Industriële technologie

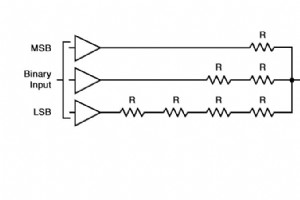

Het R/2R DAC-circuit is een alternatief voor de binary-weighted-input (R/2nR) DAC die minder unieke weerstandswaarden gebruikt. R/2R DAC versus R/2nR DAC Een nadeel van het voormalige DAC-ontwerp was de vereiste van verschillende nauwkeurige ingangsweerstandswaarden:één unieke waarde per binaire i

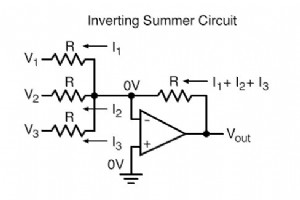

Wat is een R/2nR DAC-circuit? Het R/2nR DAC-circuit, ook wel bekend als de binary-weighted-input DAC is een variatie op het inverterende op-amp-circuit. (Merk op dat optel-circuits soms ook zomer-circuits worden genoemd.) Als u zich herinnert, is het klassieke inverterende sommeringscircuit een op

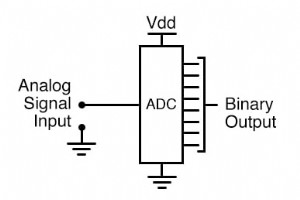

Het aansluiten van digitale circuits op sensorapparaten is eenvoudig als de sensorapparaten zelf inherent digitaal zijn. Schakelaars, relais en encoders kunnen eenvoudig worden gekoppeld aan poortcircuits vanwege de aan/uit-aard van hun signalen. Als er echter analoge apparaten bij betrokken zijn,

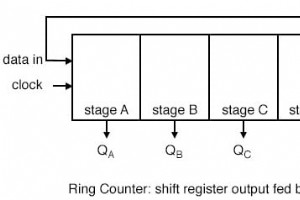

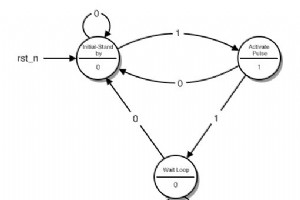

Als de uitgang van een schuifregister wordt teruggekoppeld naar de ingang. een ringteller resulteert. Het datapatroon in het schuifregister zal recirculeren zolang klokpulsen worden toegepast. Het gegevenspatroon herhaalt zich bijvoorbeeld elke vier klokpulsen in de onderstaande afbeelding. We moet

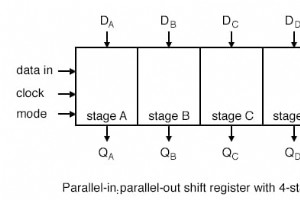

Het doel van het parallel-in/parallel-uit schuifregister is om parallelle gegevens op te nemen, te verschuiven en vervolgens uit te voeren zoals hieronder weergegeven. Een universeel schuifregister is een alles-in-één apparaat naast de parallel-in/parallel-uit-functie. Hierboven passen we vi

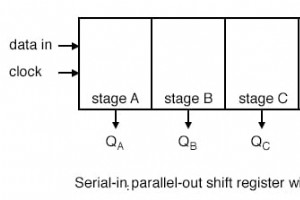

Een serieel-in, parallel-uit schuifregister is vergelijkbaar met het serieel-in, serieel-uit schuifregister doordat het gegevens naar interne opslagelementen verschuift en gegevens naar de seriële-uit, data-uit, pin verschuift. Het is anders omdat het alle interne trappen beschikbaar maakt als uitg

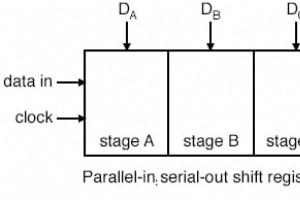

Parallel-in/serieel-uit schuifregisters doen alles wat de vorige serieel-in/serieel-uit schuifregisters doen, plus invoergegevens naar alle fasen tegelijk. Het parallel-in/seriële-uit schuifregister slaat gegevens op, verschuift deze klok voor klok en vertraagt deze met het aantal stappen maal de

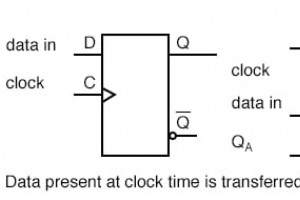

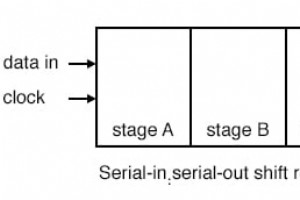

Serieel-in, serieel-uit schuifregisters vertragen de gegevens met één kloktijd voor elke fase. Ze slaan een beetje gegevens op voor elk register. Een serieel-in, serieel-uit schuifregister kan één tot 64 bits lang zijn, langer als registers of pakketten in cascade worden geschakeld. Hieronder ziet

Schuifregisters zijn, net als tellers, een vorm van sequentiële logica . Sequentiële logica wordt, in tegenstelling tot combinatorische logica, niet alleen beïnvloed door de huidige invoer, maar ook door de voorgeschiedenis. Met andere woorden, sequentiële logica onthoudt gebeurtenissen uit het ve

Tot nu toe was elk circuit dat werd gepresenteerd een combinatie stroomkring. Dat betekent dat de output alleen afhankelijk is van de huidige inputs. Eerdere inputs voor dat type circuits hebben geen effect op de output. Er zijn echter veel toepassingen waarbij onze circuits geheugen moeten hebben;

Onvolledig

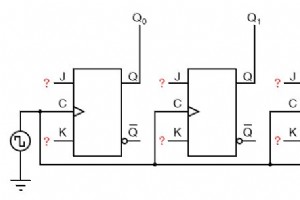

Wat is een Synchroon Teller? Een synchrone teller , in tegenstelling tot een asynchrone teller , is er een waarvan de uitvoerbits tegelijkertijd van status veranderen, zonder rimpel. De enige manier waarop we zon tegenschakeling van J-K-flip-flops kunnen bouwen, is door alle klokingangen met elka

In het vorige gedeelte zagen we een circuit met één JK-flip-flop die achteruit telde in een binaire reeks van twee bits, van 11 tot 10 tot 01 tot 00. Aangezien het wenselijk zou zijn om een circuit te hebben dat vooruit kan tellen en niet alleen achteruit, het zou de moeite waard zijn om een vo

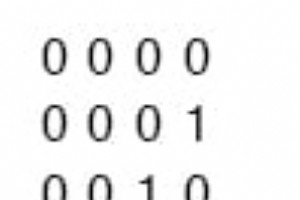

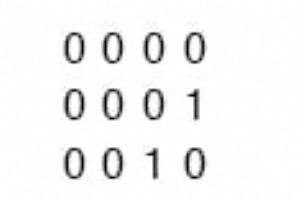

Als we een vier-bits binaire telreeks van 0000 tot 1111 onderzoeken, zal een duidelijk patroon duidelijk worden in de oscillaties van de bits tussen 0 en 1: Merk op hoe de minst significante bit (LSB) wisselt tussen 0 en 1 voor elke stap in de telreeks, terwijl elke volgende bit wisselt met de he

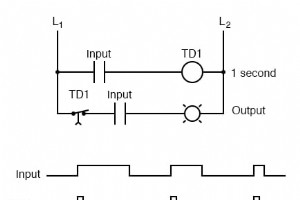

We hebben al een voorbeeld gezien van een monostabiele multivibrator die in gebruik is:de pulsdetector die wordt gebruikt in het circuit van flip-flops, om het vergrendelingsgedeelte voor een korte tijd in te schakelen wanneer het klokingangssignaal overgaat van laag naar hoog of van hoog naar laag

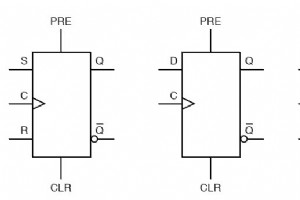

De normale data-ingangen naar een flip-flop (D, S en R, of J en K) worden synchrone ingangen genoemd omdat ze alleen in stap, of synchroon, effect hebben op de uitgangen (Q en niet-Q). het kloksignaal verandert. Deze extra ingangen die ik nu onder uw aandacht breng, worden asynchroon genoemd omdat

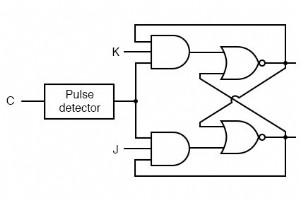

Een andere variatie op een thema van bistabiele multivibrators is de JK-flip-flop. In wezen is dit een aangepaste versie van een SR-flip-flop zonder ongeldige of illegale uitvoerstatus. Kijk goed naar het volgende diagram om te zien hoe dit wordt bereikt: De J- en K-ingangen Wat vroeger de S-

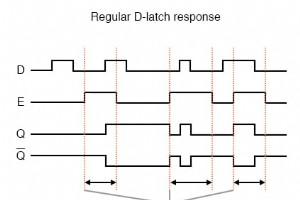

Tot nu toe hebben we zowel S-R- als D-latch-circuits bestudeerd met enable-ingangen. De grendel reageert alleen op de data-ingangen (S-R of D) als de vrijgave-ingang is geactiveerd. In veel digitale toepassingen is het echter wenselijk om het reactievermogen van een vergrendelingscircuit te beperken

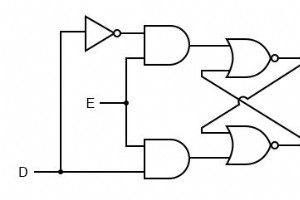

Omdat de activeringsingang op een gated SR-latch een manier biedt om de Q- en niet-Q-uitgangen te vergrendelen zonder rekening te houden met de status van S of R, kunnen we een van die ingangen elimineren om een multivibrator-vergrendelingscircuit te creëren zonder illegale invoer staten. Zon cir

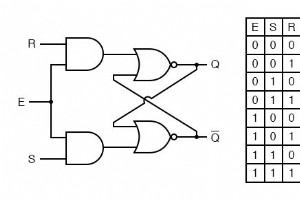

Het is soms handig in logische circuits om een multivibrator te hebben die alleen van status verandert als aan bepaalde voorwaarden wordt voldaan, ongeacht de S- en R-ingangsstatussen. De voorwaardelijke invoer heet de enable , en wordt gesymboliseerd door de letter E. Bestudeer het volgende voor

Industriële technologie