Universele schuifregisters:parallel-in, parallel-uit

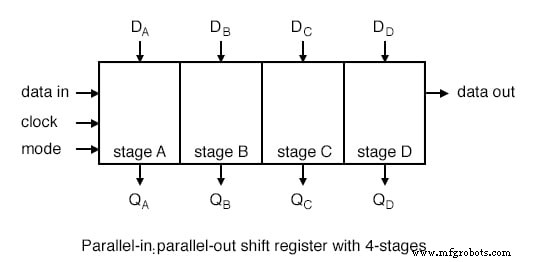

Het doel van het parallel-in/parallel-uit schuifregister is om parallelle gegevens op te nemen, te verschuiven en vervolgens uit te voeren zoals hieronder weergegeven.

Een universeel schuifregister is een alles-in-één apparaat naast de parallel-in/parallel-uit-functie.

Hierboven passen we vier bits gegevens toe op een parallel-in/parallel-uit schuifregister op DA DB DC DD . De modusregeling, die meerdere ingangen kan zijn, regelt parallel laden versus schakelen.

De modusregeling kan ook de richting van het schakelen in sommige echte apparaten regelen. De gegevens worden één bitpositie verschoven voor elke klokpuls.

De verschoven gegevens zijn beschikbaar bij de uitgangen QA QB QC QD . De "data in" en "data out" zijn bedoeld om meerdere fasen te laten lopen.

Hoewel we hierboven alleen gegevens kunnen cascaderen voor rechtsverschuiving. We kunnen trapsgewijze gegevens voor linksverschuiving opvangen door een paar linkse wijzende signalen, "data in" en "data uit", hierboven toe te voegen.

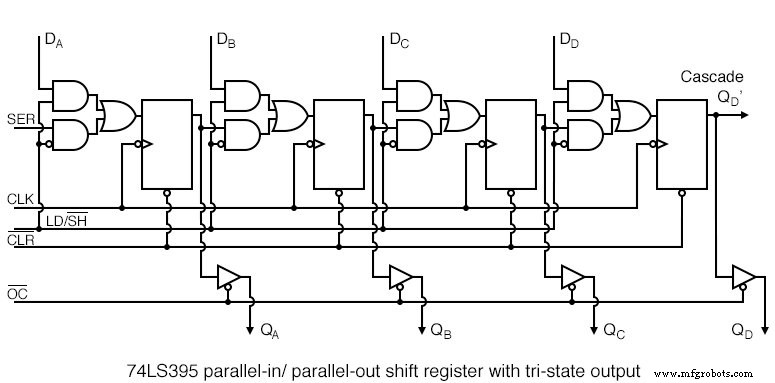

De interne details van een naar rechts verschuivend parallel-in/parallel-uit schuifregister worden hieronder getoond.

De tri-state buffers zijn niet strikt noodzakelijk voor het parallel-in/parallel-out schuifregister, maar maken deel uit van het real-world apparaat dat hieronder wordt getoond.

De 74LS395 komt zo nauw overeen met ons concept van een hypothetisch naar rechts verschuivend parallel-in/parallel-uit schuifregister dat we een te vereenvoudigde versie van de bovenstaande gegevensbladdetails gebruiken.

Zie de link naar het volledige gegevensblad voor meer details, verderop in dit hoofdstuk.

LD/SH' bestuurt de AND-OR-multiplexer bij de gegevensinvoer naar de FF's. Als LD/SH'=1 , de bovenste vier EN-poorten zijn ingeschakeld, waardoor parallelle ingangen DA . kunnen worden toegepast DB DC DD naar de vier FF-gegevensingangen.

Let op de inverterbel op de klokingang van de vier FF's. Dit geeft aan dat de 74LS395 gegevens klokt op de negatief lopende klok, wat de overgang van hoog naar laag is.

De vier databits worden parallel geklokt vanaf DA DB DC DD naar QA QB QC QD op de volgende negatief lopende klok. In dit "echte deel", OC' moet laag zijn als de gegevens beschikbaar moeten zijn op de eigenlijke uitgangspinnen in plaats van alleen op de interne FF's.

De eerder geladen gegevens kunnen één bitpositie naar rechts worden verschoven als LD/SH'=0 voor de volgende negatief lopende klokflanken.

Vier klokken zouden de gegevens volledig uit ons 4-bit schuifregister verschuiven. De gegevens zouden verloren gaan tenzij ons apparaat werd gecascadeerd van QD ’ naar SER van een ander apparaat.

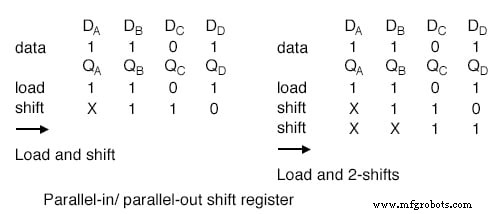

Hierboven wordt een gegevenspatroon gepresenteerd aan invoer DA DB DC DD . Het patroon wordt geladen naar QA QB QC QD . Daarna wordt het een beetje naar rechts verschoven.

De binnenkomende gegevens worden aangegeven met X , wat betekent dat we niet weten wat het is. Als de invoer (SER ) waren geaard, we zouden bijvoorbeeld weten welke gegevens (0 ) is naar binnen geschoven.

Ook getoond, is naar rechts verschuiven met twee posities, waarvoor twee klokken nodig zijn.

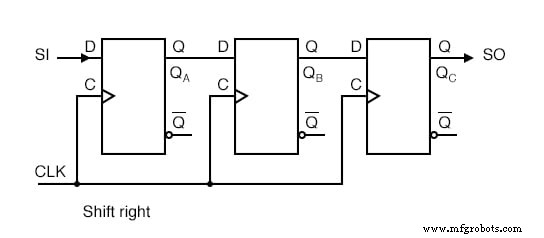

De bovenstaande afbeelding dient als referentie voor de hardware die betrokken is bij het naar rechts verschuiven van gegevens.

Het is te eenvoudig om zelfs maar met dit cijfer bezig te zijn, behalve om te vergelijken met meer complexe cijfers om te volgen.

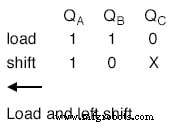

Rechts verschuiven van gegevens wordt hierboven gegeven ter referentie naar de vorige rechter verschuiver.

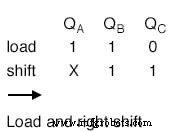

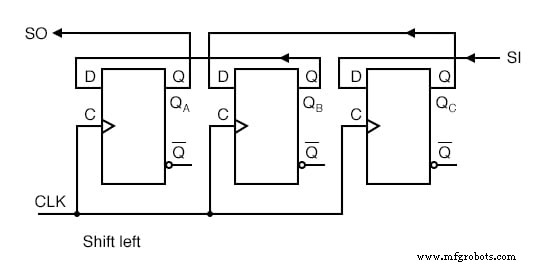

Als we naar links moeten schuiven, moeten de FF's opnieuw worden bedraad. Vergelijk met de vorige rechter shifter. Ook SI en ZO zijn teruggedraaid. SI verschuift naar QC . QC verschuift naar QB . QB verschuift naar QA . VA vertrekt op de SO verbinding, waar het naar een andere shifter kan lopen SI . Deze linker schakelvolgorde is achteruit vanaf de rechter schakelvolgorde.

Hierboven schuiven we hetzelfde gegevenspatroon één bit naar links.

Er is één probleem met de bovenstaande afbeelding "naar links verplaatsen". Er is geen markt voor. Niemand maakt een shift-left onderdeel.

Een "echt apparaat" dat de ene richting verschuift, kan extern worden bedraad om de andere richting te verschuiven. Of moeten we zeggen dat er geen links of rechts is in de context van een apparaat dat maar in één richting verschuift.

Er is echter een markt voor een apparaat dat op commando door een stuurlijn naar links of rechts verschuift. Links en rechts zijn natuurlijk geldig in die context.

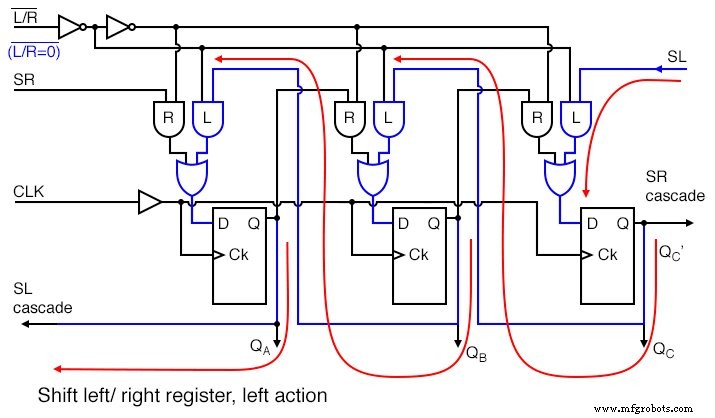

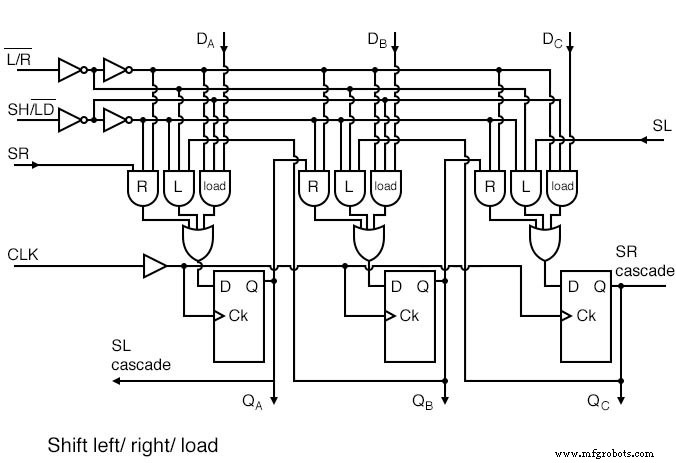

Wat we hierboven hebben, is een hypothetisch schuifregister dat in staat is om beide richtingen te verschuiven onder de controle van L'/R .

Het is ingesteld met L’/R=1 om de normale richting te verschuiven, naar rechts. L’/R=1 activeert de multiplexer EN-poorten met het label R .

Hierdoor kunnen gegevens het pad volgen dat wordt geïllustreerd door de pijlen, wanneer een klok wordt toegepast. Het verbindingspad is hetzelfde als de "te simpele" "shift right" figuur hierboven.

Gegevens komen binnen bij SR , naar QA , naar QB , naar QC , waar het vertrekt bij SR cascade . Deze pin kan SR . aansturen van een ander apparaat aan de rechterkant.

Wat als we L’/R . veranderen naar L’/R=0 ?

Met L’/R=0 , de multiplexer EN-poorten met het label L zijn ingeschakeld, wat een pad oplevert, weergegeven door de pijlen, hetzelfde als de bovenstaande afbeelding voor "naar links verplaatsen".

Gegevens komen binnen op SL , naar QC , naar QB , naar QA , waar het vertrekt bij SL cascade . Deze pin kan SL drive aansturen van een ander apparaat aan de linkerkant.

De belangrijkste deugd van de bovenstaande twee figuren die het "schuif naar links/rechts register" illustreren, is eenvoud.

De werking van de linker-rechts-bediening L’/R=0 is gemakkelijk te volgen. Een commercieel gedeelte heeft de parallelle gegevensbelasting nodig die wordt geïmpliceerd door de titel van de sectie. Dit wordt weergegeven in de onderstaande afbeelding.

Nu we zowel naar links als naar rechts kunnen schuiven via L’/R , laten we SH/LD' . toevoegen , shift/load en de AND-poorten met het label "load" om te voorzien in parallel laden van gegevens van invoer DA DB DC .

Wanneer SH/LD'=0 , EN-poorten R en L zijn uitgeschakeld, EN-poorten "laden" zijn ingeschakeld om gegevens door te geven DA DB DC naar de FF-gegevensingangen. de volgende klok CLK klokt de gegevens naar QA QB QC .

Zolang dezelfde gegevens aanwezig zijn, worden deze opnieuw geladen op volgende klokken. Gegevens die voor slechts één klok aanwezig zijn, gaan echter verloren van de uitgangen wanneer deze niet langer aanwezig zijn op de gegevensingangen.

Een oplossing is om de gegevens op één klok te laden en vervolgens op de volgende vier klokken te verschuiven. Dit probleem wordt in de 74ALS299 verholpen door een andere AND-poort aan de multiplexer toe te voegen.

Als SH/LD' is gewijzigd in SH/LD'=1 , zijn de EN-poorten met het label "load" uitgeschakeld, waardoor de linker/rechter controle L'/R om de richting van de verschuiving op de L . in te stellen of R EN poorten. Schakelen is zoals in de vorige figuren.

Het enige dat nodig is om een levensvatbaar geïntegreerd apparaat te produceren, is om de vierde EN-poort aan de multiplexer toe te voegen, zoals bedoeld voor de 74ALS299.

Dit wordt getoond in de volgende sectie voor dat onderdeel.

Parallel-in/parallel-out en universele apparaten

Laten we eens nader kijken naar Serial-in/parallel-out schuifregisters die beschikbaar zijn als geïntegreerde schakelingen, met dank aan Texas Instruments.

Volg de links voor volledige apparaatgegevensbladen.

-

SN74LS395A parallel-in/parallel-uit 4-bit schuifregister

-

SN74ALS299 parallel-in/parallel-uit 8-bit universeel schuifregister

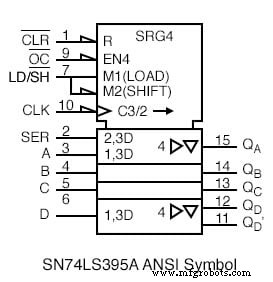

We hebben al gekeken naar de interne details van de SN74LS395A, zie bovenstaande figuur, 74LS395 parallel-in/parallel-out schuifregister met tri-state output.

Direct erboven staat het ANSI-symbool voor de 74LS395.

Waarom alleen 4-bits, zoals aangegeven door SRG4 boven? Het hebben van zowel parallelle ingangen als parallelle uitgangen, naast de besturings- en voedingspinnen, staat niet meer I/O (Input/Output) bits toe in een 16-pins DIP (Dual Inline Package).

R geeft aan dat de schuifregistertrappen worden gereset door invoer CLR' (actieve laag-inverterende halve pijl bij ingang) van het bedieningsgedeelte bovenaan het symbool. OC' , indien laag, (pijl weer omkeren) wordt (EN4) ingeschakeld ) de vier tristate uitgangsbuffers (QA QB QC QD ) in de gegevenssectie.

Laden/verschuiving' (LD/SH' ) op pin (7) komt overeen met internals M1 (laden) en M2 (verschuiving). Zoek naar voorvoegsels van 1 en 2 in de rest van het symbool om na te gaan wat hierdoor wordt bestuurd.

De negatieve flankgevoelige klok (aangegeven door de omgekeerde pijl op pin-10) C3/2 heeft twee functies.

Eerst de 3 van C3/2 beïnvloedt elke invoer met een voorvoegsel van 3 , zeg 2,3D of 1,3D in de gegevenssectie.

Dit zou parallelle belasting zijn bij A, B, C, D toegeschreven aan M1 en C3 voor 1,3D . Ten tweede, 2 van C3/2 -pijl naar rechts geeft aan dat gegevens worden geklokt waar 2 verschijnt in een voorvoegsel (2,3D bij pin-2).

We hebben dus het klokken van gegevens bij SER in QA met modus 2 . De pijl naar rechts na C3/2 rekeningen voor verschuiving in interne schuifregisterstadia QA QB QC QD .

De naar rechts wijzende driehoeken geven buffering aan; de omgekeerde driehoek geeft drie toestanden aan, bestuurd door de EN4 .

Let op, alle 4 s in het symbool dat hoort bij de EN worden vaak weggelaten. Stadia QB QC worden geacht dezelfde kenmerken te hebben als QD . QD ’ cascades naar de SER . van het volgende pakket naar rechts.

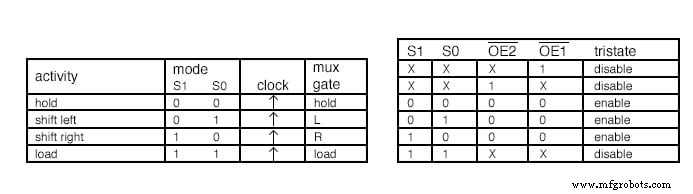

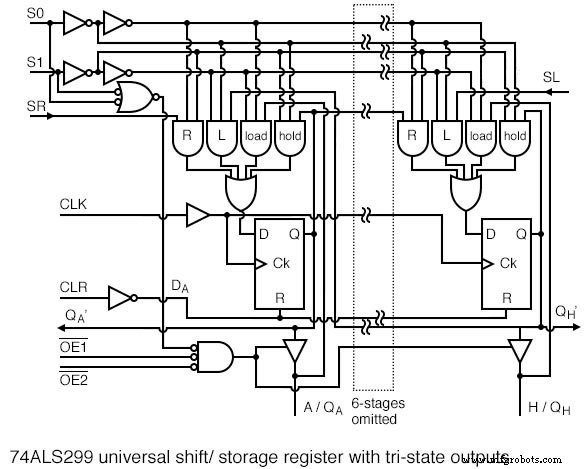

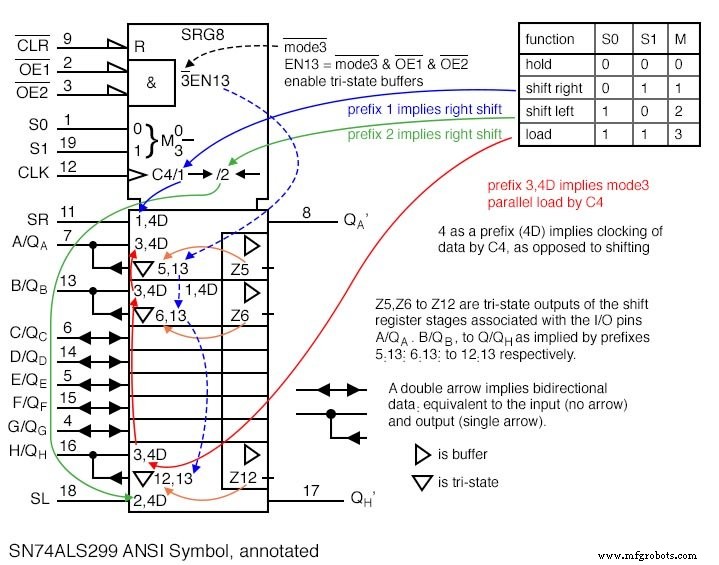

De bovenstaande tabel, gecomprimeerd uit het gegevensblad '299', vat de werking van het universele schuif-/opslagregister 74ALS299 samen.

Volg de '299-link hierboven voor volledige details. De multiplexerpoorten R , L , laden werken zoals in de vorige "shift links/rechts register" cijfers.

Het verschil is dat de modus S1 . invoert en S0 selecteer shift left, shift right en load met modus ingesteld op S1 S0 = tot 01 , 10 , en 11 respectievelijk zoals weergegeven in de tabel, waardoor multiplexerpoorten L , R , en laden respectievelijk.

Zie tafel. Een klein verschil is het parallelle belastingspad van de driestandenuitgangen. Eigenlijk zijn de tri-state buffers (moeten) uitgeschakeld worden door S1 S0 =11 om de I/O bus te laten zweven voor gebruik als invoer.

Een bus is een verzameling van soortgelijke signalen. De invoer wordt toegepast op A , B via H (dezelfde pinnen als QA , QB , via QH ) en doorgestuurd naar de load poort in de multiplexers, en op de D ingangen van de FF's. Gegevens worden parallel geladen op een klokpuls.

De enige nieuwe multiplexerpoort is de EN-poort met het label hold , mogelijk gemaakt door S1 S0 =00 . De vasthouden poort maakt een pad mogelijk vanaf de Q uitvoer van de FF terug naar de hold gate, naar de D-ingang van dezelfde FF. Het resultaat is dat met modus S1 S0 =00 , wordt de uitgang continu opnieuw geladen bij elke nieuwe klokpuls. Zo worden gegevens bewaard. Dit is samengevat in de tabel.

Gegevens lezen van uitgangen QA , QB , via QH , de tri-state buffers moeten zijn ingeschakeld door OE2', OE1' =00 en modus =S1 S0 =00, 01 of 10 .

Dat wil zeggen, modus is alles behalve laden . Zie tweede tabel.

Rechts verschuift gegevens van een pakket naar links, verschuift naar de SR invoer. Alle gegevens verschoven naar rechts vanaf fase QH trapsgewijs naar rechts via QH ’.

Deze output wordt niet beïnvloed door de tri-state buffers. De shift-rechts-reeks voor S1 S0 =10 is:

SR> VA> QB> QC> VD> QE> QF> QG> QH (QH ’)

Links verschuift gegevens van een pakket naar rechts verschuift binnen op de SL invoer. Alle gegevens verschoven naar links vanaf fase QA trapsgewijs naar links via QA ', ook niet beïnvloed door de tri-state buffers. De volgorde van verschuiving naar links voor S1 S0 =01 is:

(VA ’) VA

Het schakelen kan plaatsvinden met de tri-state buffers uitgeschakeld door een van OE2' of OE1' =1 . De uitgangen van de registerinhoud zijn echter niet toegankelijk. Zie tabel.

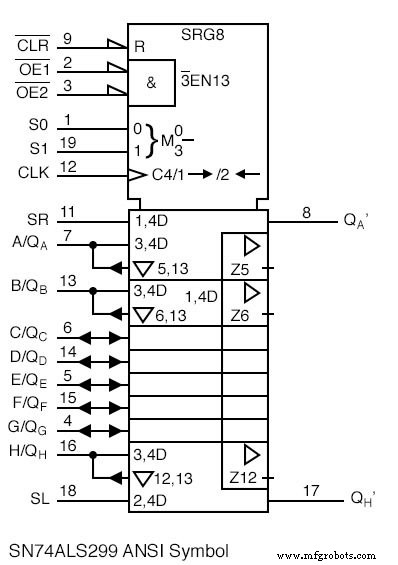

Het "schone" ANSI-symbool voor het SN74ALS299 parallel-in/parallel-out 8-bits universeel schuifregister met tri-state output wordt hierboven ter referentie getoond.

De geannoteerde versie van het ANSI-symbool wordt getoond om de daarin vervatte terminologie te verduidelijken.

Merk op dat de ANSI-modus (S0 S1) is omgekeerd van de volgorde (S1 S0) die in de vorige tabel werd gebruikt.

Dat keert de decimale modusnummers (1 &2) om. In ieder geval zijn we het volledig eens met het officiële gegevensblad en kopiëren we deze inconsistentie.

Praktische toepassingen

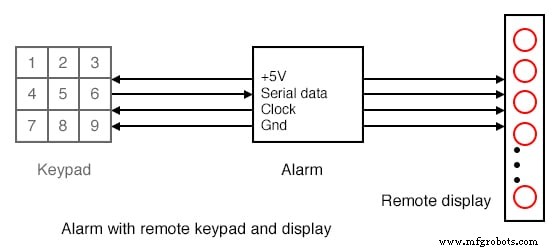

Het blokschema Alarm met afstandsbediening wordt hieronder herhaald. Voorheen bouwden we de toetsenbordlezer en het externe display als afzonderlijke eenheden.

Nu zullen we zowel het toetsenbord als het display combineren in een enkele eenheid met behulp van een universeel schuifregister.

Hoewel afzonderlijk in het diagram, bevinden het toetsenbord en de display zich beide in dezelfde externe behuizing.

We zullen de toetsenbordgegevens parallel in het schuifregister laden met een enkele klokpuls en deze vervolgens naar de hoofdalarmbox verplaatsen.

Tegelijkertijd verschuiven we de LED-gegevens van het hoofdalarm naar het externe schakelregister om de LED's te verlichten.

We zullen tegelijkertijd toetsenbordgegevens en LED-gegevens naar het schuifregister schuiven.

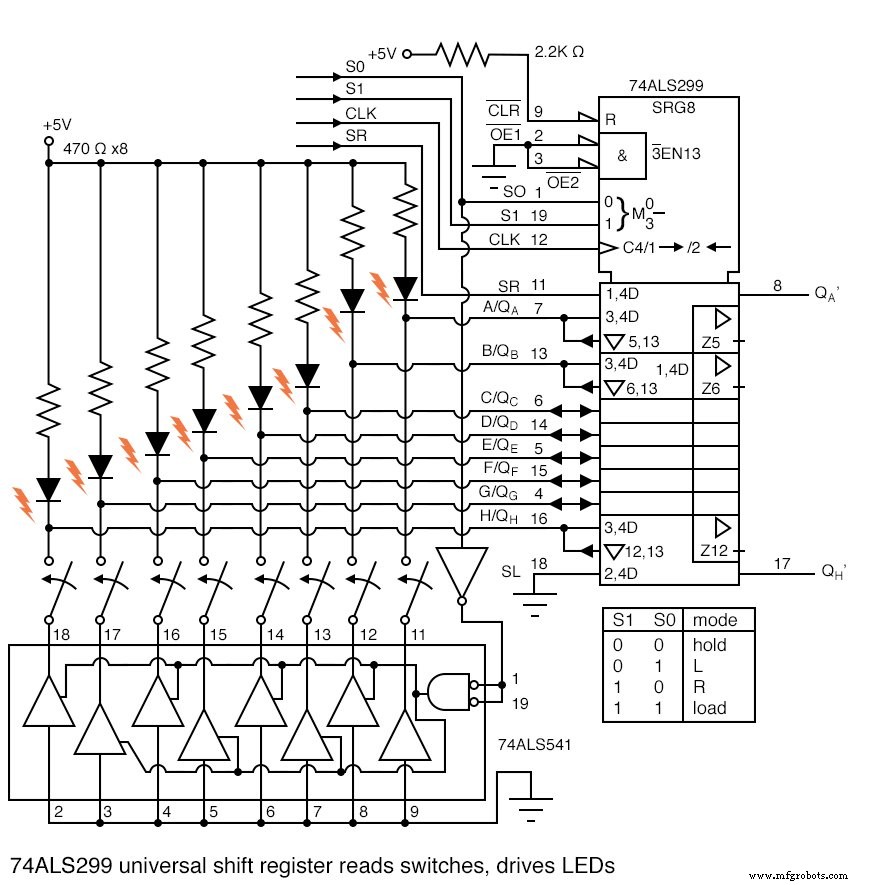

Acht LED's en stroombeperkende weerstanden zijn aangesloten op de acht I/O-pinnen van het universele schuifregister 74ALS299.

De LEDS kan alleen worden aangestuurd tijdens Mode 3 met S1=0 S0=0 . De OE1' en OE2' tristate-inschakelingen zijn geaard om de tristate-uitgangen permanent in te schakelen tijdens modi 0, 1, 2 .

Hierdoor gaan de LEDS branden (flikkeren) tijdens het schakelen. Als dit een probleem zou zijn, de EN1 ’ en EN2’ kan ongeaard zijn en parallel lopen met S1 en S0 respectievelijk om alleen de tristate-buffers in te schakelen en de LEDS te laten branden tijdens het vasthouden, modus 3 . Laten we het voor dit voorbeeld simpel houden.

Tijdens parallel laden, S0=1 omgekeerd naar een 0, kunnen de octale tristate-buffers de schakelaarwissers aarden.

De bovenste, open, schakelcontacten worden logisch hoog getrokken door de weerstand-LED-combinatie op de acht ingangen.

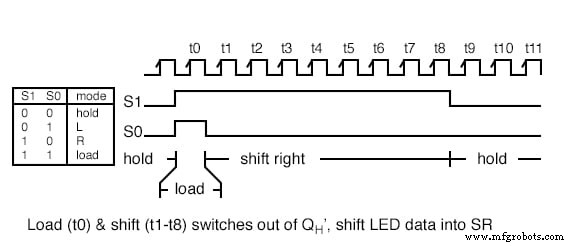

Elke sluiting van een schakelaar zal de ingang laag kortsluiten. We laden de schakelgegevens parallel in de '299 op klok t0 wanneer beide S0 en S1 zijn hoog. Zie golfvormen hieronder.

Eenmaal S0 gaat laag, acht klokken (t0 naart8 ) schakelgegevens voor het sluiten van de schakelaar uit de '299 via de Qh ’ pinnen.

Tegelijkertijd worden nieuwe LED-gegevens verschoven bij SR van de 299 door dezelfde acht klokken. De LED-gegevens vervangen de sluitingsgegevens van de schakelaar naarmate het schakelen vordert.

Na de 8e ploegklok, t8 , S1 gaat laag naar opbrengsthoudmodus (S1 S0 =00 ). De gegevens in het schuifregister blijven hetzelfde, zelfs als er meer klokken zijn, bijvoorbeeld T9 , t10 , enz.

Waar komen de golfvormen vandaan? Ze zouden kunnen worden gegenereerd door een microprocessor als de kloksnelheid niet hoger was dan 100 kHz. In dat geval zou het onhandig zijn om klokken te genereren na t8 .

Als de klok in het megahertz-bereik was, zou de klok continu lopen. De klok, S1 en S0 zou worden gegenereerd door digitale logica, hier niet weergegeven.

GERELATEERDE WERKBLAD:

- Werkblad Ploegregisters

Industriële technologie