Inleiding tot Shift Registers

Schuifregisters zijn, net als tellers, een vorm van sequentiële logica .

Sequentiële logica wordt, in tegenstelling tot combinatorische logica, niet alleen beïnvloed door de huidige invoer, maar ook door de voorgeschiedenis.

Met andere woorden, sequentiële logica onthoudt gebeurtenissen uit het verleden.

Schuifregisters produceren een discrete vertraging van een digitaal signaal of golfvorm.

Een golfvorm gesynchroniseerd met een klok , een zich herhalende blokgolf, wordt vertraagd door “n” discrete kloktijden, waarbij “n” is het aantal schuifregistertrappen.

Dus een viertraps schuifregister vertraagt “data in” met vier klokken naar “data out”.

De stadia in een schuifregister zijn vertragingsstadia , typ meestal “D” Teenslippers of typ “JK” Teenslippers.

Vroeger dienden zeer lange (enkele honderden trappen) schuifregisters als digitaal geheugen.

Deze verouderde applicatie doet denken aan de akoestische kwikvertragingslijnen die werden gebruikt als vroeg computergeheugen.

Seriële datatransmissie, over een afstand van meters tot kilometers, maakt gebruik van schuifregisters om parallelle data om te zetten in seriële vorm.

Seriële datacommunicatie vervangt veel langzame parallelle datakabels door een enkel serieel hogesnelheidscircuit.

Seriële gegevens over kortere afstanden van tientallen centimeters, gebruiken schuifregisters om gegevens in en uit microprocessors te krijgen.

Talloze randapparatuur, waaronder analoog-naar-digitaal-omzetters, digitaal-naar-analoog-omzetters, beeldschermstuurprogramma's en geheugen, gebruiken schuifregisters om de hoeveelheid bedrading in printplaten te verminderen.

Sommige gespecialiseerde tellercircuits gebruiken eigenlijk schuifregisters om herhalende golfvormen te genereren.

Langere schuifregisters, met behulp van feedback, genereren patronen die zo lang zijn dat ze op willekeurige ruis lijken, pseudo-ruis .

Basis schuifregisters zijn ingedeeld volgens structuur volgens de volgende typen:

- Serial-in/serial-out

- Parallel-in/serial-out

- Serial-in/parallel-out

- Universele parallel-in/parallel-out

- Bellenteller

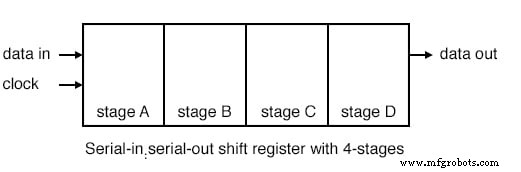

Hierboven laten we een blokschema zien van een serieel-in/seriële-uit schuifregister, dat 4 fasen lang is.

Gegevens aan de ingang worden met vier klokperioden vertraagd vanaf de ingang naar de uitgang van het schuifregister.

Gegevens bij "data in", hierboven, zullen aanwezig zijn in de fase A uitgang na de eerste klokpuls. Na de tweede pulsfase A gegevens worden overgebracht naar fase B output, en “data in” wordt overgebracht naar fase A uitvoer. Na de derde klok, etappe C wordt vervangen door fase B; stadium B wordt vervangen door fase A; en fase A wordt vervangen door "data in".

Na de vierde klok zijn de gegevens die oorspronkelijk aanwezig waren bij "data in" in stadium D , "uitvoer".

De 'first in'-gegevens zijn 'first out' omdat deze worden verschoven van 'data in' naar 'data out'.

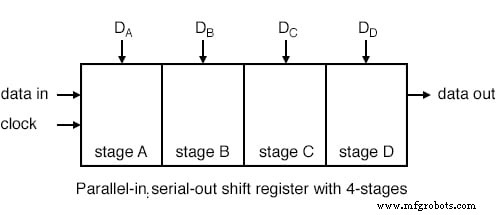

Gegevens worden in alle fasen tegelijk geladen van een parallel-in/seriële-uit schuifregister.

De gegevens worden vervolgens via "data out" door klokpulsen naar buiten verschoven. Aangezien hierboven een 4-traps schuifregister wordt getoond, zijn vier klokpulsen nodig om alle gegevens eruit te schuiven.

In het bovenstaande diagram, stadium D data zal aanwezig zijn bij de “data out” tot de eerste klokpuls; stadium C gegevens zullen aanwezig zijn bij "data out" tussen de eerste klok en de tweede klokpuls; stadium B gegevens zullen aanwezig zijn tussen de tweede klok en de derde klok; en podium A gegevens zullen aanwezig zijn tussen de derde en de vierde klok.

Na de vierde klokpuls en daarna moeten opeenvolgende bits "data in" verschijnen bij "data uit" van het schuifregister na een vertraging van vier klokpulsen.

Als er vier schakelaars waren aangesloten op DA via DD , kan de status worden ingelezen in een microprocessor met slechts één datapin en een klokpin.

Aangezien het toevoegen van meer schakelaars geen extra pinnen vereist, ziet deze benadering er aantrekkelijk uit voor veel ingangen.

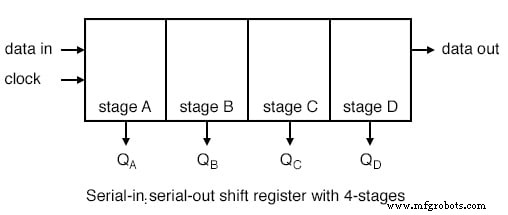

Hierboven worden vier databits verschoven van "data in" met vier klokpulsen en zijn beschikbaar op QA via QD voor het aansturen van externe circuits zoals LED's, lampen, relaisdrivers en hoorns. Na de eerste klok verschijnen de gegevens bij "data in" bij QA .

Na de tweede klok, De oude QA gegevens verschijnen op QB; QA ontvangt volgende data van “data in”. Na de derde klok, QB gegevens zijn op QC .

Na de vierde klok, QC gegevens zijn op QD . Deze fase bevat de gegevens die als eerste aanwezig zijn bij “data in”. Het schuifregister zou nu vier databits moeten bevatten.

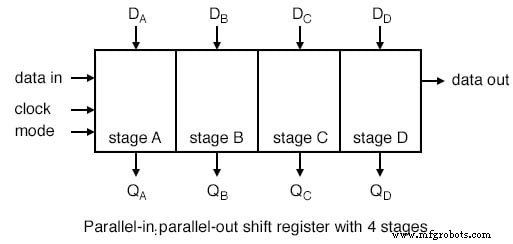

Een parallel-in/parallel-uit schuifregister combineert de functie van het parallel-in, serieel-uit schuifregister met de functie van het serieel-in, parallel-uit schuifregister om het universele schuifregister te verkrijgen.

De "doe alles" shifter heeft een prijs - het grotere aantal I/O (Input/Output) pinnen kan het aantal fasen dat kan worden verpakt verminderen.

Gegevens gepresenteerd op DA via DD wordt parallel in de registers geladen.

Deze gegevens op QA via QD kan worden verschoven door het aantal pulsen dat wordt aangeboden aan de klokingang.

De verschoven gegevens zijn beschikbaar op QA via QD .

De "mode"-ingang, die meer dan één ingang kan zijn, regelt het parallel laden van gegevens van DA via DD , verschuiving van gegevens en de richting van verschuiving.

Er zijn schuifregisters die gegevens naar links of naar rechts verschuiven.

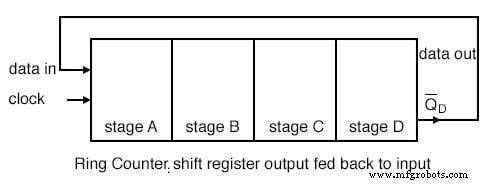

Als de seriële uitgang van een schuifregister is aangesloten op de seriële ingang, kunnen gegevens continu rond de ring worden verschoven zolang er klokpulsen aanwezig zijn.

Als de uitvoer wordt omgekeerd voordat deze wordt teruggekoppeld, zoals hierboven weergegeven, hoeven we ons geen zorgen te maken over het laden van de initiële gegevens in de "ringteller".

GERELATEERDE WERKBLAD:

- Werkblad Ploegenregister

Industriële technologie

- Inleiding tot DC-circuits

- Inleiding tot AC-circuits

- Inleiding tot discrete halfgeleidercircuits

- Inleiding tot analoge geïntegreerde schakelingen

- Inleiding tot SPICE

- Netwerkprotocollen

- Microprocessors

- Op-Amp-gegevens

- Een inleiding tot edge computing en voorbeelden van use-cases

- Inleiding tot harmonischen:deel 1

- Wat is IIoT?