Ultra-lage specifieke weerstand laterale dubbel-diffuus metaaloxide-halfgeleidertransistor met verbeterde dubbele poort en gedeeltelijk P-begraven laag

Abstract

Een ultra-lage specifieke aan-weerstand (R op,sp ) laterale dubbel gediffundeerde metaaloxide-halfgeleidertransistor (LDMOS) met verbeterde dual-gate en gedeeltelijk P-begraven laag wordt in dit artikel voorgesteld en onderzocht. Het analytische model op weerstand voor de voorgestelde LDMOS is gebouwd om een diepgaand inzicht te verschaffen in de relatie tussen de weerstand van het driftgebied en de weerstand van het kanaalgebied. N-begraven laag wordt geïntroduceerd onder P-put om een geleidingspad met lage weerstand te bieden en de weerstand van het kanaalgebied aanzienlijk te verminderen. Verbeterde dual-gate-structuur wordt gevormd door een N-begraven laag, terwijl de verticale doorslag in de off-state wordt vermeden. Gedeeltelijke P-begraven laag met geoptimaliseerde lengte wordt aangenomen onder het N-driftgebied om het verticale uitputtingsgebied uit te breiden en de elektrische veldpiek in off-state te ontspannen, wat de doorslagspanning (BV) verbetert met een lage weerstand van het driftgebied. Voor de LDMOS met verbeterde dual-gate en gedeeltelijk P-begraven laag, laat het resultaat zien dat R op,sp is 8,5 mΩ·mm 2 terwijl BV 43 V is.

Achtergrond

Met de toename van de vraag naar complexere en snellere logische functies in analoge vermogens-IC's, is het belangrijk om de prestaties van de laterale dubbel gediffundeerde metaaloxide-halfgeleidertransistor (LDMOS) te verbeteren, waarbij met name de specifieke aan-weerstand wordt geminimaliseerd ( R op,sp ) en het maximaliseren van off-state doorslagspanning (BV) [1,2,3,4,5,6,7,8,9]. De meeste ontwikkelde technologieën zijn gericht op het optimaliseren van het driftgebied om de wisselwerking tussen R . te verbeteren op,sp vs. BV voor LDMOS-apparaten [10,11,12,13,14,15,16,17,18,19,20]. In ons vorige werk werd de LDMOS met ultra-ondiepe greppelisolatie (USTI) voorgesteld [21]. De diepte en hoekhoek van USTI zijn geoptimaliseerd om de beste prestaties in hun klasse te bereiken. Voor de LDMOS met laag voltage verliest het driftgebied echter zijn dominantie in R op,sp en de bijdrage van de zenderregio kan niet worden genegeerd.

Methode

In dit werk wordt een nieuwe LDMOS met ultralage specifieke weerstand met verbeterde dual-gate en gedeeltelijk P-begraven laag onderzocht. De fysieke modellen IMPACT.I, BGN, CONMOB, FLDMOB, SRH en SRFMOB worden gebruikt in numerieke simulatie. Een analytisch model op weerstand wordt voorgesteld om een diepgaand inzicht te verschaffen in de relatie tussen de weerstand van het driftgebied en de weerstand van het kanaalgebied. Op basis van het model zijn N-begraven laag en gedeeltelijk P-begraven laag geoptimaliseerd om een lage R te bereiken op,sp en hoge BV.

Resultaten en discussie

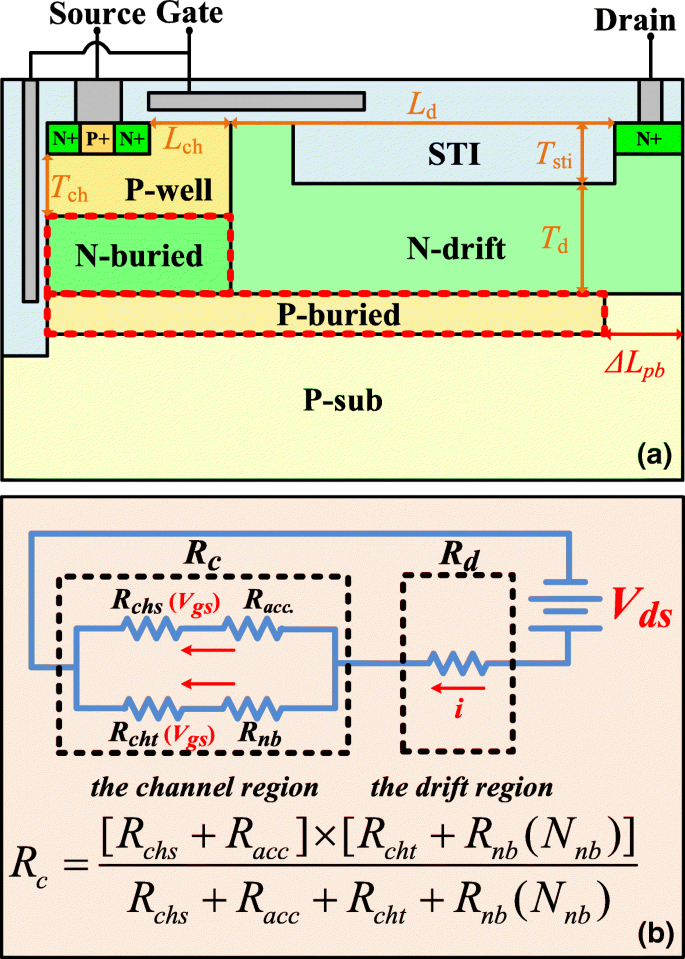

Figuur 1a toont de schematische dwarsdoorsnede van LDMOS met ultralage specifieke weerstand tegen weerstand met verbeterde dual-gate en gedeeltelijk P-begraven laag. De LDMOS heeft de dual-gate met N-begraven laag en de gedeeltelijk P-begraven laag die bijdraagt aan het verminderen van R op,sp en respectievelijk BV verbeteren. In het kanaalgebied wordt de verbeterde dubbele poort gevormd door een sleufpoort en een sterk gedoteerde N-begraven laag. In vergelijking met conventionele dual-gate-structuur, vermindert de N-begraven laag de weerstand van het kanaalgebied aanzienlijk door een geleidingspad met lage weerstand onder P-put in de aan-toestand te bieden. In het driftgebied wordt de gedeeltelijk P-begraven laag met hoge doteringsconcentratie geïntroduceerd onder het N-driftgebied om BV te verbeteren met behoud van een lage R op,sp . De gedeeltelijk P-begraven laag helpt het verticale elektrische veld in de off-state te verminderen zonder de ladingsbalans in het driftgebied te verbreken. De sleutelgrootte van het nieuwe apparaat staat in tabel 1.

een Schematische dwarsdoorsnede van LDMOS met ultralage specifieke weerstand met verbeterde dubbele poort en gedeeltelijk P-begraven laag. b Schematische equivalente aan-weerstand voor de voorgestelde LDMOS

Figuur 1b toont het schematische equivalente on-weerstandsmodel voor de voorgestelde LDMOS. De totale aan-weerstand wordt beschouwd als de weerstand van het driftgebied (R d ) en de weerstand van het kanaalgebied (R c ) in series. In het kanaalgebied loopt het geleidingspad van het oppervlaktekanaal evenwijdig aan het geleidingspad van het geulkanaal. Dus, R c is gelijk aan (R chs + R acc )//(R cht + R nb ), waarbij R chs , R acc , R cht , en R nb zijn respectievelijk de weerstanden van het oppervlaktepoortkanaal, het accumulatiegebied, het geulpoortkanaal en de N-begraven laag. Gebaseerd op het voorgestelde on-resistance-model, is de reductie van R c zou bereiken door R . te verminderen nb zonder de andere prestaties te beïnvloeden, omdat de andere weerstanden voornamelijk worden bepaald door de procestechnologie, bedrijfsspanning en drempelspanning. De R d is verminderd door een P-begraven laag onder het N-driftgebied te introduceren om het Reduce Surface-field (RESURF) -effect in ons vorige werk te verbeteren. In dit werk wordt de gedeeltelijk P-begraven laag gebruikt om de BV te verbeteren met behoud van de lage R d .

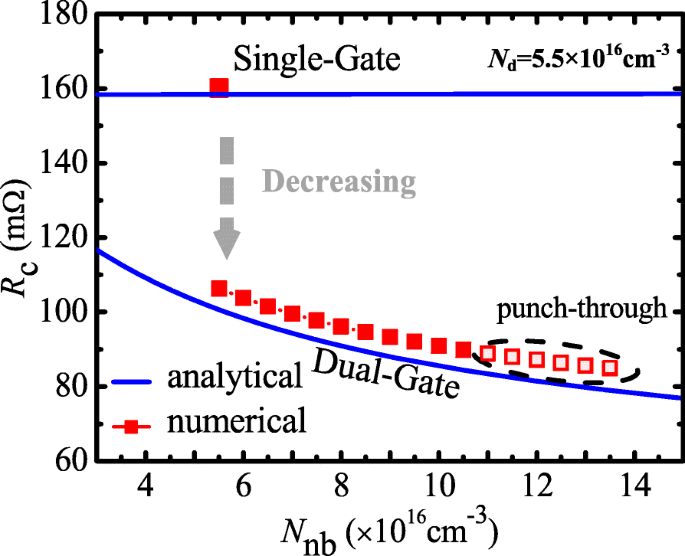

Gericht op de vermindering van R c , wordt de N-begraven laag met hoge doteringsconcentratie ingebracht onder P-well. Afbeelding 2 toont numerieke en analytische R c als functies van de doteringsconcentratie van de N-begraven laag (N nb ) met enkele poort en dubbele poort. Er wordt aangegeven dat de structuur met twee poorten helpt om R . te verminderen c vergeleken met de enkele poort. Wanneer N nb = N d = 5.5 × 10 16 cm −3 , R c bedraagt 110 mΩ. Volgens het aan-weerstandsmodel, R nb levert de belangrijkste bijdrage aan R c . En dan, de R nb is gewenst om te verminderen met als doel kleinere R c . Zoals weergegeven in Afb. 2a, R c wordt verminderd met N nb toenemend. Wanneer N nb = 1.35 × 10 17 cm −3 , R c wordt teruggebracht tot 85 mΩ. Afb. 2 laat echter ook zien dat N nb zou worden beperkt door punch-through afbraak. Vanwege het toevoegen van een loopgraafpoort, R c wordt eerst met 34% verlaagd met N nb = N d = 5.5 × 10 16 cm −3 . Als N nb neemt toe, R c voortdurend afneemt. Met geoptimaliseerde N nb = 1,05 × 10 17 cm −3 , R c wordt uiteindelijk met 45% verminderd. Wanneer N nb> 1,05 × 10 17 cm −3 , zal punch-through afbraak plaatsvinden in P-well. Het analytische resultaat van R op,sp weergegeven in Fig. 2 geeft aan dat het voorgestelde model een goede pasvorm biedt met numerieke simulatieresultaten. Daarom is het model geloofwaardig als leidraad voor het optimalisatieontwerp.

Numerieke en analytische R c als een functie van N nb met enkele poort en dubbele poort (Z = 1 cm). N d is de dopingconcentratie van het N-driftgebied

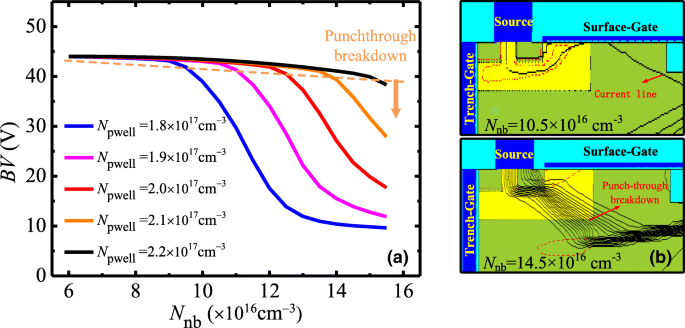

Afbeelding 3a toont numerieke BV als functie van N nb met verschillende dopingconcentraties van P-well (N pwell ). N nb heeft niet alleen effect op de R c , maar ook de BV. Voor een gegeven N pwell , BV blijft ongewijzigd op kleine N nb , en neemt dan af met N nb toenemend. Wanneer N nb neemt toe tot 1,2 × 10 17 cm −3 , BV begint te dalen met N pwell = 2 × 10 17 cm −3 . De daling van BV wordt toegeschreven aan doorslag in het P-well-gebied, zoals weergegeven in figuur 3b. Naarmate de afvoerspanning toeneemt, strekt het uitputtingsgebied in de P-put zich uit naar de bron. Wanneer het uitputtingsgebied de N+/P-putovergang aanvalt, vindt de doorslag doorslag plaats. Voor een grote N pwell , de uitputting strekt zich voornamelijk uit tot het driftgebied en de doorslag wordt vermeden zonder de BV te verslechteren. Hoewel P-well met een hoge dopingconcentratie voordelen heeft om de punch-through-doorslag te voorkomen, zou het de drempelspanning verhogen. Dus, N pwell van 2 × 10 17 cm −3 wordt gekozen met inachtneming van de drempelspanning en de wisselwerking tussen de BV en R op,sp .

een Numerieke BV als functie van N nb met verschillende N pwell . b Stroomdichtheidsprofiel voor N nb = 10.5 × 10 16 cm −3 en 14,5 × 10 16 cm −3 terwijl N pwell = 2 × 10 17 cm −3 bij pech

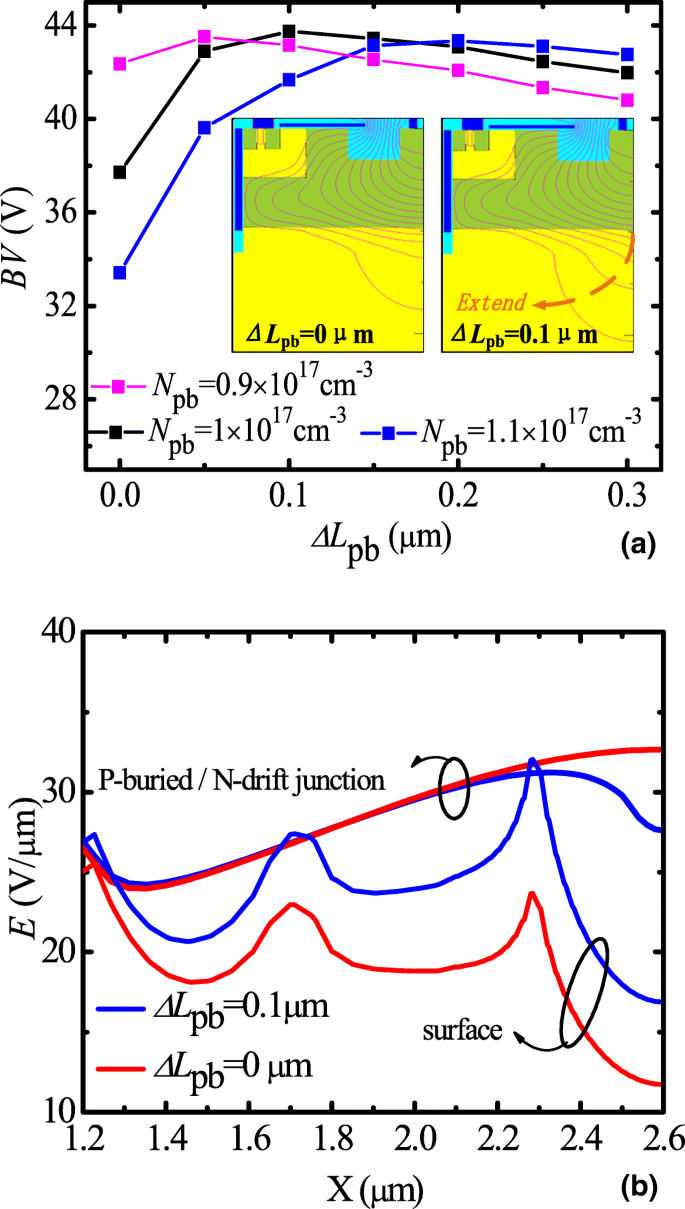

Om een lage R . te bereiken d en een hoge BV, een gedeeltelijk P-begraven laag wordt geïntroduceerd onder het N-driftgebied. Afbeelding 4a toont BV als functie van ΔL PB met verschillende N PB . Voor een gegeven N PB , als ΔL PB neemt toe, BV neemt toe en neemt vervolgens iets af. Wanneer ΔL PB = 0.1 μm, N PB = 1 × 10 17 cm −3 , BV bereikt de maximale waarde 43 V. De inzet toont het equipotentiaalcontourprofiel met N PB = 1 × 10 17 cm −3 . Er wordt aangegeven dat de equipotentiaalcontour in de gedeeltelijke P-begraven laagstructuur zich meer uitstrekt tot het substraat in vergelijking met de volledige P-begraven laag. Figuur 4b toont de verdeling van het elektrische veld aan het oppervlak en de interface van de P-begraven/N-drift-junctie. Voor geoptimaliseerd conventioneel LDMOS vindt de storing gewoonlijk plaats op de N-drift/P-begraven interface. Voor de voorgestelde LDMOS vervangt de kruising van N-drift/P-sub de kruising van N-drift/P-begraven om het verticale elektrische veld te ontspannen en het uitputtingsgebied uit te breiden, wat resulteert in een hogere BV met behoud van een lage R d .

een BV als functie van ΔL PB met verschillende N PB . De wisselplaat is het equipotentiaalcontourprofiel met N PB = 1 × 10 17 cm −3 . b Elektrisch velddistributie aan het oppervlak en de P-begraven/N-drift junctie-interface

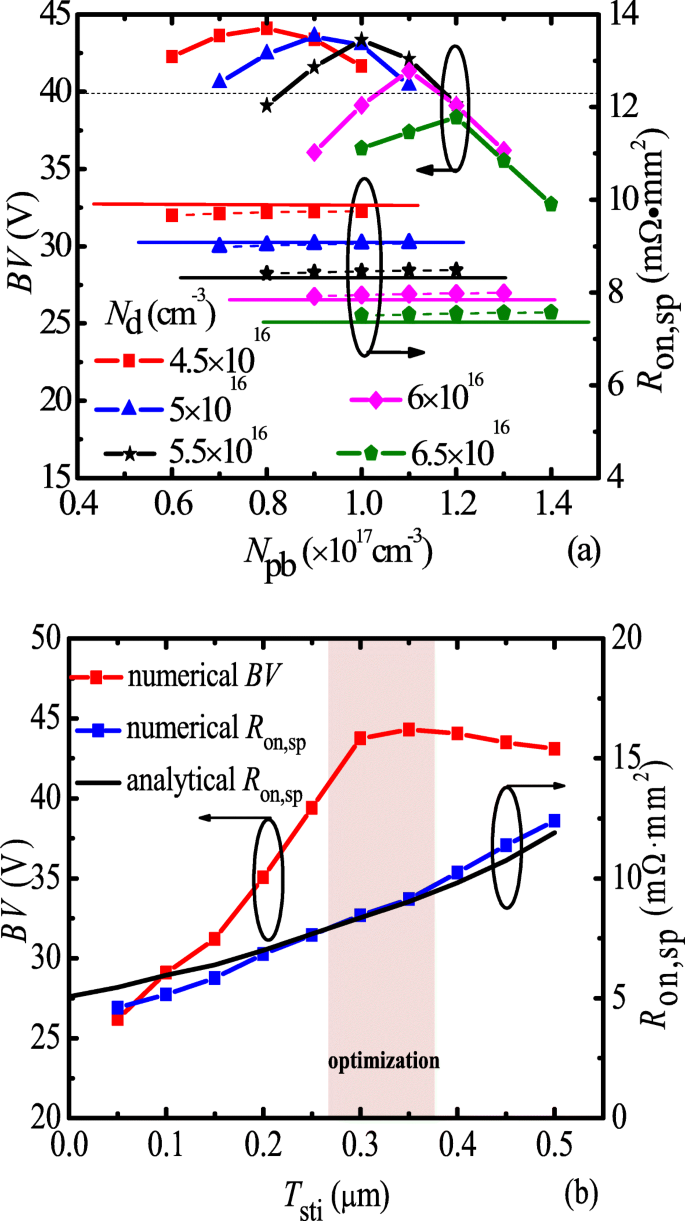

Ladingsbalans tussen N-drift en gedeeltelijk P-begraven laag is vereist om een hoge BV te bereiken. Figuur 5a laat zien dat numerieke en analytische BV en R op,sp als functies van de dopingconcentratie van de P-begraven (N PB ) voor verschillende N d . Voor een gegeven N d , BV heeft een maximale waarde met gevarieerde N PB , en het maximum van BV neemt toe met de afname van N d . Echter, R op,sp kan worden vergroot als de N d afnemend. Vanwege BV vereist hoger dan 40 V, de N d = 5.5 × 10 16 cm −3 en N PB = 1 × 10 17 cm −3 zijn gekozen. Afbeelding 5b toont numerieke en analytische BV en R op,sp als functie van de dikte van de STI-laag (T sti ). T sti heeft een sterke impact op BV en R op,sp , en het moet zorgvuldig worden ontworpen en geoptimaliseerd, evenals ons eerdere werk [21]. Voor T sti < 0,3 m, het doorslagpunt onder de rand van de polyveldplaat heeft een hoge elektrische veldpiek. Als T sti neemt toe, wordt de elektrische veldpiek ontspannen, en dan BV neemt toe. Voor T sti = 0,3 m, BV van 43 V wordt verkregen. Voor T sti ≥ 0,3 m, de elektrische veldpiek onder de rand van de polyveldplaat is voldoende laag, waardoor het doorslagpunt wordt overgedragen naar de P / N-junctie onder de afvoerzijde. Als T sti neemt toe, BV neemt toe en verzadigt dan.

een Numeriek (stippellijn) en analytisch (ononderbroken lijn) BV en R op,sp als functies van N PB voor verschillende N d . b Numeriek (stippellijn) en analytisch (ononderbroken lijn) BV en R op,sp als functies van T sti

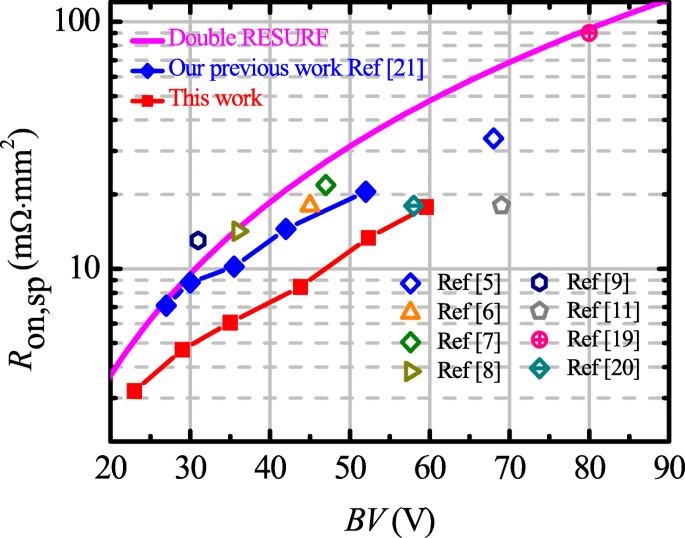

Afbeelding 6 toont de benchmark van bestaande bipolaire-CMOS-DMOS (BCD)-technologieën en de voorgestelde LDMOS. Blijkbaar is de procestechnologie voor voorgestelde LDMOS compatibel met onze ontwikkelde BCD-technologie die de beste prestaties van LDMOS in zijn klasse heeft bereikt. In het fabricageproces voor de voorgestelde LDMOS zou de N-begraven laag hetzelfde masker kunnen delen met P-well. Voor de voorgestelde LDMOS, R op,sp is 8,5 mΩ·mm 2 terwijl BV = 43 V, wat met ongeveer 37% is verminderd in vergelijking met ons vorige werk.

De benchmark van bestaande BCD-technologieën en de voorgestelde LDMOS

Conclusie

In dit artikel wordt een nieuwe LDMOS met ultralage specifieke weerstand tegen weerstand met verbeterde dual-gate en gedeeltelijk P-begraven laag voorgesteld en onderzocht door middel van numerieke simulatie. N-begraven laag met hoge dopingconcentratie wordt gebruikt om verbeterde dual-gate te bereiken met vermindering van R c . Gedeeltelijke P-begraven laag wordt geïntroduceerd onder het N-driftgebied om BV te verbeteren met het bijhouden van de ladingsbalans. Het fabricageproces van de LDMOS in dit werk is compatibel met de bestaande BCD-technologie die in ons vorige werk is gerapporteerd. Het resultaat laat zien dat de R op,sp van de voorgestelde LDMOS wordt verminderd met 37% bij BV van 43 V vergeleken met eerder werk. Nu de halfgeleiderverwerkingstechnologie naar nanometerniveau gaat, is de R op,sp kan verder verminderen met vermindering van de kanaallengte.

Afkortingen

- BCD:

-

Bipolair-CMOS-DMOS

- BV:

-

Doorslagspanning

- LDMOS:

-

Laterale dubbel gediffundeerde metaaloxide-halfgeleidertransistor

- RESURF:

-

Oppervlakteveld verkleinen

- R op,sp :

-

Specifieke aan-weerstand

- USTI:

-

Ultra-ondiepe greppelisolatie

Nanomaterialen

- Nanovezels en filamenten voor verbeterde medicijnafgifte

- Kenmerken van grensvlak-, elektrische en banduitlijning van HfO2 / Ge-stapels met in situ gevormde SiO2-tussenlaag door plasma-versterkte atomaire laagafzetting

- Een nieuwe Bi4Ti3O12/Ag3PO4 heterojunctie-fotokatalysator met verbeterde fotokatalytische prestaties

- Effect van verbeterde thermische stabiliteit van aluminiumoxide-ondersteuningslaag op de groei van verticaal uitgelijnde enkelwandige koolstofnanobuizen en hun toepassing in nanofiltratiemembranen

- Invloed van Ag-nanodeeltjes met verschillende afmetingen en concentraties ingebed in een TiO2-compacte laag op de conversie-efficiëntie van perovskiet-zonnecellen

- Antiproliferatief en apoptose-triggerend potentieel van op paclitaxel gebaseerde gerichte lipide nanodeeltjes met verbeterde cellulaire internalisatie door transferrinereceptoren - een onderzoek in le…

- Omnidirectionele Absorber door het Void Plasmon Effect in de zichtbare regio met sterk verbeterd gelokaliseerd elektrisch veld

- SnSe2-veldeffecttransistor met hoge aan/uit-verhouding en polariteitsschakelbare fotogeleiding

- TiO2-nanomembranen vervaardigd door atomaire laagafzetting voor supercondensatorelektrode met verbeterde capaciteit

- ZnO poreuze nanoplaten met gedeeltelijke oppervlaktemodificatie voor verbeterde ladingsscheiding en hoge fotokatalytische activiteit onder zonnestraling

- Verbeterde Si-passivering en PERC-zonnecelefficiëntie door atomaire laag afgezet aluminiumoxide met tweestaps nagloeiing