Effecten van etsvariaties op Ge/Si-kanaalvorming en apparaatprestaties

Abstract

Tijdens de vorming van Ge-fin-structuren op een silicium-op-isolator (SOI) substraat, ontdekten we dat het droge etsproces zorgvuldig moet worden gecontroleerd. Anders kan dit leiden tot overetsing van Ge of de vorming van een ongewenst Ge-fin-profiel. Als het etsproces niet goed wordt gecontroleerd, wordt de bovenste Ge/SOI-structuur weggeëtst en blijft alleen de Si-fin-laag over. In dit geval vertoont het apparaat abnormale kenmerken. Het etsproces komt naar voren als een cruciale stap in het schalen en verpakken van apparaten en beïnvloedt pogingen om de pakkingsdichtheid te verhogen en de prestaties van het apparaat te verbeteren. Daarom wordt voorgesteld om de werking van de plasmareactor te optimaliseren door middel van simulaties, om niet alleen de gebruikte procesparameters aan te passen, maar ook om de gebruikte hardware te wijzigen. We gaan Ge-junctieloze apparaten ontwikkelen door bijgewerkte fabricageparameters te gebruiken. Bovendien willen we misfit-dislocaties op het grensvlak elimineren of threading-dislocaties verminderen door een cyclisch thermisch uitgloeiproces toe te passen om het doel te bereiken om een hangende structuur van epitaxiale Ge-lagen van hoge kwaliteit te verkrijgen.

Achtergrond

Een manier om de reactiesnelheid van halfgeleiderinrichtingen te verhogen en hun stroomverbruik te verminderen, is het gebruik van een halfgeleider met een hoge draaggolfmobiliteit. Voorbeelden van dergelijke materialen omvatten Ge evenals zijn legeringen en verbindingen. Wanneer echter een structuur wordt gevormd door een laag van een halfgeleidermateriaal op een substraat van een andere halfgeleider te stapelen, kunnen er problemen ontstaan. Het verschil in de roosterafmetingen van het halfgeleidersubstraat en de bovenliggende laag van een ander halfgeleidermateriaal kan bijvoorbeeld dislocaties veroorzaken, wat een nadelig effect kan hebben op de prestaties van het apparaat. Conventioneel wordt, om op Ge gebaseerde halfgeleiderinrichtingen te fabriceren die een Si-substraat bevatten, een dikkere bufferlaag of opofferingslaag (bijvoorbeeld een Si/Ge-bufferlaag) gevormd op het siliciumsubstraat. Vervolgens wordt een epitaxiale Gelaag op de Si/Ge-bufferlaag gekweekt. Vervolgens worden anisotrope en isotrope etsprocessen achtereenvolgens uitgevoerd om een deel van de bufferlaag te verwijderen en de epitaxiale Ge-laag te behouden. VLSI-apparaten moeten een hoge aandrijfstroom, een lage lekstroom buiten de staat en een lage voedingsspanning vertonen om hoge prestaties te garanderen, inclusief een laag energieverbruik in stand-by en verminderde dynamische vermogensdissipatie. Momenteel zijn spanningsverbeterde mobiliteit, high-k/metal gate en driedimensionale (3D) apparaatarchitectuur op het 22 nm-knooppunt [1] enkele van de technologieën die worden gebruikt voor de continue schaling van complementaire metaaloxide-halfgeleider ( CMOS) apparaten met een Si-kanaal. Naast kenmerken zoals hoge mobiliteit, zijn nieuwe apparaatarchitecturen zoals die van gate-all-around (GAA) [2] en ultradunne-lichaamsveldeffecttransistoren (FET's) [3] nodig om de elektrostatische controle in de sub te verbeteren. -10 nm-knooppunten. Ge-gebaseerde GAA pFET's [4] en nFET's [5] met inversion-mode (INV) werking zijn aangetoond. De vorming van knooppunten in Ge INV-apparaten is echter een kritiek probleem vanwege de lage doteringsoplosbaarheid, snelle doteringsdiffusie en het lage thermische budget. Om deze problemen op te lossen, zijn junction-less (JL) apparaten [6] die een zwaar gedoteerd kanaal gebruiken met hetzelfde draaggolftype als dat van de source/drain (S/D)-regio's voorgesteld als alternatieven. De snelle schaalvergroting van transistors vereist echter de ontwikkeling van nieuwe en effectievere apparaten die moderne transistors kunnen inhalen. In de afgelopen jaren is gebleken dat JL-FET's veelbelovend zijn als transistors van de volgende generatie. De JL-FET is in feite een weerstand waarin de dichtheid van de mobiele drager kan worden geregeld door de poort. In de AAN-toestand is er door de relatief hoge doteringsconcentratie in het kanaalgebied een grote lichaamsstroom; de oppervlakteaccumulatiestroom wordt bij deze stroom opgeteld. Het dopingniveau in de JL-FET moet hoog zijn om een geschikte stroomaandrijving te bereiken, terwijl de doorsnede van het apparaat klein genoeg moet zijn zodat het apparaat kan worden uitgeschakeld . In het geval van sterk gedoteerde JL-FET's ondergaan de dragers echter aanzienlijke onzuiverheidsverstrooiing, waardoor de aandrijfstroom aanzienlijk wordt verslechterd [7]. Bovendien hebben JL-FET's de voordelen dat ze eenvoudig te fabriceren zijn en een hoge ladingsmobiliteit en lage poortcapaciteit hebben, in tegenstelling tot INV-apparaten [8,9,10,11,12]. Onlangs werden dubbele poort [13] en lichaamsgebonden tri-poort [14] Ge JL-FET pMOSFET's gedemonstreerd op respectievelijk germanium-op-isolatorsubstraten en bulk Si.

Naarmate micro-elektronische apparaten blijven krimpen en de procesvereisten steeds strenger worden, worden plasmamodellering en -simulatie steeds aantrekkelijker als hulpmiddel voor ontwerp, controle en optimalisatie van plasmareactoren [15]. Verschillende technieken worden gebruikt om het gedrag van plasmaprocessen te simuleren op basis van de ongelijkheid in lengte- en tijdschalen. Een van de simulatietechnieken, computationele vloeistofdynamica (CFD), wordt veel gebruikt om de stromingsvelden voor technische ontwerpkenmerken te voorspellen en om experimentele beperkingen te extrapoleren. De modellering ervan is toegepast om de stromings-mengverschijnselen [16] te onderzoeken, maar zeldzaam onderzoek in het etsproces. Daarom stelde deze studie voor om het thermische stroomveld van plasmareactoren voor het etsproces in detail te karakteriseren en vervolgens numerieke parameters af te leiden die nuttig kunnen zijn voor experimenten.

In dit werk werd etsen uitgevoerd om gesuspendeerde epitaxiale Ge-lagen over Si en andere legeringshalfgeleiders te vormen voor apparaatintegratie. De gesimuleerde resultaten zullen worden gevalideerd door experimenten; daarom zullen initiële en randvoorwaarden evenals parameters in het numerieke model worden gewijzigd om de betrouwbaarheid van de gegevens te vergroten. We verwachten dat optimale parameters kunnen worden verkregen door experimenten en simulaties om de etstechnieken te verbeteren, en om aan deze transistorontwikkeling te voldoen door een hogere fabricageproceskwaliteit en lagere productiekosten uit te voeren.

Methoden/experimenteel

De uitgangssubstraten waren SOI-wafels met een siliciumlaag van 70 nm (p-type, 9-18 Ω cm). De wafels werden gereinigd met behulp van de RCA-standaard clean 1 (SC-1) en RCA-standaard clean 2 (SC-2) processen, om alle aanwezige organische stoffen, ongewenste metalen en deeltjes te verwijderen. Dit werd gevolgd door spoelen in gedeïoniseerd water en drogen in N2 . De Ge-film werd afgezet in een lagedruk chemische dampdepositie epitaxiale reactor (Epsilon 2000, ASM) met 10% GeH4 als voorloper. Als draaggas werd waterstof gebruikt. Vóór de afzetting van de Ge-film werd een in situ HCl-gebaseerde voorbehandeling uitgevoerd bij 850 ° C en 10 Torr om het wafeloppervlak voor te bereiden. De substraattemperatuur werd vervolgens gewijzigd in 400 °C om een Ge-film op de SOI-wafer te laten groeien met 10% GeH4 . De diktes van de afgezette Ge-films werden bepaald met behulp van transmissie-elektronenmicroscopie (TEM, thermische emissie Schottky-type, 0,5-200 kV). De kristalliniteiten van de Ge-films werden onderzocht met behulp van röntgendiffractie (XRD) -analyse (D8A, Bruker, CuKa-straling, λ =-1,5408 , 20-70 °). Bovendien werden Ω-2θ-scans uitgevoerd rond de (004) diffractiepiek met behulp van een X'Pert MRD (PANalytical) -systeem. Een tweevoudige Ge {400} kanaalgeslepen kristalcollimator werd gebruikt om de CuKa1-straling te selecteren. Tijdens de standaard XRD-metingen werd het monster in een horizontale positie gefixeerd en werden de bron en detectorarm van de diffractometer in de θ-θ-modus bewogen. Wederzijdse ruimtetoewijzing werd uitgevoerd in de modus met gemiddelde resolutie met behulp van de bovengenoemde kristalcollimator; Op de detectorarm voor de scintillatieteller waren 0,4 mm brede sleuven aanwezig. De diktes van de Ge-lagen werden bepaald via ellipsometriemetingen (M2000, J.A. Woollam Co., λ = 193-1690 nm). De vin werd gevormd door anisotroop plasma-etsen met Cl2 /HBr-gas. Na de vorming van de ZrO2 /TiN-poort, de S/D werden geïmplanteerd met B (1 × 10 15 cm −2 , 15 keV) en geactiveerd door snel thermisch uitgloeien bij 550 °C gedurende 30 s.

Zeer selectieve droge etsing van het germaniummechanisme

Elektronen- en neutrale reacties zijn isotroop, terwijl ionenreacties zeer gericht zijn en variëren met de toegepaste bias. Door het voorspanningsvermogen aan te passen, kunnen de ionen in de gewenste richting worden versneld om de etsreactie te ondersteunen. Het is algemeen aanvaard dat Br niet spontaan reageert met Si en dat er energetische ionen nodig zijn om de reactie te laten plaatsvinden. Ion-geassisteerde Br- en Cl-atomen kunnen spontaan reageren met Ge- of Si-atomen onder activering om de vluchtige producten GeBr4 te vormen , GeCl4 , SiBr4 , en SiCl4 , die van het substraatoppervlak worden gedesorbeerd en kunnen worden weggepompt. Deze door ionen ondersteunde chemische reactie van Si met Br is zeer anisotroop gebleken. Hogere verticale etssnelheden werden verkregen met HBr voor variaties in het biasvermogen, wat de toevoeging van HBr in Cl2 bevestigt kan de etssnelheid verbeteren [17]. Omdat plasma op Cl- en Br-basis Ge en Si etst door een ion-geassisteerd mechanisme, wordt de energie van ionen zoals Br + , Br 2+ , HBr + , Cl + , en Cl2 + kan worden geregeld door de substraathouder voor te spannen. Er is geen uitgesproken verandering van de laterale etssnelheid door het voorspanningsvermogen te variëren voor zowel het etsen aan het bovenoppervlak als het insnoeringsgebied. Er werden ondersnijdingen gevonden in de vinstructuren die waren geëtst met HBr-mengsels, in het insnoeringsgebied, omdat lateraal etsen werd versterkt door de defecten langs het Ge/Si-grensvlak. En ook het masker beïnvloedt mogelijk de vormevolutie vanwege de zijwand die door ionenstroom wordt geraakt. Dit fenomeen wordt versterkt naarmate het profiel dieper wordt en naarmate de laterale ionsnelheidscomponent toeneemt. Vanwege de hoge hoekafhankelijkheid van het HBr-plasma-etsproces [18] kan dus worden geconcludeerd dat de kristalstructuur relatief zwakker is aan het Ge/Si-grensvlak vanwege de gedeeltelijk gebonden atomen van de misfit-dislocaties en de relatief zwakke Ge-Ge- en Ge-Si-bindingen. Door de verhouding van HBr/Cl2 . aan te passen en biaskracht, kunnen verschillende soorten vinachtige structuren worden verkregen tijdens de fabricage van Ge-apparaten. De etseigenschappen van Ge en Si lijken erg op elkaar. Gassen die Si etsen, etsen Ge gewoonlijk met een grotere snelheid. Het is aangetoond dat de sterke punten van Ge- en Si-bindingen Ge-Ge = 263.6 ± 7.1 kJ mol −1 zijn en Si-Si = 325 ± 7 kJ mol −1 [2]. Er werden verschillende voorspanningskrachten toegepast om de verticale etssnelheid aan te passen door gerichte versnelling van de ionen. Beelden werden opgenomen na het gate-stackproces. De verticale etssnelheid werd berekend uit de filmhoogte ten opzichte van het oxidesubstraat. Laterale etssnelheden werden bepaald aan de hand van twee delen van de vin:het laterale etsen op het bovenoppervlak van de vin en het etsen in het vernauwingsgebied dichtbij het Ge/Si-grensvlak. Samenvattend werd experimenteel gevonden dat het biasvermogen de meest kritische parameter in het etsproces is en daarom de kenmerken van het apparaat dienovereenkomstig beïnvloedt.

In deze studie werden alle etsprocessen uitgevoerd in een TCP 9600-reactor van Lam Research. Dit is een aan een transformator gekoppelde plasmareactor die een afzonderlijke regeling van het spoelvermogen (bovenste elektrode) en de voorspanning van het substraat (onderste elektrode) mogelijk maakt. Helium backside koeling is ingebouwd om de temperatuur van het substraat beter te kunnen regelen. De monsters werden gemonteerd op een 6-in. Si-dragerwafel met vacuümvet voordat deze in de etskamer wordt gebracht. HBr/Cl2 chemie werd benut voor het anisotrope etsproces. De procesdruk werd geregeld op 10 mTorr. De gedetailleerde experimentele opstelling en omstandigheden worden geïllustreerd in de studie van Hsu et al. [4].

Fysiek model

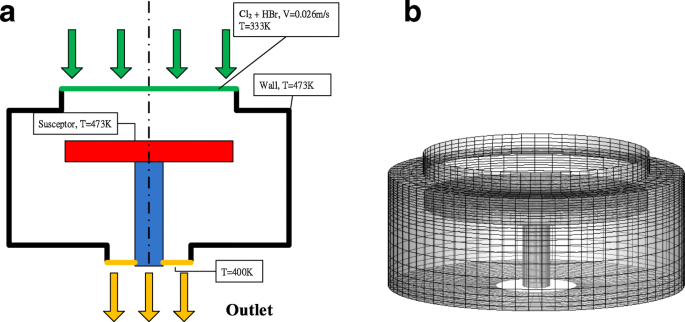

CFD wordt gebruikt om toegang te krijgen tot de interne informatie in de reactor en de stroom wordt beschouwd als laminair met de slipgrensvoorwaarde vanwege het hogere Knudsen-getal in de kamer (Fig. 1). In de huidige simulatie wordt de thermische plasmastroom beschouwd als een mengsel in de impulsvergelijkingen; deeltjestransport wordt beschouwd in de soortvergelijkingen en chemische reacties zijn betrokken op de susceptorwand. Een modelgeval voor simulatie wordt geïllustreerd in Fig. 3. Het inlaatgas is een mengsel van chloor (Cl2 ) en waterstofbromide (HBR). De snelheid van het mengsel bij de inlaat is 0,026 m/s met een temperatuur die op 333 K wordt gehouden. De susceptor en de kamerwand worden verwarmd tot een bedrijfstemperatuur van 473 K. Deze plasmastroom wordt aangedreven door elektrische potentiaalvoorspanning en heeft chemische reacties op het oppervlak van de susceptor in een uniforme, herhaalbare manier, en tenslotte om uit de reactor te worden afgevoerd. Na het bouwen van de solide modellering door de CAD-software, werd het mesh-systeem geconstrueerd in gestructureerde rasters met 50.000 knooppunten zoals weergegeven in Fig. 3. De tijdelijke behoudsvergelijking voor transport van een scalaire hoeveelheid ϕ wordt gedemonstreerd door de volgende vergelijking geschreven in integraal formulier voor een willekeurig regelvolume V als volgt [19]:

Fysisch model voor numerieke simulatie van plasmareactor. een De schets van de reactorkamer met voorgeschreven randvoorwaarden. b Mesh-systeem voor numerieke simulaties

$$ \frac{d}{dt}\underset{V}{\oint}\rho \varphi\;dV+\oint \kern0.27em \rho \varphi \overset{\rightharpoonup }{v}\cdot \mathrm{ d}\overrightarrow{\mathrm{A}}=\oint \Gamma \mathrm{\nabla}\varphi \cdot \mathrm{d}\overrightarrow{\mathrm{A}}+{\int}_{\mathrm{ V}}{\mathrm{S}}_{\varphi}\mathrm{dV} $$ (1*)waarbij ρ dichtheid aangeeft; \( \overset{\rightharpoonup }{v} \) is snelheidsvector; \( \overset{\rightharpoonup }{A} \) is oppervlaktevector; V is volume; Γ is de diffusiecoëfficiënt voor ϕ en Sϕ is de bronterm van ϕ per volume-eenheid. Het symbool ϕ kan worden vervangen door 1 voor de continuïteitsvergelijking, u , v , en w zijn de impulsvergelijkingen in de X-, Y- en Z-richtingen, en Ci voor respectievelijk de soorttransportvergelijkingen in de reactorkamer. vgl. (1*) kan worden uitgedrukt in gegeneraliseerde coördinaten met behulp van de eindige-volumemethode voor simulatie. Na het combineren van randvoorwaarden, Vgl. (1*) kan worden gelineariseerd en uitgedrukt in het computationele domein als een reeks algebraïsche vergelijkingen, die kunnen worden opgelost door het SIMPLE-algoritme met behulp van de CFD-techniek [19]. Merkte op dat de meeste apparaten voor de fabricage van halfgeleiders ver onder de atmosferische druk werken. Bij dergelijke lage drukken bevindt de vloeistofstroom zich in het slipregime en zijn de normaal gebruikte no-slip randvoorwaarden voor snelheid en temperatuur niet langer geldig. De huidige plasmastroom bij zeer lage druk bevindt zich in het slipregime, dat tussen de vrije moleculaire stroom en het continuümregime ligt [20]. Daarom worden in onze numerieke simulaties sliprandvoorwaarden voor snelheid en temperatuur opgelegd voor het modelleren van vloeistofstroming.

De halfgeleidermaterialen Si(s) en Ge(s) worden weggeëtst op het verwarmde oppervlak van de susceptor, beheerst door de volgende oppervlaktereacties:

$$ {\mathrm{Cl}}_2+\mathrm{Si}={\mathrm{SiCl}}_4 $$ (2*.1) $$ 4\mathrm{HBr}+\mathrm{Si}={\mathrm {SiBr}}_4+2{\mathrm{H}}_2 $$ (2*.2) $$ 2{\mathrm{Cl}}_2+\mathrm{Ge}={\mathrm{GeCl}}_4 $$ (2*.3) $$ 4\mathrm{HBr}+\mathrm{Ge}={\mathrm{GeBr}}_4+2{\mathrm{H}}_2 $$ (2*.4)De chemische reacties zijn vergelijkbaar voor Si-etsen in Vgl. (2*.1) en Vgl. (2*.2), of Ge-etsen in Vgl. (2*.3) en Vgl. (2*.4). Daarom wordt het Si-etsproces door het mengsel van chloor en waterstofbromide gedemonstreerd in de volgende simulaties.

Resultaten en discussie

Materiaalkarakterisering

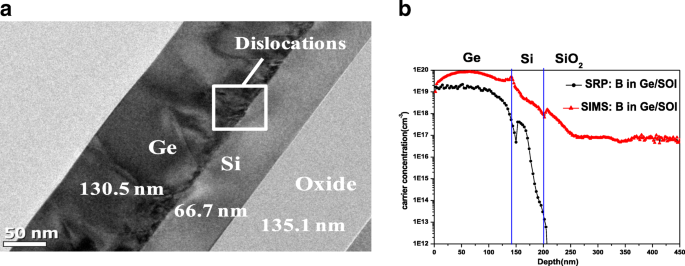

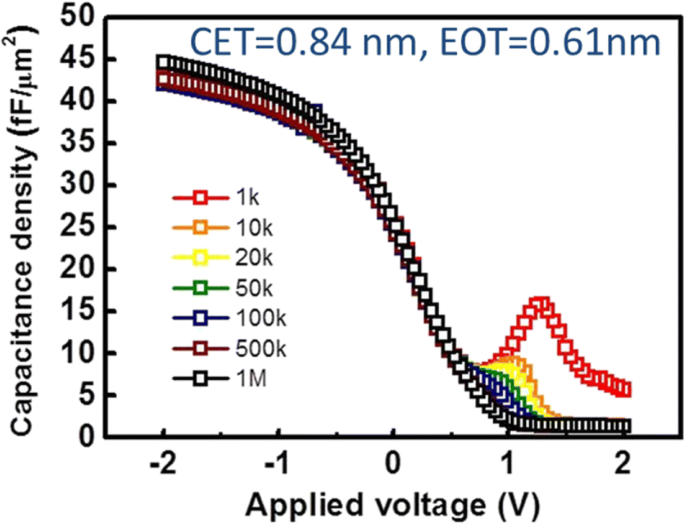

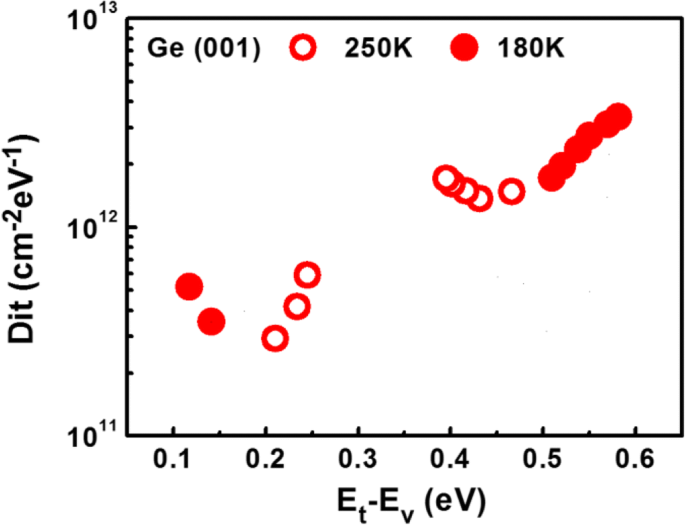

Dwarsdoorsnede TEM-afbeeldingen van de Ge-laag gevormd op het SOI-substraat worden getoond in Fig. 2a. Zoals te zien is, zijn er misfit-dislocaties aanwezig op de Ge/Si-interface; deze resulteren op hun beurt in threading dislocaties over de epitaxiale Ge-film. Aangenomen wordt dat deze threading-dislocaties de thermische mismatch tussen Ge en Si opvangen. De meeste threading-dislocaties eindigden binnen 80 nm van de interface; veel plantten zich echter ook voort op het filmoppervlak. De epitaxiale Ge-film op het SOI-substraat werd geïmplanteerd met boor en vervolgens geactiveerd om de doteringsverdeling en het activeringsniveau te onderzoeken. Voor het bovenste 130 nm-deel van de Ge-laag was de booractiveringssnelheid ∼ 85%, zoals weergegeven in de PCOR-SIMS en spreidingsweerstandsprofilering (SRP) profielen. (zie afb. 2b). De gatenconcentratie daalde significant in het geval van de bodem van de Ge-laag nabij het Ge/Si-grensvlak, vanwege de aanwezigheid van defecten en vanwege de meetlimieten van SRP. In het geval van de gefabriceerde apparaten werd het defecte Ge nabij de Ge/Si-interface verwijderd door selectief etsen; de PCOR-SIMS- en SRP-metingen die in het kanaal worden uitgevoerd, moeten dus nauwkeurig zijn. Het maximale activeringsniveau van ~ 3 × 10 19 cm −3 is volledig in overeenstemming met de conventionele activeringslimiet. Merk op dat als gevolg van de activering bij lage temperatuur (550 ° C) uitgevoerd tijdens boorimplantatie, de S / D nabij het parasitaire Si-kanaal zeer resistief was (figuur 2); dit verhinderde parasitaire Si-geleiding. Afbeelding 3 toont de capaciteit-spanning (CV) karakteristieken van de TiN/ZrO2 /Ge metaal-isolator-halfgeleidercondensatoren (MISCAP's). Om de vorming van een onstabiele GeOx . te voorkomen laag tijdens het hoge-k diëlektrische depositie en post-depositie gloeiproces, het op nitride gebaseerde materiaal Ge3 N4 en niet GeO2 werd ingevoegd als de interfacelaag op het Ge (001)-oppervlak via een NH3 /H2 plasmabehandeling op afstand. De ZrO2 laag werd gedurende 20 cycli bij 250°C afgezet door afzetting van een atomaire laag. De gemeten CV-curven geven geen frequentiespreiding of rek van 1 KHz tot 1 MHz aan en zijn consistent. Het verlies, dat valniveaus creëert in de buurt van de ZrO2 /Ge-interface, verschuift de thermische activeringsenergie voor het genereren van minderheidsdragers van die die overeenkomt met de p-Ge bandgap-energie naar de midgap-energie. De equivalente oxidedikte (EOT) is 0,6 nm en de D het (Interface-trap-dichtheid) waarde is ~ 3 × 10 12 cm 2 eV −1 in de buurt van de middenspleet, zoals gemeten met de geleidingsmethode bij lage temperatuur (zie inzet van Fig. 4).

een Het TEM-beeld van het p-type Ge op SOI-substraat. b De SIMS- en SRP-profielen van de in situ met boor gedoteerde epi-Ge-laag op SOI. De gatenconcentratie is laag in de onderste defecte Ge nabij de Ge/Si-interface

C-V-kenmerken van de TiN/ZrO2 /Ge MISCAP's met EOT ~ 0,6 nm

Dit gemeten met een lage temperatuur geleidingsmethode

Simulatie voor de parameters van de werking van de reactor

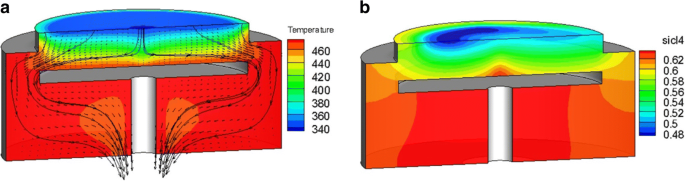

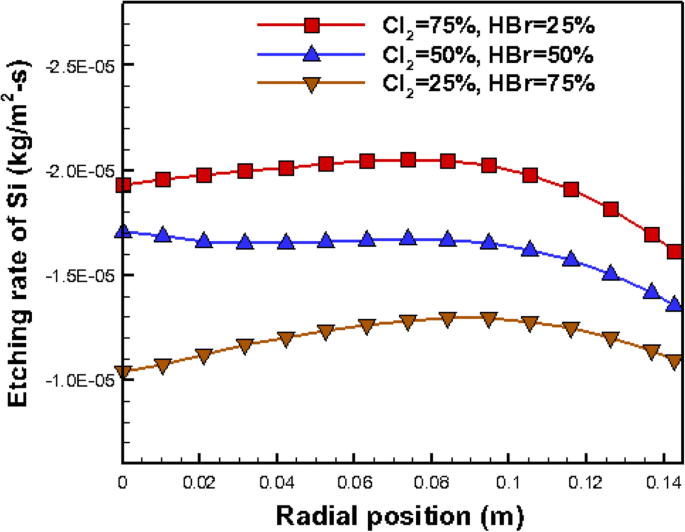

Een typisch model van stabiele laminaire plasmastromen werd gesimuleerd op high-speed personal computers. Het inlaatgas is een mengsel van Cl2 , die een massafractie van 0,75 heeft, en HBr, die een massafractie van 0,25 heeft. Figuur 5a illustreert de contouren van de instroom bij lage temperatuur, bij hogere temperatuur binnen en de deeltjespadlijnen in de reactorkamer. Figuur 5b toont de massafractiecontouren van product SiCl4, dat een lage concentratie boven de susceptor heeft en een hoge concentratie onder de susceptor naar de uitgang. Bovendien, hogere massafractie van Cl2 behaalt goede prestaties bij het etsen, en deze knowhow is gevalideerd door huidige simulaties zoals getoond in Fig. 6. De horizontale as vertegenwoordigt langs één radiale positie op de susceptor en de verticale as geeft de etssnelheid aan (kg/m 2 s) van Si. Figuur 6 laat zien dat het betere etsproces wordt gearchiveerd door het inlaatmengsel van 75% Cl2 en 25% HBr, en dit mengsel werd gebruikt om experimenten uit te voeren in deze studie.

Contouren van plasmaparameters in de reactor. een Temperatuurverdeling en deeltjespadlijnen r. b Massafractiecontouren van product SiCl4

Etssnelheden van Si op de susceptor van mengsels van inlaatgassen met verschillende fracties

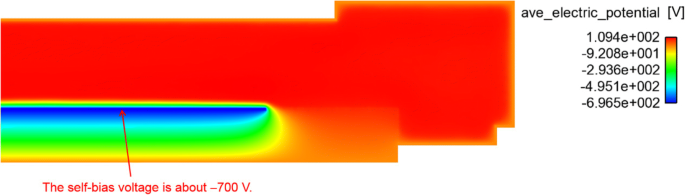

Een ander geval om de haalbaarheid van computerondersteunde experimenten aan te tonen, is de verdeling van elektrische potentiaal in de kamer voor plasma-etsen. Gebaseerd op het onderliggende mechanisme van dit etsproces, werd een 2D-simulatiemodel ontwikkeld voor de verdeling van de plasmavermogensdichtheid zoals weergegeven in Fig. 7 en werd gebruikt om de meetgegevens te passen, om de nauwkeurigheid van het model te bevestigen en te helpen het experiment.

Simulatie van elektrische potentiaalverdeling voor plasma-etsen in de kamer

Zoals voorgesteld door Sugai [21], kan de zelfvoorspanning worden gerelateerd aan de capaciteiten van de mantel op de RF-elektrode (CK ) en aardelektrode (CA ), en als volgt uitgedrukt:

$$ {V}_{\mathrm{DC}}=\frac{C_{\mathrm{K}}-{C}_{\mathrm{A}}}{C_{\mathrm{K}}+{C }_{\mathrm{A}}}\ {V}_{\mathrm{RF}} $$ (3*)Volgens de huidige simulaties zoals weergegeven in Fig. 7, is de zelfvoorspanning ongeveer -700 V, wat dicht bij de theoretische waarde ligt, -650 V, zoals berekend uit Vgl. (3*). Daarom wordt voorgesteld om optimalisatie uit te voeren met behulp van simulaties om niet alleen de gebruikte procesparameters aan te passen, maar ook om de gebruikte hardware te wijzigen. Dit zorgt voor uniformiteit over de hele run en leidt tot hoogwaardige, goedkope processen die zijn geoptimaliseerd.

Apparaatfabricage en karakterisering

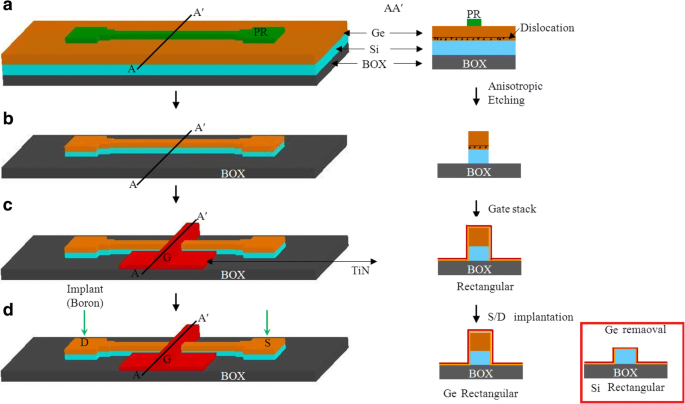

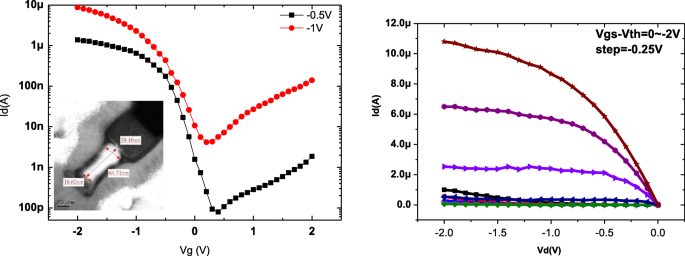

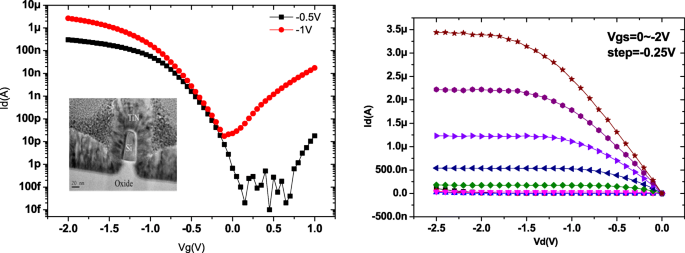

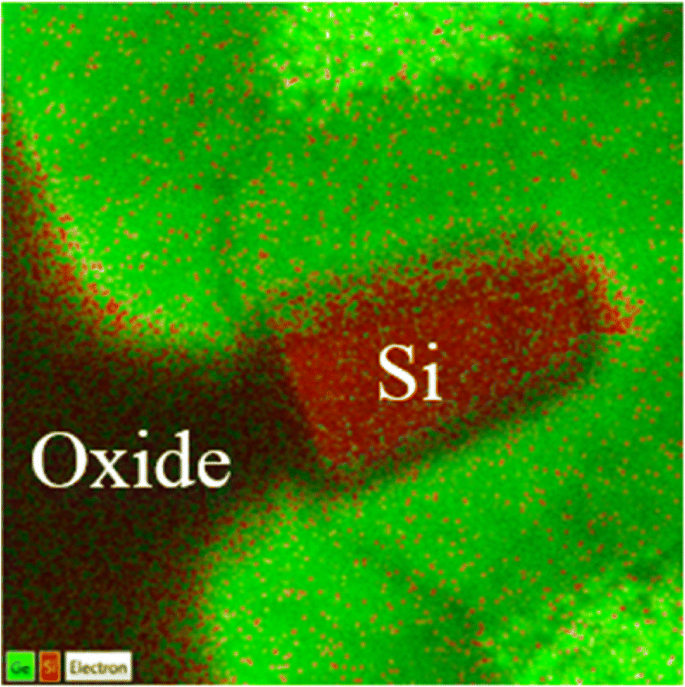

De epitaxiale Ge-laag werd met behulp van e-beam-lithografie tot vinnen met de gewenste functiegroottes gevormd. De vin werd gevormd door anisotroop etsen met Cl2 /HBr-gebaseerd plasma om de hoog-defecte Ge nabij Ge/Si-interface weg te etsen. De zwevende Ge-vin op SOI werd gevormd met de hogere etsselectiviteit van Ge dan Si en de verhoogde etssnelheid van het defecte gebied [4]. Een SiO2 afdeklaag werd vervolgens afgezet en werd de afstandhouder na poortpatroonvorming. Na het definiëren van het actieve gebied, worden de gate-stacks van ZrO2 laag werden respectievelijk gevormd door ALD. De kanaaldoorsneden van gefabriceerde apparaten worden getoond in Fig. 8. De vinbreedte (W fin ) wordt gebruikt voor de kanaalconcentratie van 8 × 10 19 cm − 3 die wordt geëxtraheerd met behulp van de van der Pauw-methode op een deken Ge-epi-laag op SOI. Merk op dat de beheersbaarheid van het kanaal afneemt met toenemende kanaalconcentratie en toenemende W fin [12, 13]. De grote kanaalconcentratie vereist de kleine W fin om de lage SS te behouden. Ten slotte werden de poortelektroden gedefinieerd en gedeponeerd. Figuur 9 toont de uitvoer- en overdrachtskarakteristieken van een driehoekige Ge FinFET met een vinbreedte (W fin ) van 18 nm en poortlengte (L g ) van 90 nm. De ik aan /Ik uit verhouding van de Ge JL-FET is zo hoog als 10 5 en de subdrempelzwaai (SS) is ~ 100 mV dec − 1 . De overdrachtskarakteristieken van de Si JL-FET zijn weergegeven in Fig. 10. De I aan /Ik uit verhouding van de Si JL-FET is hoog als ~ 10 8 , de SS is 90 mV dec − 1 , het is L g is 80 nm, en zijn W fin is 20nm. Figuur 8 laat ook zien dat de spanwijdte van de poortspanning, ΔV g , is ongeveer 0,5 V en ligt dicht bij de bandgap van Ge (E g /q =0,66 V). Dit bevestigt dat de I d –V g curven getoond in Fig. 8 zijn voor een Ge FinFET. Echter, de spanwijdte van de poortspanning, ΔV g , getoond in Fig. 6 is ongeveer 1,8 V en dicht bij de bandgap van Si (E g /q = 1.1 V) maar niet die van Ge (E g /q =0,66 V). Dus de ik d –V g curven getoond in Fig. 9 zijn voor een Si JL-FET en niet voor een Ge JL-FET. Deze waarneming is gebaseerd op de fysica van halfgeleiderapparaten en wordt ondersteund door de experimenteel bepaalde I d –V g krommen van de Ge en Si FinFET's evenals de transversale TEM/EDS Si-kaarten. Twee dingen worden duidelijk uit de inzetstukken in Fig. 11. De inzetstukken tonen de uitvoer- en overdrachtskarakteristieken van de onverwachte Si JL-FET na overetsen van Ge; de ik aan /Ik uit verhouding van dit apparaat is zo hoog als 10 8 . De AAN-stroom is echter slechts 17 μA μm − 1 bij − 1 V. De hoge I aan /Ik uit verhouding is toe te schrijven aan de Si-laag en niet aan de Ge-laag. Als alleen de Si-laag over is, is het apparaat eigenlijk een Si JL-FET in plaats van een Ge JL-FET.

Schema van de fabricage van het apparaat. een Vinnen patroon. Het uitgangsmateriaal is Ge (130 nm) op BOX. b Anisotroop etsen en fotoresiststriping. c Poortvorming door atomaire laagafzetting van ZrO2 en TiN-afzetting. d Zelf-uitgelijnde boorimplantatie op S/D voor goed contact. Opmerking:de linkerkant is het 3D-schema en de rechterkant is de overeenkomstige dwarsdoorsnede

Ik d –V g en ik d –V d curve voor de Ge FinFET

Ik d –V g en ik d –V d voor de Si FinFET nadat de top Ge achteloos is weggeëtst. Hoewel ik aan /Ik uit kan 10 8 . bereiken , de huidige waarde is erg laag

TEM-mapping voor de kanaalstructuur die een overetsproces ondergaat

Conclusies

We bevestigen de relatie tussen simulatiemodel en meetgegevens. Daarom wordt voorgesteld om optimalisatie uit te voeren met behulp van simulaties om niet alleen de gebruikte procesparameters aan te passen, maar ook om de gebruikte hardware te wijzigen. Met behulp van numerieke simulaties om de bedrijfsparameters voor de rector te bepalen, hebben we aangetoond dat de parameters voor het etsproces voor het vormen van Ge/Si-kanalen kunnen worden geoptimaliseerd door middel van experimenten, om het etsproces te verbeteren en de ontwikkeling van transistors te ondersteunen door het verbeteren van de fabricagekwaliteit en het verlagen van de productiekosten. De experimentele resultaten gaven aan dat de droge etstechniek die is ontwikkeld voor Ge FinFET's ook uiterst nuttig is voor de fabricage van CMOS-apparaten met hoge vin.

Nanomaterialen

- Geavanceerde atoomlaagdepositietechnologieën voor micro-LED's en VCSEL's

- Dip-coating procestechniek en prestatie-optimalisatie voor drie-staten elektrochrome apparaten

- Kenmerken van grensvlak-, elektrische en banduitlijning van HfO2 / Ge-stapels met in situ gevormde SiO2-tussenlaag door plasma-versterkte atomaire laagafzetting

- Substitutionele doping voor aluminosilicaatmineraal en superieure watersplitsingsprestaties

- Optische en elektrische kenmerken van silicium nanodraden bereid door stroomloos etsen

- De effecten van Li/Nb-verhouding op de voorbereiding en fotokatalytische prestaties van Li-Nb-O-verbindingen

- De oppervlaktemorfologieën en eigenschappen van ZnO-films afstemmen door het ontwerp van grensvlakken

- Voorbereiding en fotokatalytische prestaties van LiNb3O8-fotokatalysatoren met holle structuur

- De koppelingseffecten van oppervlakteplasmonpolaritons en magnetische dipoolresonanties in metamaterialen

- Fotogeleiding, pH-gevoeligheid, ruis en kanaallengte-effecten in Si Nanowire FET-sensoren

- Laseretsen en lasergraveren