Ge pMOSFET's met hoge mobiliteit met amorfe Si-passivering:impact van oppervlakteoriëntatie

Abstract

We rapporteren de amorfe Si-passivering van Ge pMOSFET's vervaardigd op (001)-, (011)- en (111)-georiënteerde oppervlakken voor geavanceerde CMOS- en dunne-filmtransistortoepassingen. Amorfe Si-passivering van Ge wordt uitgevoerd door magnetronsputteren bij kamertemperatuur. Met de vaste dikte van Si t Si , (001)-georiënteerde Ge pMOSFET's bereiken de hogere on-state stroom I AAN en effectieve mobiliteit van gaten μ eff vergeleken met de apparaten op andere oriëntaties. Bij een inversieladingsdichtheid Q inv van 3,5 × 10 12 cm −2 , Ge(001) transistoren met 0,9 nm t Si toon een piek μ eff van 278 cm 2 /V × s, wat 2,97 keer hoger is dan de universele mobiliteit van Si. Met het verlagen van t Si , ik AAN van Ge-transistors neemt toe als gevolg van de vermindering van de capacitieve effectieve dikte, maar subthreshold swing- en lekvloerkarakteristieken worden verslechterd, toegeschreven aan de toename van midgap D het .

Achtergrond

Germanium (Ge) trekt enorme onderzoeksinteresses aan voor geavanceerde CMOS- en dunne-filmtransistortoepassingen vanwege de grotere gatenmobiliteit en lagere thermische budgetverwerking in vergelijking met Si [1,2,3,4,5,6]. Om de hoge kanaalmobiliteit te bereiken, is het oppervlakpassiveringsproces dat leidt tot een hoge interfacekwaliteit vereist voordat de gate-stack wordt gevormd. Er zijn verschillende oppervlaktepassiveringstechnieken ontwikkeld om de voordelen van dragermobiliteit in Ge-metaaloxide-halfgeleider-veldeffecttransistoren (MOSFET's) te leveren [1, 2, 7,8,9,10]. Van deze technieken is een op Ge gepassiveerd silicium (Si) de laatste jaren de hotspot geweest, vanwege de voordelen van een effectieve onderdrukking van interfacetoestanden en goede thermische stabiliteit en betrouwbaarheid [11]. De vorming van Si-passiveringskap is uitgebreid bestudeerd met behulp van chemische dampafzetting (CVD) met voorlopers van SiH4 [1], Si2 H6 [4], Si3 H8 [12], en E-beam verdamping [13]. Hoewel de CVD-methode de meer uniforme passiveringslaag over fysieke dampafzetting (PVD) zou kunnen bieden, heeft de passiveringssnelheid de sterke correlatie in de oriëntatie van het kanaaloppervlak en de procestemperatuur. PVD-techniek zou de verbeterde passiveringssnelheid zelfs bij kamertemperatuur kunnen bieden, wat de voordelen heeft van een laag thermisch budget en lage kosten, waardoor het meer geschikt is voor dunnefilmtransistors en back-end-of-line 3D-integratietoepassingen. In deze brief hebben we Ge pMOSFET's met hoge mobiliteit gefabriceerd op (001)-, (011)- en (111)-georiënteerde oppervlakken met behulp van amorfe Si-passivering door magnetronsputteren. Aanzienlijk verbeterde effectieve mobiliteit van gaten μ eff wordt bereikt in Ge-transistors in vergelijking met de universele Si-mobiliteit. Effecten van oppervlakteoriëntatie en dikte van amorf Si t Si over het versterkende effect van amorfe Si-passivering op μ eff worden bestudeerd.

Methoden

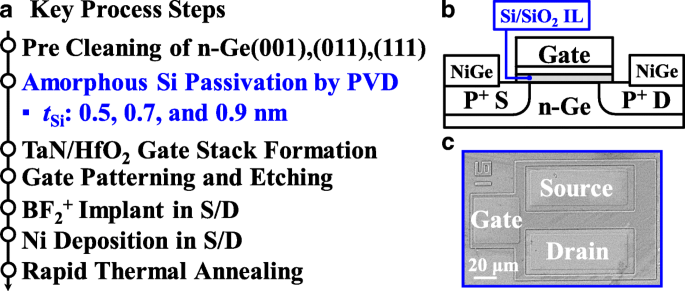

Figuur 1a toont de belangrijkste processtappen voor het fabriceren van Ge pMOSFET's op (001)-, (011)- en (111)-georiënteerde oppervlakken. Na pre-gate reiniging in verdunde HF (1:50) oplossing, werd een ultradunne amorfe Si-passiveringslaag afgezet op n-Ge-substraten door magnetronsputteren bij een doelvermogen van 50 W. Drie passiveringsduren van 60 s, 80 s en 100 s werden gebruikt die overeenkomen met de afzetting van 0,5, 0,7 en 0,9 nm t si , respectievelijk. Daarna een 5 nm dikke HfO2 gate-diëlektricum werd afgezet bij 250°C door atomaire laagafzetting met behulp van TDMAHf en H2 O als voorlopers van respectievelijk Hf en O. Een 50 nm TaN-poortelektrode werd afgezet door reactief sputteren. Vervolgens werd de poortelektrode van een patroon voorzien en geëtst, gevolgd door BF2 + implantatie in source/drain (S/D)-regio's bij 30 KeV met een dosis van 1 × 10 15 cm − 2 . Niet-zelf-uitgelijnde S/D-metalen van 15-nm nikkel werden gevormd door het lift-off-proces. Ten slotte werd snel thermisch gloeien bij 400 °C uitgevoerd voor doteringsactivering en S/D-metallisatie. Figuur 1b toont het dwarsdoorsnedeschema van de Ge pMOSFET met Si/SiO2 grenslaag (IL). Figuur 1c toont een microscoopbeeld in bovenaanzicht van een gefabriceerde Ge pMOSFET.

een Processequentie die de belangrijkste stappen toont die worden gebruikt om de Ge pMOSFET's te fabriceren met verschillende t Si . b Schema in dwarsdoorsnede van een Ge pMOSFET met SiO2 IL. c Microscoopopname van bovenaf van een gefabriceerde Ge pMOSFET

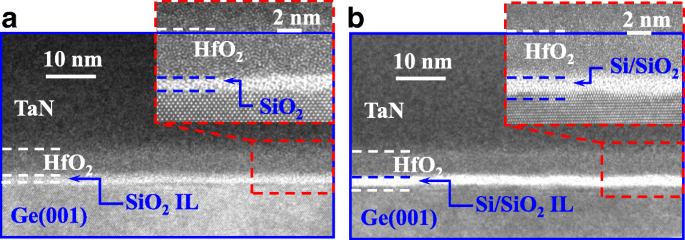

Figuur 2a, b toont de transmissie-elektronenmicroscoop (TEM) beelden van de high-κ/metal gate stack met SiO2 /Si-interfacelaag (IL) op Ge(001)-kanaal met t Si van respectievelijk 0,5 en 0,9 nm. Insets tonen de TEM (HRTEM) afbeeldingen met hoge resolutie van de monsters. Voor het apparaat met een t Si van 0,5 nm was de amorfe Si-laag volledig geoxideerd, terwijl voor het apparaat met 0,9 nm t Si , bleven er ongeveer twee Si-monolagen over na de daaropvolgende gloeistappen.

Transversale TEM-afbeeldingen van Ge pMOSFET-poortstapels met a 0,5 nm t Si en b 0.9 nm t Si . HRTEM-afbeeldingen in inzetstukken laten zien dat Si/SiO2 IL wordt gevormd tussen HfO2 en Ge-kanaal

Resultaten en discussie

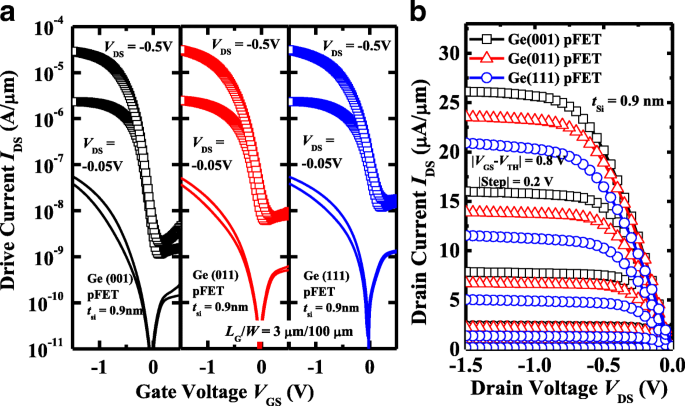

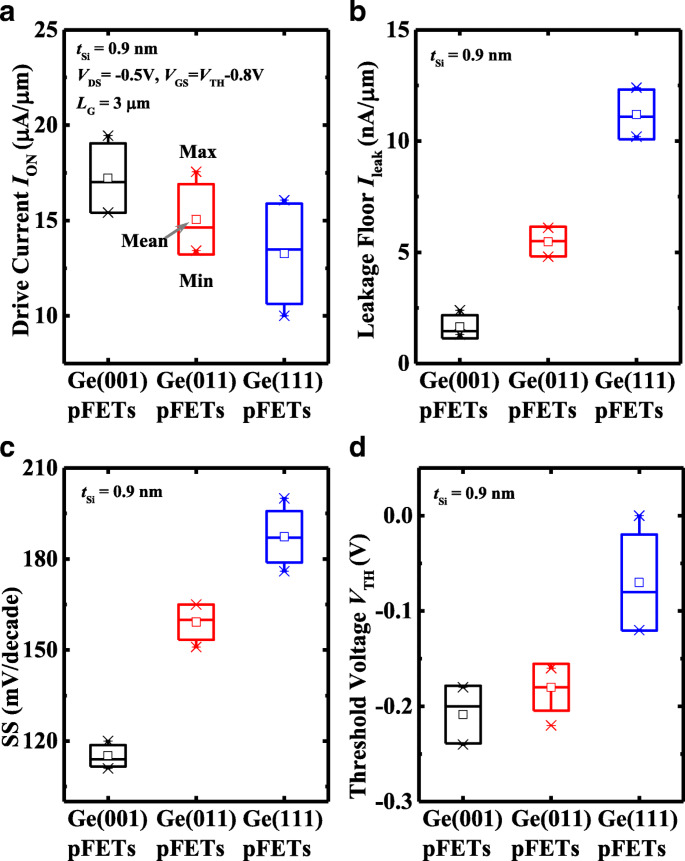

Figuur 3a geeft de gemeten I . weer DS -V GS en ik G -V GS krommen van de typische Ge pMOSFET's op (001)-, (011)- en (111)-georiënteerde oppervlakken met 0,9 nm t Si , die de uitstekende overdrachtseigenschappen vertonen. Alle transistors hebben een poortlengte L G van 3 μm en een poortbreedte W van 100 urn. De kanaalrichting is [110] voor alle oriëntaties. De ik DS -V DS curven van de apparaten gemeten bij verschillende gate overdrive V GS -V TH worden getoond in Fig. 3b. Hier, drempelspanning V TH wordt gedefinieerd als de V GS bij ik DS van 10 −7 A/μm. Het is waargenomen dat Ge(001) pMOSFET de hogere aandrijfstroom I . bereikt AAN vergeleken met de transistors op (011) en (111) oppervlakken op de vaste V GS -V TH . Later zullen we laten zien dat dit wordt toegeschreven aan het feit dat Ge(001) pMOSFET's een hogere effectieve gatenmobiliteit hebben μ eff in vergelijking met de apparaten op de andere twee oppervlakteoriëntaties. We voeren een uitgebreide vergelijking van elektrische prestaties uit voor de apparaten met de vaste t Si van 0,9 nm, inclusief I AAN , lekkage vloer I lek , subthreshold swing (SS) en V TH kenmerken. Ik lek wordt gedefinieerd als het minimum I DS bij V DS van − 0,05 V. Figuur 4a geeft de statistische grafiek weer van de I AAN voor Ge pMOSFET's op verschillende oriëntaties, en I AAN werd gedefinieerd als I DS op een V DS van − 0,5 V en een V GS -V TH van − 0,8 V. Alle transistors in deze plot hebben de L G van 3 μm en W van 100 urn. (001)-georiënteerde apparaten vertonen het verbeterde gemiddelde I AAN in vergelijking met die op (011) en (111) oriëntaties, wat wordt toegeschreven aan de hogere μ eff . Figuur 4b vergelijkt de I lek voor de apparaten, wat aantoont dat Ge(001)-transistors de laagste I . hebben lek van hen, en Ge(011) pMOSFET's hebben de lagere I lek dan (111)-georiënteerde apparaten. Opgemerkt moet worden dat de I lek wordt bepaald door de tegenstroom van de p + /n-junctie in het afvoergebied, dat wordt beïnvloed door de achtergrond-n-type dopingconcentratie in Ge-substraat en activering van de geïmplanteerde p + doteringen. De n-type doteringsconcentraties in de wafels met verschillende oriëntaties zijn niet exact gelijk. De oriëntatie van het oppervlak beïnvloedt de activeringssnelheid van het doteringsmiddel en de herkristallisatiekwaliteit van S/D-regio's. Bovendien, hoewel de I G is lager dan I DS vóór het inschakelen van de transistors, zou het de I . beïnvloeden lek . Evenzo demonstreren (001)-georiënteerde Ge pMOSFET's de verbeterde SS-karakteristieken in vergelijking met andere twee oriëntaties, wat te wijten is aan het feit dat transistors op (001) oppervlak de lagere midgap-dichtheid van interfacestatus D hebben het vergeleken met de andere apparaten. Afbeelding 4d laat zien dat de apparaten in verschillende oriëntaties de verschillende V . hebben TH . Op basis van de resultaten in Fig. 4 wordt geconcludeerd dat, met de vaste t Si van 0,9 nm verkrijgen (001)-georiënteerde Ge pMOSFET's de beste elektrische eigenschappen.

een Gemeten I DS -V GS en ik G -V GS krommen van (001)-, (011)- en (111)-georiënteerde Ge pMOSFET's met 0,9 nm t Si met de uitstekende overdrachtseigenschappen. b Ik DS -V DS krommen gemeten bij verschillende V GS -V TH voor de apparaten

Vergelijking van a Ik AAN , b Ik lek , c SS, en d V TH voor (001)-, (011)- en (111)-georiënteerde Ge pMOSFET's met een t Si van 0,9 nm

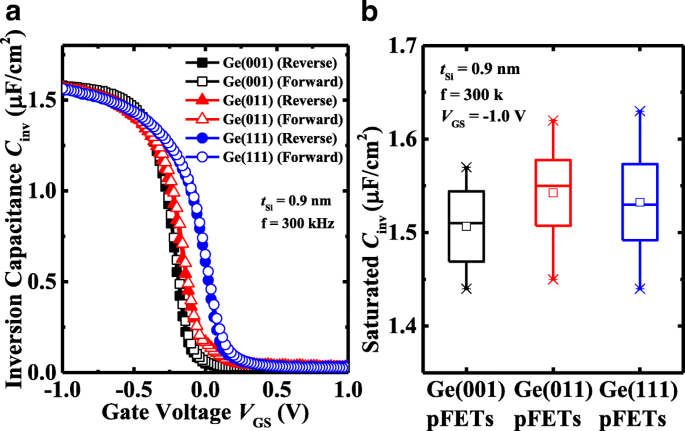

De diktes van Si/SiO2 IL in transistors met 0,9 nm t Si op verschillende oppervlakteoriëntaties worden bestudeerd met behulp van inversiecapaciteit C inv versus V GS meting, zoals weergegeven in Fig. 5. Voorwaartse en achterwaartse veegmetingen vertonen de verwaarloosbaar kleine hysterese in de apparaten. De transistors vertonen de vergelijkbare grootte van C inv , ~ 1.56 μF/cm 2 , overeenkomend met de capacitieve effectieve dikte (CET) van 2,2 nm. Figuur 5b toont de statistische resultaten van verzadigde C inv voor de apparaten, die het zeer kleine verschil in C . aantonen inv in de transistors op verschillende oppervlakteoriëntaties. Dit geeft aan dat de passiveringssnelheid van amorf Si door magnetronsputteren onafhankelijk is van de oppervlakteoriëntatie. De regel van links-rechts verschuivingen van de C inv -V GS curven komt goed overeen met die van V TH voor de apparaten in Fig. 4d, wat kan worden veroorzaakt door de enigszins verschillende dopingconcentratie in verschillende oriëntatiesubstraten.

een Vergelijking van inversie C inv -V GS krommen tussen de Ge pMOSFET's met 0,9 nm t Si op verschillende oriëntaties. Zowel voorwaarts als achterwaarts vegen wordt getoond. b Statistische grafieken voor de verzadigde C inv van de apparaten met de verwaarloosbare verschillen in C inv in het inversieregime

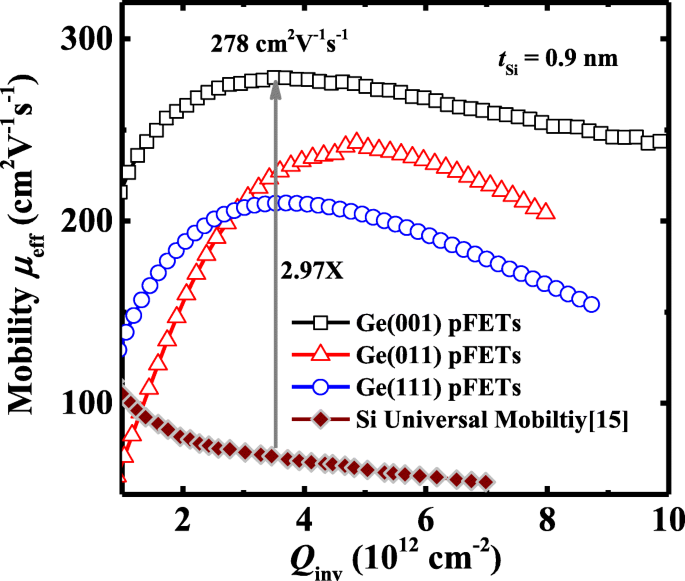

Figuur 6 vergelijkt de mobiliteitskenmerken van de transistors met 0,9 nm t Si op verschillende oppervlakteoriëntaties. De μ eff werd geëxtraheerd met behulp van een op de totale weerstand gebaseerde methode [14]. Ge(001) pMOSFET's vertonen een veel hogere kanaalmobiliteit in vergelijking met de apparaten op (011) en (111) oriëntaties. Transistors op (001) substraat bereiken een piek μ eff van 278 cm 2 /V·s bij een inversieladingsdichtheid Q inv van ~ 3.5 × 10 12 cm −2 , wat 2,97 keer hoger is dan de universele mobiliteit van Si. Oppervlakteruwheid bij het Si/Ge-grensvlak en dichtheid van grensvlaktoestanden (D het ) kan μ . beïnvloeden eff van de apparaten bij een hoge inversiedraaggolfdichtheid. Het is onwaarschijnlijk dat de commercieel gekochte Ge-wafels met verschillende oppervlakteoriëntaties het duidelijke verschil in oppervlakteruwheid hebben. Daarom wordt gespeculeerd dat de mobiliteitsverbetering in (001)-georiënteerde apparaten voornamelijk te wijten is aan verminderde dragerverstrooiing die wordt bijgedragen door interfacetoestanden. In dit werk evalueren we de midgap D het van de apparaten, en met de vaste t Si van 0,9 nm hebben de (001)-georiënteerde Ge pMOSFET's inderdaad de lagere midgap D het vergeleken met de andere oriëntaties.

Perceel van μ eff versus Q inv voor Ge pMOSFET's met 0,9 nm t Si op (001)-, (011)- en (111)-georiënteerde substraten. Ge(001) pMOSFET's bereiken de 2,97-voudige verbetering in μ eff op een Q inv van 3,5 × 10 12 cm −2 in vergelijking met de Si universele mobiliteit. De μ eff werd geëxtraheerd met behulp van een op totale weerstand gebaseerde methode [17]

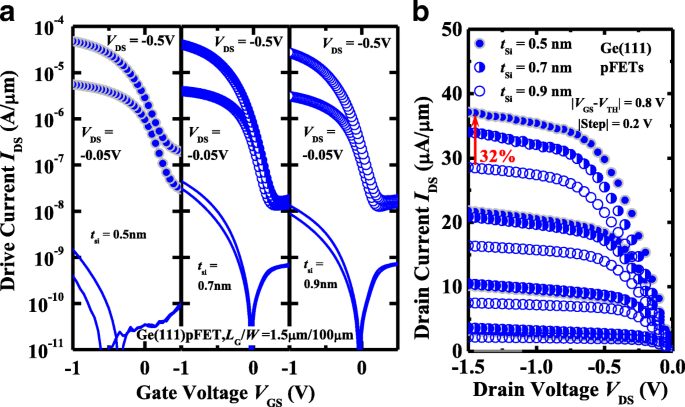

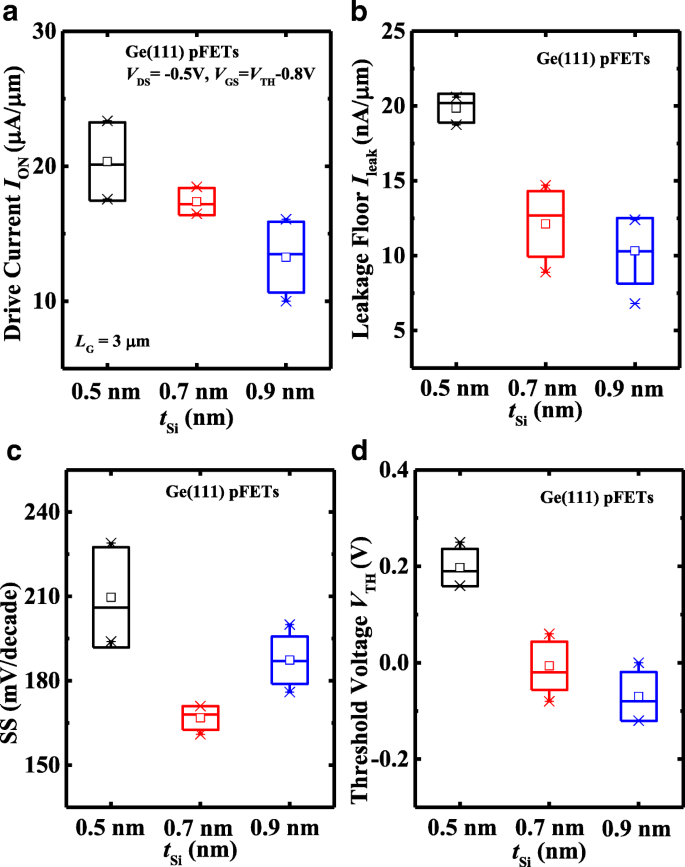

De impact van t Si op de elektrische prestaties van Ge pMOSFET's wordt ook onderzocht. Afbeelding 7a, b geeft de gemeten I . weer DS -V GS en ik DS -V DS curven van respectievelijk de (111)-georiënteerde Ge pMOSFET's met t Si van 0,5, 0,7 en 0,9 nm bij een V DS van − 0,05 en − 0,5 V. De transistors hebben een L G van 1,5 m. Er wordt waargenomen dat Ge pMOSFET's met 0,9 nm t Si vertonen verbeterde overdrachtskenmerken in vergelijking met de apparaten met dunnere t Si , maar ik AAN van het apparaat neemt af met het toenemen van t Si . Bij V DS van − 1,5 V en V GS -V TH van − 0,8 V, Ge(111) pMOSFET met 0,5 nm t Si toont een verbetering van 32% in I AAN vergeleken met het apparaat met 0,9 nm t Si . Figuur 8 plot de statistische resultaten van I AAN , ik lek , SS en V TH van de Ge pMOSFET's op (111)-oriëntatie met verschillende t Si . Uit Fig. 8a zien we dat transistors met 0,5 nm t Si bereik de verbeterde I AAN in vergelijking met de apparaten met dikkere t Si , wat te wijten is aan de transistor met 0,5 nm t Si die een kleinere CET heeft, wat leidt tot een hogere C inv . Het valt op dat ik lek neemt af met het toenemen van t Si (Fig. 8b), en transistors met 0,5 nm t Si heeft de inferieure SS-kenmerken dan die van de apparaten met een amorfe Si-passiveringslaag van 0,7 en 0,9 nm (figuur 8c). Dit kan te wijten zijn aan die transistors met 0,5 nm t Si met een hogere midgap D het . De relatie tussen SS en midgap D het van Ge pMOSFET kan worden uitgedrukt door SS = ln(10) ⋅ (kT /q) ⋅ [1 + (C het + C d )/C os ], waarbij C os , C d , en C het zijn respectievelijk oxidecapaciteit, capaciteit van de uitputtingslaag en capaciteit van interface-traps. C het kan worden berekend door q × D het , waren D het is de interface trap dichtheid. Hoewel transistor met 0,5 nm t Si heeft de grotere C os in vergelijking met de andere twee apparaten, is de hogere midgap D het kan leiden tot de inferieure SS voor de apparaten met de dikkere t Si . De oppervlaktepassivering heeft ook invloed op de I lek van afvoer naar bron. Met het vegen van V GS van positie naar negatief, gaat het kanaal over van accumulatiemodus naar inversiemodus. Als de D het hoog is, worden sommige punten in het kanaaloppervlak vastgezet door de interface-vallen en kunnen de lekpaden worden gevormd, waardoor I toeneemt lek van afvoer naar bron. Zoals getoond in Fig. 8d, tonen Ge(111) pMOSFET's de verschuiving van V TH naar min V GS richting met het verhogen van t Si , die wordt toegeschreven aan de verhoogde CET. Bovendien lijkt de dichtheid van vallen in de onderste helft van de bandgap toe te nemen voor de dunnere t Si , wat kan leiden tot de verschuiving van V TH [2].

een Ik DS -V GS en ik G -V GS en b Ik DS -V DS krommen van Ge(111) pMOSFET's met verschillende t Si . Transistor met 0,5 nm t Si vertoont een verbetering van 32% in I AAN vergeleken met het apparaat met 0,9 nm t Si bij V DS van − 1,5 V en V GS -V TH van − 0.8 V

Vergelijking van a Ik AAN , b Ik lek , c SS, en d V TH voor (111)-georiënteerde Ge pMOSFET's met 0,5, 0,7 en 0,9 nm t Si waaruit blijkt dat transistors met 0,5 nm t Si heb de betere ik AAN , maar erger SS en I lek kenmerken in vergelijking met apparaten met dikkere t Si

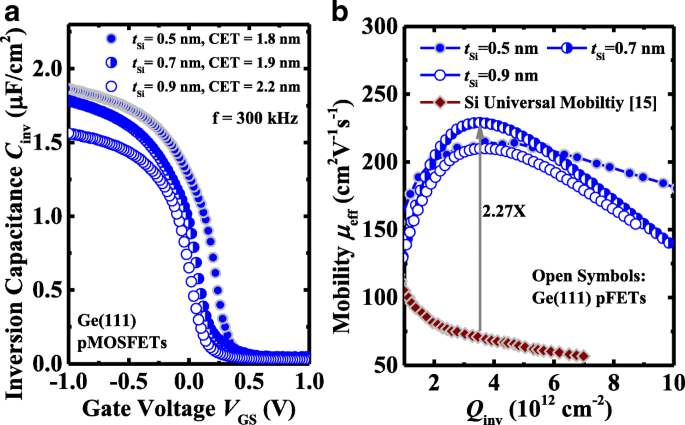

Afbeelding 9a toont de C inv als een functie van V GS krommen voor de Ge pMOSFET's op (111)-georiënteerd oppervlak met t Si van 0,5, 0,7 en 0,9 nm gemeten bij een frequentie van 300 kHz. De CET-waarden in inversiegebieden worden geëxtraheerd op 1,8, 1,9 en 2,2 nm voor de apparaten met 0,5, 0,7 en 0,9 nm t si , respectievelijk. μ eff als een functie van Q inv kenmerken van de apparaten worden geëxtraheerd en weergegeven in Fig. 9b. De (111)-georiënteerde Ge pMOSFET met 0,7 nm t si bereikt de hoogste piekmobiliteit van 229 cm 2 /V s, wat 2,27 keer hoger is in vergelijking met de universele Si-mobiliteit. Opgemerkt moet worden dat de apparaten met 0,5 nm t Si vertonen een aanzienlijk verbeterde μ eff over de transistors met dikkere t Si bij hoge Q inv (bijv. 10 13 cm −2 ). Dit leidt ook tot de hogere I AAN bij hoge V GS -V TH in de apparaten met 0,5 nm t Si vergeleken met de apparaten met 0.7 en 0.9 nm t Si . De μ eff bij hoge Q inv neemt af als t Si neemt toe van 0,5 nm tot 0,7 ~ 0,9 nm, wat wordt toegeschreven aan het feit dat de grotere oppervlakteruwheid leidt tot een sterkere oppervlakteruwheidsverstrooiing van de dragers. Tijdens de passivering van het Ge-oppervlak met behulp van magnetronsputteren bij kamertemperatuur, wordt de diffusie van oppervlakte-atomen sterk onderdrukt. Dus met het toenemen van t Si , is de oppervlakteruwheid groter, wat kan worden waargenomen aan de hand van de HRTEM-afbeeldingen in Fig. 2.

een C inv -V G kenmerken gemeten bij 300 kHz voor (111)-georiënteerde apparaten met 0,5, 0,7 en 0,9 nm t Si . b μ eff als een functie van Q inv voor Ge pMOSFET's [17]

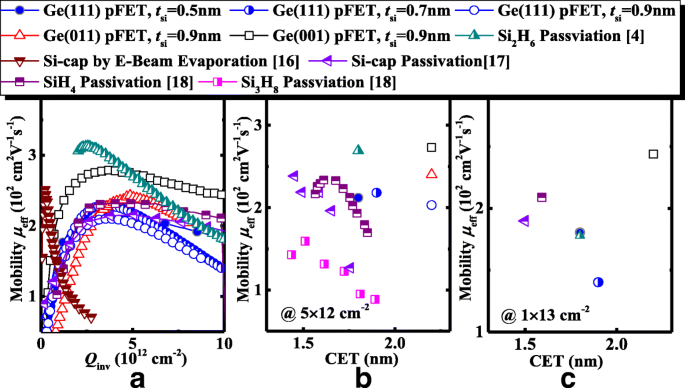

In Fig. 10 vergelijken we de μ eff van de Ge pMOSFET's in dit werk met die van de gerapporteerde ontspannen Ge-transistors met Si door E-beam-verdamping, SiH4 , Si2 H6, en Si3 H8 passivering. Vergeleken met het amorfe Si door E-beam-verdamping in Ref. [15], Ge pMOSFET's in dit werk vertonen de aanzienlijk verbeterde μ eff . Het is te zien dat, op vergelijkbare CET, Ge pMOSFET's die amorfe Si-passivering gebruiken door magnetronsputteren, de lagere μ hebben eff in vergelijking met de apparaten met Si2 H6 passivering. Het proces van passiveren met amorf Si moet verder worden geoptimaliseerd om de mobiliteit van de drager te verbeteren.

een μ eff voor de Ge pMOSFET's in dit werk versus de gepubliceerde resultaten voor ontspannen Ge pMOSFET's. b , c Benchmarking van μ eff geëxtraheerd op Q inv = 5 × 10 12 en 1 × 10 13 cm −2 respectievelijk van de Ge pMOSFET's met de verschillende CET-waarden [18, 19]

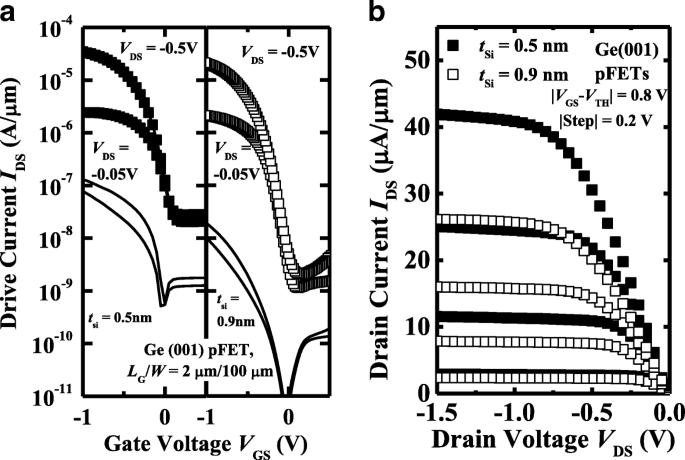

Ge pMOSFET's met de verschillende t Si op (001)-georiënteerd oppervlak worden ook gekenmerkt. Afbeelding 11a, b illustreren de gemeten I DS -V GS en ik DS -V DS krommen, respectievelijk, van een paar Ge(001) pMOSFET's met 0,5 en 0,9 nm t Si . Net als bij de (111)-georiënteerde apparaten, Ge(001) pMOSFET met 0,5 nm t Si verkrijgt de verbetering in I AAN maar de degradatie in I lek vergeleken met de transistor met 0,9 nm t Si .

een Gemeten I DS -V GS en ik G -V GS krommen van (001)-georiënteerde Ge pMOSFET's met 0,5 en 0,9 nm t Si . b Ik DS -V GS rondingen van de apparaten

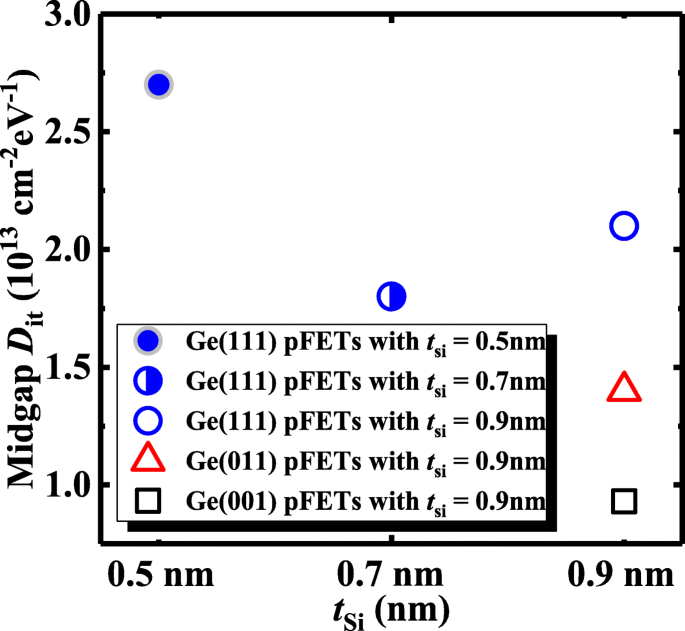

De middenopening D het kenmerken van Ge pMOSFET's worden bestudeerd met de methode in [16], en waarden van D het worden berekend door D het = [SSlog(e)/(kT /q ) − 1]C G /q , [16] waar q is de elektronenlading, k is de constante van Boltzmann, T is de absolute temperatuur, en C G is de gemeten poortcapaciteit per oppervlakte-eenheid. Afbeelding 12 toont D het als functie van de dikte van amorf Si met verschillende Ge-oppervlakteoriëntaties. Voor (111)-georiënteerd oppervlak, een apparaat met 0,7-nm t si heeft de laagste D het waarde. Met de 0,9 nm t Si , (001)-georiënteerd apparaat heeft de lagere D het vergeleken met de transistors op andere oriëntaties.

D het versus de dikte van amorf Si met verschillende Ge-oppervlakteoriëntaties

Ten slotte vergelijken we de belangrijkste elektrische kenmerken van Ge pMOSFET's op de verschillende oriëntaties in Tabel 1. Met een vaste t Si , Ge(001) pMOSFET heeft de verbeterde elektrische prestaties in vergelijking met de andere twee oriëntaties. De aandrijfstroom kan worden verbeterd door de t . te verminderen Si van 0,9 nm tot 0,5 nm, wat te wijten is aan de dunnere t Si biedt een aanzienlijk verminderde CET zonder degradatie in μ . te veroorzaken eff .

Conclusies

Ge pMOSFET gepassiveerd door amorf Si worden gedemonstreerd op (001)-, (011)- en (111)-georiënteerd substraat. Met een t Si van 0,9 nm, de verbeterde I AAN en SS-kenmerken worden verkregen in (001)-georiënteerde Ge pMOSFET's in vergelijking met de apparaten op (011) en (111) oriëntaties, vanwege de hogere μ eff en lagere midgap D het . Ge(001) pMOSFET's met 0,9 nm t Si bereik een maximale mobiliteit van 278 cm 2 /V s op een Q inv van 3,5 × 10 12 cm −2 , wat 2,97 keer hoger is dan de universele mobiliteit van Si. Het is aangetoond dat ik AAN van de apparaten is verbeterd met het verlagen van t Si vanwege de verlaging van de CET. Maar Ge pMOSFET's met dikkere t Si vertonen de superieure subthreshold swing en lekvloer, dankzij die midgap D het kan worden verminderd door t . te vergroten Si .

Afkortingen

- ALD:

-

Atoomlaagafzetting

- BF2 + :

-

Boorfluoride-ion

- CET:

-

Capacitieve effectieve dikte

- Ge:

-

Germanium

- GeOx :

-

Germaniumoxide

- HF:

-

Fluorwaterstofzuur

- HfO2 :

-

Hafniumdioxide

- HRTEM:

-

Transmissie-elektronenmicroscoop met hoge resolutie

- IL:

-

Tussenlaag

- MOSFET's:

-

Metaaloxide-halfgeleider veldeffecttransistoren

- Ni:

-

Nikkel

- Si:

-

Silicium

- SS:

-

Subdrempelzwaai

- TaN:

-

Tantaalnitride

- TDMAHf:

-

Tetrakis (dimethylamido) hafnium

Nanomaterialen

- KUHMUTE herontwerpt mobiliteit met SLS 3D Printing

- 3D-printen met hoge snelheid met AFPM

- 3D-printen met hoge snelheid met AION500MK3

- Hoge prestaties van PEDOT:PSS/n-Si-zonnecellen op basis van een gestructureerd oppervlak met AgNWs-elektroden

- Polarisatieconverter met regelbare dubbele breking op basis van hybride volledig diëlektrisch grafeenmetasurface

- Hoge prestatie organisch-nanogestructureerde silicium hybride zonnecel met aangepaste oppervlaktestructuur

- Een nanoschaal low-power weerstandloze spanningsreferentie met hoge PSRR

- ZnO poreuze nanoplaten met gedeeltelijke oppervlaktemodificatie voor verbeterde ladingsscheiding en hoge fotokatalytische activiteit onder zonnestraling

- Ge pMOSFET's met GeOx-passivering gevormd door ozon en plasma postoxidatie

- Nieuwe inzichten over factoren die het vervoer van vervoerders beperken in zeer dunne, amorfe Sn-gedoteerde In2O3-films met hoge zaalmobiliteit

- High Mobility Ge pMOSFET's met ZrO2-diëlektricum:effecten van nagloeien