Een 100-Mhz bandbreedte 80-dB dynamisch bereik continue Delta-Sigma modulator met een 2,4-Ghz kloksnelheid

Abstract

De bandbreedte van een Δ Σ modulator wordt beperkt door de kloksnelheid vanwege de vereiste overbemonsteringsverhouding. Aangezien de CMOS-processen op nanoschaal zich snel ontwikkelen, is het mogelijk om een grote bandbreedte en een continue tijd met een hoog dynamisch bereik te ontwerpen Δ Σ modulatoren voor hoogfrequente toepassingen. Dit artikel stelt een 3e-orde 4-bits continue tijd Δ . voor Σ modulator met een single-loop feedforward topologie. Deze modulator is ontworpen in een 40 nm CMOS-proces en bereikt een dynamisch bereik van 80 dB en een bandbreedte van 100 MHz bij een kloksnelheid van 2,4 GHz. De modulator verbruikt 69,7 mW van een 1,2 V-voeding.

Inleiding

Gedreven door de toenemende vraag naar draadloze communicatietoepassingen zoals cellulaire standaarden, evolueren analoog-naar-digitaalomzetters (ADC's) snel om hogere signaalbandbreedte (BW) en dynamisch bereik (DR) te ondersteunen. De eis van BW in de communicatiestandaard Long-Term-Evolution Advanced (LTE-A) is gestegen tot 100 MHz. Nyquist ADC's, typisch pijplijn-ADC's [1, 2], zijn gebruikt in macrobasisstations vanwege hun hoge BW. Onmisbare ingangsbuffers voor het aansturen van thermische ruisbegrensde geschakelde ingangscondensatoren en anti-aliasingfilters veroorzaken echter een aanzienlijk stroomverbruik en ontwerpcomplexiteit. Bovendien leidt het feit dat pijplijn-ADC's afhankelijk zijn van nauwkeurige versterking tussen de fasen, die de high-gain breedbandresiduversterker en kalibratietechnologie bepaalt, tot complexiteit en vermogensdissipatie. Δ Σ ADC's staan bekend om hun hoge prestaties en energie-efficiëntie door gebruik te maken van oversampling- en ruisvormende technologie. De vereiste van oversampling-ratio's (OSR's), die doorgaans hoger zijn dan 16 [3-6], bepaalt echter de bemonsteringsfrequentie buiten GHz. Onlangs, Δ Σ ADC's van meer dan 50 MHz BW zijn voorgesteld met behulp van CMOS-processen op nanoschaal, die een kloksnelheid van meerdere GHz mogelijk maken. Eerder hoge frequentie Δ Σ ADC's gebruiken meestal continue-tijd (CT) realisaties [3-9] in plaats van discrete-tijd (DT) realisaties. Dit laatste wordt geïmplementeerd door een geschakeld condensatorcircuit en de nauwkeurigheid ervan is afhankelijk van condensatoraanpassing, wat betekent dat een robuuste werking onder procesvariatie wordt aangeboden. Bovendien wordt een superieure immuniteit tegen klokjitter verschaft, aangezien de tijdconstanten van de condensatoren en schakelaars voldoende klein zijn. Omdat de bemonsteringsbewerking echter vóór de modulator wordt uitgevoerd, is het anti-aliasingfilter nodig. Aan de andere kant worden operationele versterkers in DT-modulatoren, vanwege de afwikkelingsvereiste om stabiliteit in de trappen te garanderen, geïmplementeerd met een bredere eenheidsversterkingsbandbreedte (UGBW) dan CT-modulators. Samenvattend kunnen DT-modulators een zeer nauwkeurig maar smal signaal leveren [10, 11] en worden ze veel gebruikt voor het implementeren van meettoepassingen zoals slimme sensoren en biomedische beeldvorming. Daarentegen zijn er meer inspanningen geleverd om CT-modulatoren te ontwerpen voor hoogfrequente toepassingen dan DT-modulators met vergelijkbare complexiteit en stroomverbruik.

Het veeleisende ontwerpdoel van een hogere BW in een bepaald proces bepaalt een lagere OSR vanwege de procesbeperkte kloksnelheid. Om een voldoende DR te bereiken, is een agressieve ruisvorming vereist die wordt geïmplementeerd door een hoge ruisoverdrachtsfunctie-volgorde, die conventioneel wordt uitgevoerd door lusfiltercascade en in het algemeen gelijk aan of groter is dan 3 in eerdere werken. De toegenomen volgorde van lusfilters veroorzaakt echter stroomverbruik, instabiliteit en ontwerpcomplexiteit. De meertraps noise-shaping (MASH) architectuur [6, 8], geïmplementeerd door gecascadeerde lage-orde lokale Δ Σ modulatoren zonder feedbackpad onder elkaar, werd gebruikt om stabiliteitsproblemen te verlichten, maar met een mismatch-gevoeligheid. Bovendien krijgt een modulator met een multi-bits quantizer een voorwaardelijk hoge DR met een exponentieel toenemende comparatorhoeveelheid.

Dit artikel beschrijft een CT-modulator in 40 nm CMOS die 80 DR over 100 MHz BW bereikt met een verbruik van 69,7 mW met behulp van een 40 nm CMOS-proces. Dit blad is als volgt ingedeeld. De sectie "Methode" beschrijft de modulatortopologie en circuitimplementatie. De sectie "Resultaten en discussie" toont gesimuleerde resultaten en de sectie "Conclusie" geeft een samenvatting van dit werk.

Methode

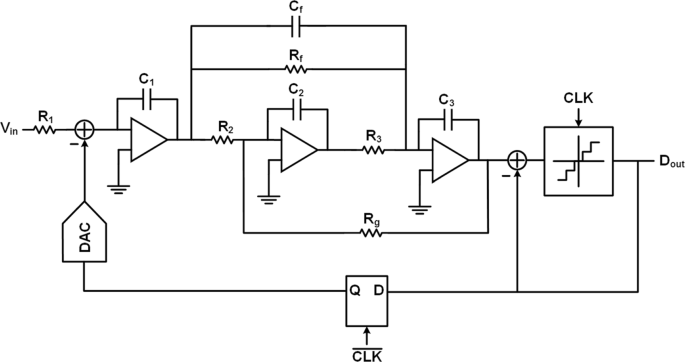

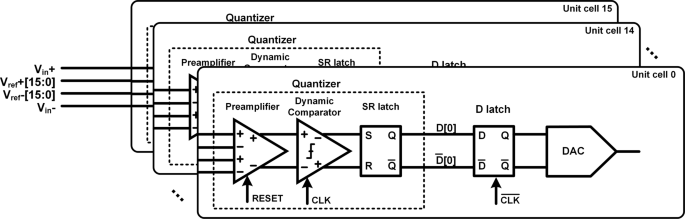

Figuur 1 illustreert het algemene schema van de voorgestelde 3e-orde CT Δ Σ modulator met de single-ended structuur voor vereenvoudiging. De 3e-orde ruisvorming zorgt voor een geweldig compromis tussen de DR en de lusstabiliteit. De voorgestelde modulator heeft een bemonsteringsfrequentie van 2,4 GHz met een 12 OSR. De relatief hoge OSR in Δ Σ modulatoren van meer dan 100 MHz BW zorgen voor een hoge DR. De modulator bevat drie RC-integrators, een 4-bits quantizer en een 4-bit stroomgestuurde DAC. De integrators worden geïmplementeerd door innovatieve feedforward-versterkers met laag vermogen voor hoge energie-efficiëntie. De feedback-DAC heeft een extra vertraging van een halve bemonsteringsperiode om de metastabiliteitseis van de kwantiseerder te versoepelen. Een snel feedbackpad geïmplementeerd door een passieve opteller en direct aangestuurd door de kwantiseerder realiseert de overmatige lus-vertraging (ELD) compensatie. Er wordt een feedforward-topologie gebruikt voor energie-efficiëntie ten koste van de out-of-band signaaloverdrachtsfunctie.

Algemeen schema van voorgestelde single-loop 3e-orde 4-bit CT Δ Σ modulator met een feedforward-topologie

Versterkerontwerp

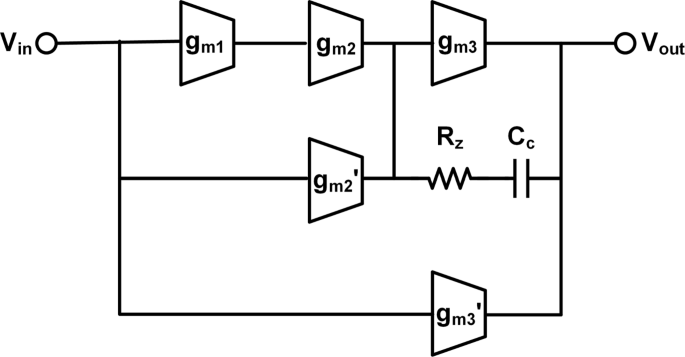

Hoge versterkerversterking is vereist in Δ Σ modulatoren om de gewenste ruistransformatiefunctie te garanderen. De technologieën op nanoschaal die worden gebruikt om een kloksnelheid van meerdere GHz te bereiken, hebben echter te lijden van een lage intrinsieke versterking. Daarom wordt een drietrapsversterker gebruikt om voldoende DC-versterking te implementeren, zoals weergegeven in Fig. 2. Feedforward-topologie en Miller-compensatie worden gecombineerd om de fasemarge te verbeteren zonder vermindering van de bandbreedte van de eenheidsversterking. Feedforward-versterkers zijn een populaire oplossing geweest voor het bereiken van hoge winst met voldoende UGBW en fasemarge (PM). Het linker halve vlak nul veroorzaakt door het voorwaartse pad wordt verondersteld de negatieve faseverschuiving van polen effectief te annuleren. Het vereist een hoge transconductantie van de versterkers op het voorwaartse pad en verbruikt veel stroom. Het voordelige schema van het hergebruiken van biasstroom bespaart energie terwijl het g . beperkt m waarden. Onvoldoende g m veroorzaakt meestal de nul voorbij de UGBW en kan geen adequate fasemarge bieden. Een geoptimaliseerd nulpunt onder de totale UGBW wordt verkregen door een Miller-compensatiecondensator en een nulweerstand toe te voegen.

Topologie van de voorgestelde drietraps feedforward-versterker met Miller-compensatie

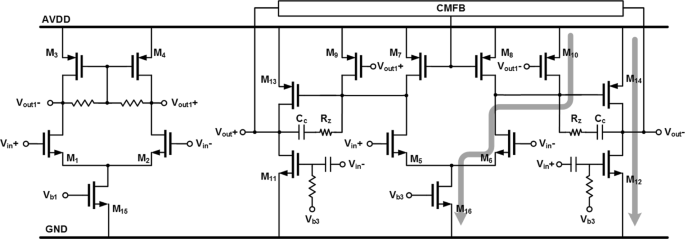

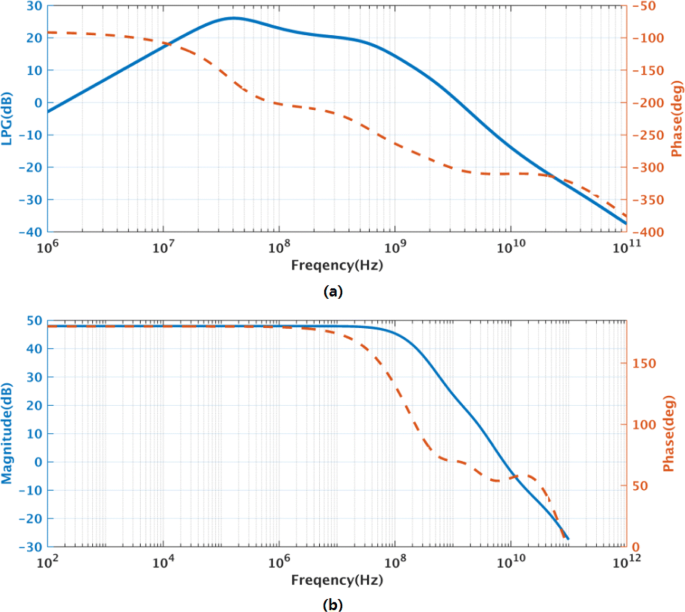

Figuur 3 toont het schema op transistorniveau van de versterker die in de eerste integrator wordt gebruikt. Transistors M 1−4 vormen de ingangstrap van de versterker, terwijl transistoren M 9,10 en M 13,14 vormen respectievelijk de tweede en de derde fase. Transistors M 5−8 en M 11,12 creëer twee snelle feedforward-paden tussen de input en output terwijl de biasstromen worden gedeeld met de versterkers van de tweede en derde trap. De common-mode (CM)-uitgang van de eerste trap wordt lokaal vastgesteld. De output CM van de tweede trap en de 3e trap wordt bepaald door een feedbackpad van de tweede trap over een CMFB-versterker, M 7,8 en M 13,14 . Figuur 4a toont de gesimuleerde open-lusrespons na de lay-out van de versterker van de eerste integrator met alle belasting, terwijl figuur 4b de close-lusrespons toont. De eerste integrator haalt 3,6 GHz UGBW en 57,8 ∘ van PM met alle laden effect terwijl verbruikt 10,5 mW van een 1,2-V voeding. De tweede en derde integrators gebruiken dezelfde topologie, maar met geschaalde biasstromen, waardoor UGBW van 4,7 en 3,3 GHz en PM van 58,0 en 57,8 wordt bereikt ∘ terwijl ze respectievelijk 4,3 en 17,3 mW verbruiken.

Schema op transistorniveau van de versterker

De post-layout gesimuleerde resultaten van de versterker in de 1e integrator. een Open-loop AC-respons; b Close-loop ac-reactie

Quantizer en DAC

Zoals het schema van de kwantiseerder en DAC getoond in Fig. 5, bestaat elk uit 16 eenheidscellen. De quantizer wordt gerealiseerd als 4-bits flash-ADC's met 16-niveaus encoder gegenereerd op basis van een resistieve ladder met 17 tikken. De quantizer, waarvan de werkingsduur door ELD wordt geëist tot minder dan een halve bemonsteringsperiode om de stabiliteit van de lus te garanderen, is een sleutelblok als een beperking van de maximale BW.

Het vereenvoudigde schema van de quantizers en de DAC's

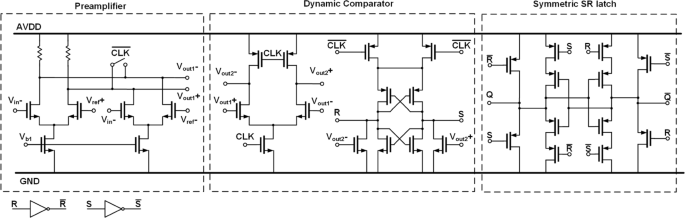

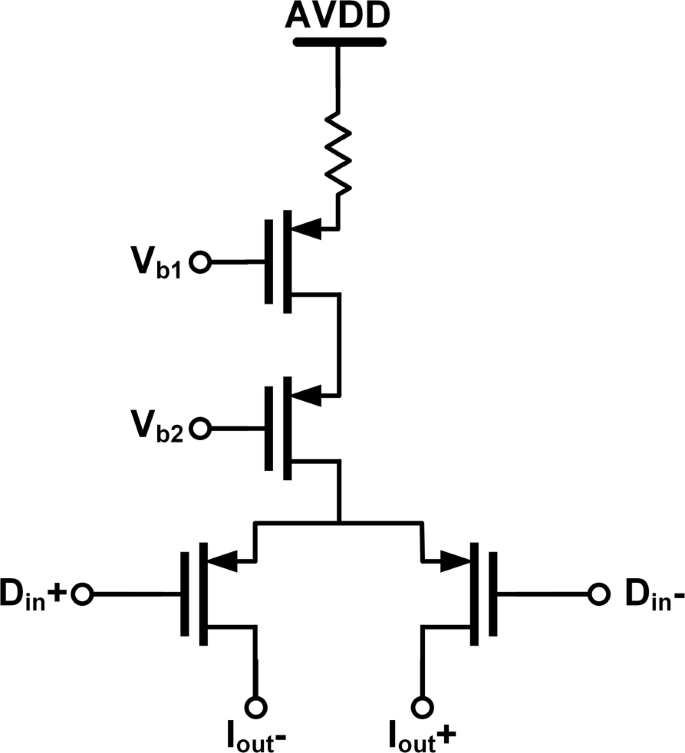

Om high-speed flash-ADC's te implementeren, wordt een drietraps comparatorarchitectuur gebruikt, bestaande uit een voorversterkertrap, een dynamische comparatortrap en een symmetrische set-and-reset (SR) vergrendeling [12], geïllustreerd als Fig. 6, wordt gebruikt. De voorversterker voor ingangsafhankelijke offsetreductie is twee resistief belaste differentiële paren met een resetschakelaar die over de uitgangen is aangesloten om snel herstel mogelijk te maken. In tegenstelling tot conventionele dynamische comparatoren, zijn het differentiële paar en kruisgekoppelde omvormers in twee delen gesplitst om de hoeveelheid transistor in elk stroompad voor laagspanningsvoedingen te minimaliseren. Wanneer de klok naar het hoge niveau draait, beginnen dynamische comparatoren de ingangsafhankelijke vergelijkingsbeslissing te nemen. Vervolgens worden de twee uitgangen van elke dynamische comparator beide teruggezet naar 0 wanneer de klokretour van hoog naar laag gaat, waardoor de regeneratie en vergrendeling van de symmetrische SR-latch wordt geactiveerd. Aangezien slechts één transistor in elke tak actief is, leidt de symmetrische SR-grendelstructuur tot een sterk laadaanstuurvermogen. Het maakt een kleine transistorgrootte mogelijk met een aanzienlijke uitschakelsnelheid en een laag stroomverbruik. Bovendien resulteert het in gelijke vertragingen van beide uitgangssignalen. De D-latches voor DAC-eenheden zijn laag-niveaugevoelig met betrekking tot het niveau van het kloksignaal, waardoor een halve ELD-duur wordt gegarandeerd. Het circuit op transistorniveau van de stroomgestuurde DAC-eenheid wordt getoond in Fig. 7.

Circuit op transistorniveau van één eenheidselement van de voorgestelde kwantiseerder

Het PMOS-stroombesturings-DAC-eenheidselement

Resultaten en discussie

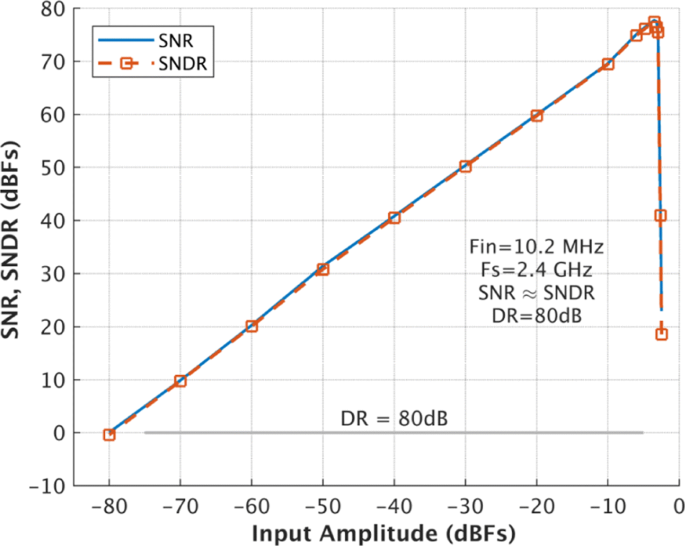

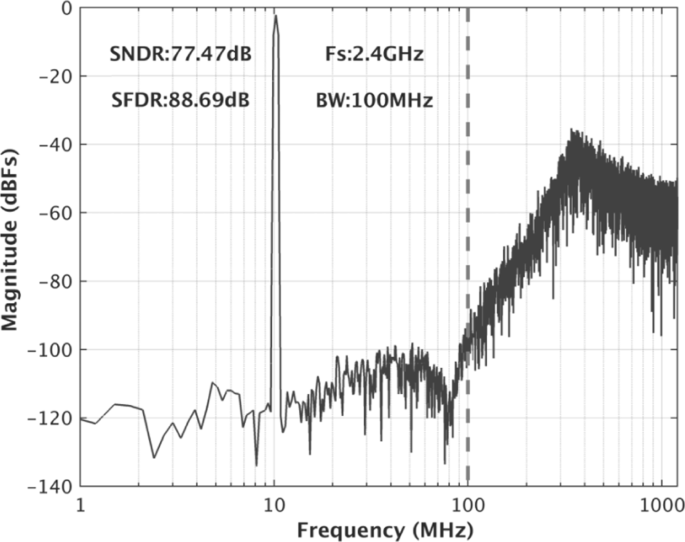

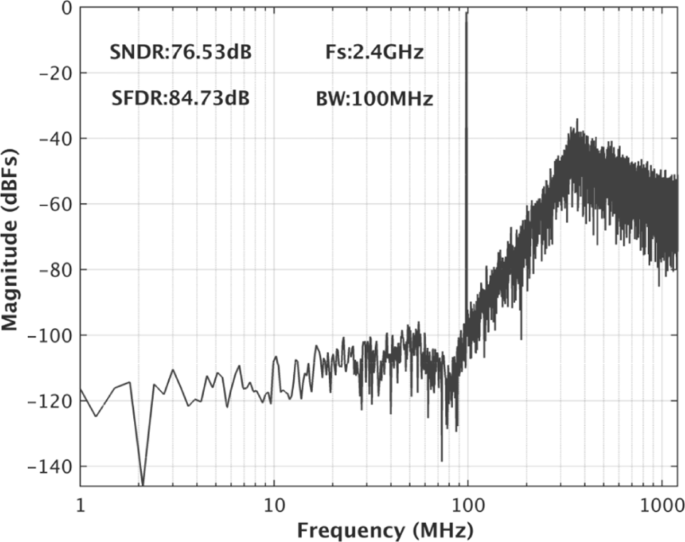

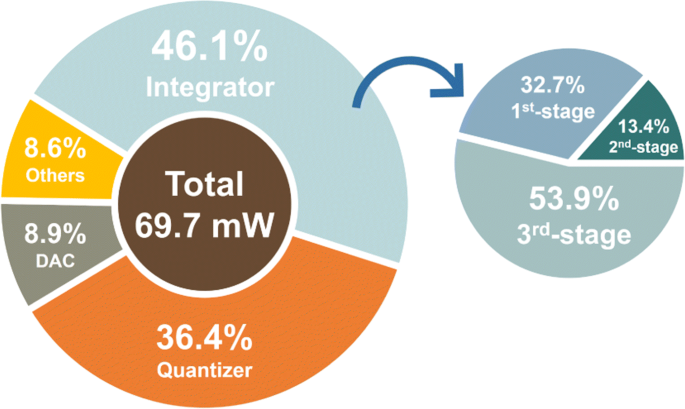

Het prototype Δ Σ modulator is gebouwd in een 40-nm CMOS-proces. Als de post-gesimuleerde resultaten van de SNR en SDNR vs. ingangsamplitude bij 10,2 MHz getoond in Fig. 8, wordt een 80-dB DR bereikt. Figuren 9 en 10 tonen de gesimuleerde spectra met een − 3,52-dBF eentonige ingang bij respectievelijk 10,2 MHz en 97 MHz, aangezien 0 dBF overeenkomt met de volledige schaal van de 2,4 Vpp-modulator. De SNDR is respectievelijk 77,47 dB en 76,53 dB. Zoals het doorslagverbruik weergegeven in Fig. 11, kost de modulator 69,7 mW stroomverbruik. De integrator, de quantizer en de DAC verbruiken respectievelijk 32,1 mW, 25,4 mW en 6,2 mW. 6,0 mW vermogen wordt verbruikt door de andere stromen, inclusief klokbuffers, stroomvoorspanningen en de spanningsreferenties. De modulator behaalt een Schreier FOM van 171,6 dB op basis van DR. Tabel 1 vergelijkt dit werk met verschillende eerder gepubliceerde werken. De voorgestelde modulator bereikt een breed BW met de hoogste FOM.

Post-gesimuleerde SNR en SNDR vs. ingangssignaalamplitude met een 10,2-MHz ingang

De post-gesimuleerde spectra met een single-tone input op 10,2 MHz

De post-gesimuleerde spectra met een single-tone input op 97 MHz

De post-gesimuleerde uitsplitsing van het stroomverbruik

Conclusie

In dit werk hebben we een 3e-orde 4-bit CT voorgesteld Δ Σ modulator met een single-loop feedforward topologie. Deze modulator is ontworpen in een 40-nm CMOS-proces en bereikt 80 dB DR over een 100-MHz BW met een kloksnelheid van 2,4 GHz. De constructie van de low-power dissipatieversterker leidt tot een hoge energie-efficiëntie, en de modulator verbruikt 69,7 mw van een 1,2 V-voeding en bereikt een Schreier FOM van 171,6 dB.

Beschikbaarheid van gegevens en materialen

Alle gegevens die tijdens dit onderzoek zijn gegenereerd of geanalyseerd, zijn opgenomen in dit gepubliceerde artikel.

Afkortingen

- ADC:

-

Analoog-naar-digitaal converters

- BW:

-

Bandbreedte

- CT:

-

Continu-tijd

- DR:

-

Dynamisch bereik

- DT:

-

Discrete tijd

- ELD:

-

Overmatige lusvertraging

- LTE-A:

-

Geavanceerde langetermijnevolutie

- OSR:

-

Overbemonsteringsverhoudingen

- PM:

-

Fasemarge

- UGBW:

-

Unity-gain bandbreedte

Nanomaterialen

- DIY eenvoudigste IV9 Numitron-klok met Arduino

- 3D-printen met hoge snelheid met AION500MK3

- Volledige Terahertz-polarisatiecontrole met verbrede bandbreedte via diëlektrische metasurfaces

- Vervaardiging van putten op nanoschaal met hoge doorvoer op dunne polymeerfilm met behulp van AFM-tipgebaseerde dynamische ploeglithografie

- RGO en driedimensionale grafeennetwerken hebben TIM's samen gemodificeerd met hoge prestaties

- Grafeen/polyaniline-aerogel met superelasticiteit en hoge capaciteit als zeer compressietolerante supercondensatorelektrode

- Polarisatieconverter met regelbare dubbele breking op basis van hybride volledig diëlektrisch grafeenmetasurface

- Hoge prestatie organisch-nanogestructureerde silicium hybride zonnecel met aangepaste oppervlaktestructuur

- De extreem verbeterde fotostroomrespons in topologische isolator-nanoplaten met hoge geleiding

- Multifunctioneel apparaat met schakelbare functies voor absorptie en polarisatieconversie op Terahertz-bereik

- Een nanoschaal low-power weerstandloze spanningsreferentie met hoge PSRR