Hardwaregedrag kan niet worden geïmplementeerd zonder voorwaardelijke instructies en andere manieren om de stroom van logica te beheersen. Verilog heeft een reeks controlestroomblokken en mechanismen om hetzelfde te bereiken. if-else-if Deze voorwaardelijke verklaring wordt gebruikt om een beslis

Blokkeren Blokkeren toewijzingsinstructies worden toegewezen met behulp van = en worden na elkaar uitgevoerd in een procedureel blok. Dit verhindert echter niet de uitvoering van opgaven die in een parallel blok lopen. module tb; reg [7:0] a, b, c, d, e; initial begin a = 8hDA;

Het plaatsen van waarden op netten en variabelen worden toewijzingen genoemd. Er zijn drie basisvormen: Procedureel Continu Procedureel doorlopend Juridische LHS-waarden Een opdracht bestaat uit twee delen - rechterkant (RHS) en linkerkant (LHS) met een gelijk-symbool (=) of een minder dan-gelijk-

Er zijn manieren om een set instructies te groeperen die syntactisch equivalent zijn aan een enkele instructie en die bekend staan als blokinstructies . Er zijn twee soorten blokinstructies:sequentieel en parallel. Opeenvolgend Verklaringen worden verpakt met begin en end trefwoorden en worden

Een eerder voorbeeld onderzocht een eenvoudige sequentiedetector. Hier is nog een voorbeeld van een patroondetector die een iets langer patroon detecteert. Ontwerp module det_110101 ( input clk, input rstn, input in, output out );

Een veelvoorkomend voorbeeld van een FSM is die van een sequentiedetector waarbij het hardwareontwerp naar verwachting detecteert wanneer een vast patroon wordt gezien in een stroom binaire bits die erin worden ingevoerd. Voorbeeld module det_1011 ( input clk, input rstn,

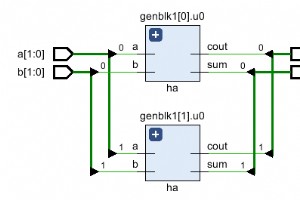

Een generate block maakt het mogelijk om module-instanties te vermenigvuldigen of voorwaardelijke instantie van een module uit te voeren. Het biedt de mogelijkheid om het ontwerp te bouwen op basis van Verilog-parameters. Deze instructies zijn met name handig wanneer dezelfde bewerking of module-ins

Alle gedragscode is geschreven in module en endmodule . Dus welk digitaal ontwerp je ook wilt maken, het past in een module blok. Het kan al dan niet poorten hebben gedefinieerd - laat signalen het blok binnenkomen als input of ontsnap aan het blok als output . Module De lege module in het ondersta

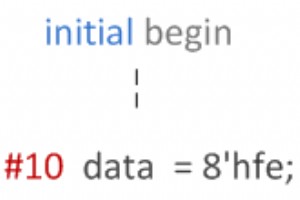

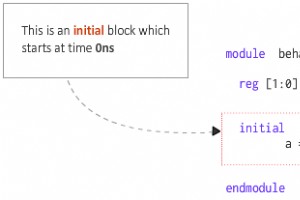

Een set Verilog-instructies wordt meestal achter elkaar uitgevoerd in een simulatie. Deze verklaringen zijn geplaatst in een procedurele blok. Er zijn hoofdzakelijk twee soorten procedurele blokken in Verilog - initieel en altijd Syntaxis initial [single statement] initial begin [multi

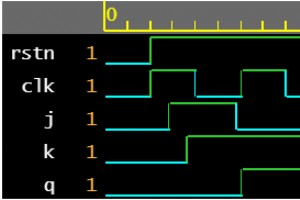

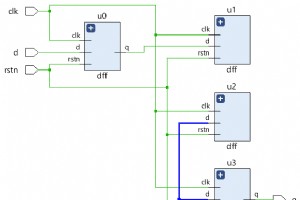

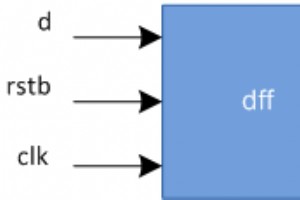

Een vorig artikel toonde verschillende voorbeelden van het gebruik van een always blok om combinatorische logica te implementeren. Een always blok wordt ook voornamelijk gebruikt om sequentiële . te implementeren logica met geheugenelementen zoals flip-flops die waarden kunnen bevatten. JK-teenslipp

Het verilog always-blok kan worden gebruikt voor zowel sequentiële als combinatorische logica. Een paar ontwerpvoorbeelden werden getoond met een assign uitspraak in een vorig artikel. Dezelfde reeks ontwerpen zal vervolgens worden onderzocht met behulp van een always blok. Voorbeeld #1:Eenvoudige c

Een always blok is een van de procedurele blokken in Verilog. Statements binnen een always-blok worden opeenvolgend uitgevoerd. Syntaxis always @ (event) [statement] always @ (event) begin [multiple statements] end De always blok wordt uitgevoerd bij een bepaalde gebeurtenis. De gebeurt

Multi-bit Verilog-draden en -variabelen kunnen met behulp van aaneenschakeling worden samengevoegd om een grotere multi-netdraad of variabele te vormen operators { en } gescheiden door commas. Aaneenschakeling mag naast draden en variabelen ook uitdrukkingen en grootteconstanten als operanden hebb

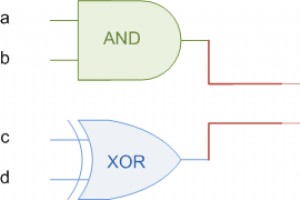

Gegevens die niet kunnen worden verwerkt, zijn vrij nutteloos, er zal altijd een vorm van berekening nodig zijn in digitale circuits en computersystemen. Laten we eens kijken naar enkele van de operators in Verilog waarmee synthesetools geschikte hardware-elementen kunnen realiseren. Verilog rekenku

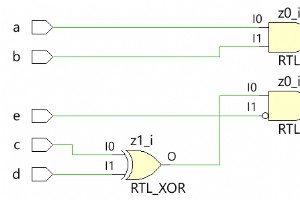

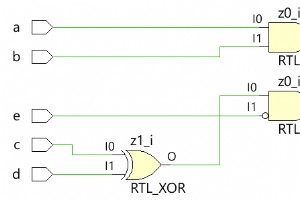

De verilog assign-instructie wordt meestal gebruikt om continu een signaal van wire . te sturen datatype en wordt gesynthetiseerd als combinatorische logica. Hier zijn nog enkele ontwerpvoorbeelden met de assign verklaring. Voorbeeld #1:Eenvoudige combinatorische logica De onderstaande code impleme

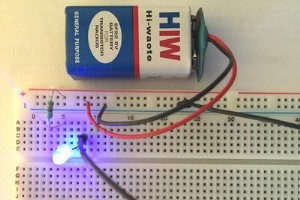

Signalen van het type wire of een soortgelijk draadachtig gegevenstype vereist de continue toewijzing van een waarde. Denk bijvoorbeeld aan een elektrische draad die wordt gebruikt om stukken op een breadboard met elkaar te verbinden. Zolang de +5V-batterij op het ene uiteinde van de draad is aanges

Zoals we in een vorig artikel zagen, worden grotere en complexere ontwerpen gebouwd door meerdere modules op een hiërarchische manier te integreren. Modules kunnen worden geïnstantieerd binnen andere modules en poorten van deze instanties kan worden verbonden met andere signalen in de oudermodule.

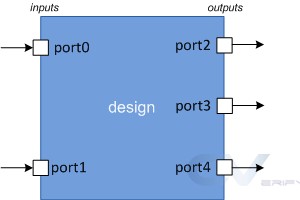

Poorten zijn een reeks signalen die fungeren als in- en uitgangen voor een bepaalde module en zijn de primaire manier om ermee te communiceren. Beschouw een module als een gefabriceerde chip die op een PCB is geplaatst en het wordt vrij duidelijk dat de enige manier om met de chip te communiceren vi

Een module is een blok Verilog-code dat een bepaalde functionaliteit implementeert. Modules kunnen worden ingebed in andere modules en een module op een hoger niveau kan communiceren met de modules op een lager niveau met behulp van hun invoer- en uitvoerpoorten. Syntaxis Een module moet worden ing

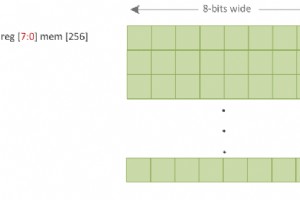

Een array declaratie van een net of variabele kan zowel scalair als vector zijn. Een willekeurig aantal dimensies kan worden gemaakt door een adresbereik op te geven achter de ID-naam en wordt een multidimensionale array genoemd. Arrays zijn toegestaan in Verilog voor reg , wire , integer en real

Verilog