Wiskundige functies van Verilog kunnen worden gebruikt in plaats van constante uitdrukkingen en ondersteunen beide integer en echt wiskunde. Gehele wiskundige functies De functie $clog2 geeft het plafond van log2 . terug van het gegeven argument. Dit wordt meestal gebruikt om de minimale breedte t

Weergavesysteemtaken worden voornamelijk gebruikt om informatieve en foutopsporingsberichten weer te geven om de stroom van simulatie uit logbestanden te volgen en helpt ook om sneller fouten op te sporen. Er zijn verschillende groepen weergavetaken en formaten waarin ze waarden kunnen afdrukken. T

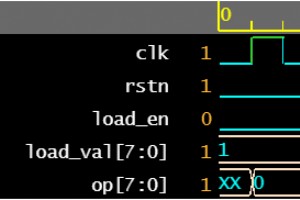

Klokken zijn van fundamenteel belang voor het bouwen van digitale schakelingen, omdat hierdoor verschillende blokken met elkaar kunnen worden gesynchroniseerd. Eigenschappen van een klok De belangrijkste eigenschappen van een digitale klok zijn de frequentie die de klokperiode bepaalt , zijn werkcy

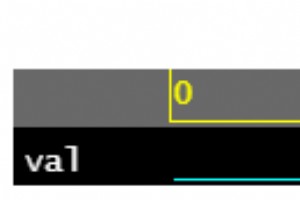

Verilog-ontwerp en testbench hebben meestal veel coderegels, bestaande uit always of initial blokken, doorlopende opdrachten en andere procedurele uitspraken die in de loop van een simulatie op verschillende tijdstippen actief worden. Elke verandering in waarde van een signaal in het Verilog-model

Verilog-simulatie hangt af van hoe tijd wordt gedefinieerd, omdat de simulator moet weten wat een # 1 betekent in termen van tijd. De `timescale compiler-richtlijn specificeert de tijdseenheid en precisie voor de modules die erop volgen. Syntaxis `timescale <time_unit>/<time_precision&

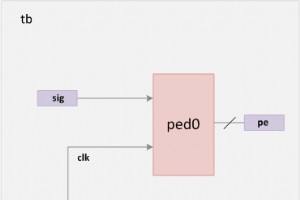

Verilog is een hardwarebeschrijvingstaal en ontwerpers hoeven hun RTL-ontwerpen niet te simuleren om ze om te zetten in logische poorten. Dus wat is de noodzaak om te simuleren? Simulatie is een techniek waarbij op verschillende tijdstippen verschillende inputstimulansen op het ontwerp worden toe

Standaard Verilog-primitieven zoals nand en not is misschien niet altijd gemakkelijk of voldoende om complexe logica weer te geven. Nieuwe primitieve elementen genaamd UDP of door de gebruiker gedefinieerde primitieven kan worden gedefinieerd om combinatorische of sequentiële logica te modelleren.

Verilog biedt ook ondersteuning voor modellering op transistorniveau, hoewel het tegenwoordig zelden door ontwerpers wordt gebruikt, omdat de complexiteit van circuits vereist dat ze naar hogere abstractieniveaus gaan in plaats van modellering op switchniveau te gebruiken. NMOS/PMOS module des

Digitale elementen zijn binaire entiteiten en kunnen alleen een van de twee waarden bevatten - 0 en 1. De overgang van 0 naar 1 en 1 naar 0 heeft echter een overgangsvertraging en dat geldt ook voor elk poortelement om de waarde van invoer naar zijn uitvoer te verspreiden. Een EN-poort met twee in

Enkele van de belangrijkste ingebouwde primitieven werden besproken in het vorige artikel en het zou goed zijn om enkele praktische voorbeelden te zien van het gebruik van eenvoudige and , nor en not poorten. Merk op dat om de Verilog-code te schrijven met behulp van poorten, het noodzakelijk is da

De meeste digitale ontwerpen worden gedaan op een hoger abstractieniveau zoals RTL, hoewel het soms intuïtief wordt om kleinere deterministische circuits op een lager niveau te bouwen door combinatie-elementen zoals en te gebruiken. en of . Modellering die op dit niveau wordt gedaan, wordt gewoonlij

De meeste programmeertalen hebben een karakteristieke eigenschap genaamd scope die de zichtbaarheid van bepaalde codesecties voor variabelen en methoden definieert. Het bereik definieert een naamruimte om botsingen tussen verschillende objectnamen binnen dezelfde naamruimte te voorkomen. Verilog de

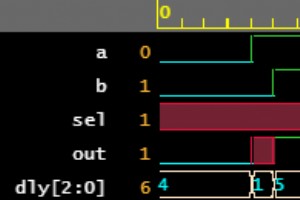

Verilog-vertragingsinstructies kunnen vertragingen hebben die aan de linkerkant of aan de rechterkant van de toewijzingsoperator zijn gespecificeerd. Vertragingen tussen opdrachten // Delay is specified on the left side #<delay> <LHS> = <RHS> Een tussenopdracht vertragingsv

Er zijn twee soorten timingcontroles in Verilog - vertraging en evenement uitdrukkingen. De vertraging controle is slechts een manier om een vertraging toe te voegen tussen het moment waarop de simulator de instructie tegenkomt en wanneer deze deze daadwerkelijk uitvoert. De gebeurtenisuitdrukking

Verilog ondersteunt een aantal compiler-richtlijnen die de compiler in wezen opdragen om de code op een bepaalde manier te behandelen. Een deel van de code kan bijvoorbeeld een implementatie van een bepaalde functie vertegenwoordigen en er moet een manier zijn om de code niet in het ontwerp op te ne

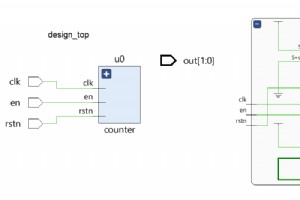

Parameters zijn Verilog-constructies waarmee een module opnieuw kan worden gebruikt met een andere specificatie. Een 4-bits opteller kan bijvoorbeeld worden geparametriseerd om een waarde voor het aantal bits te accepteren en nieuwe parameterwaarden kunnen worden doorgegeven tijdens het aanmaken v

Een function is bedoeld om enige verwerking op de invoer uit te voeren en een enkele waarde terug te geven, terwijl een task is algemener en kan meerdere resultaatwaarden berekenen en retourneren met behulp van output en inout typ argumenten. Taken kunnen tijdrovende simulatie-elementen bevatten, zo

Vaak vinden we bepaalde stukjes code herhalend en meerdere keren aangeroepen binnen de RTL. Ze nemen meestal geen simulatietijd in beslag en kunnen complexe berekeningen met zich meebrengen die met verschillende gegevenswaarden moeten worden gedaan. In dergelijke gevallen kunnen we een function . de

De case statement controleert of de gegeven expressie overeenkomt met een van de andere expressies in de lijst en vertakt dienovereenkomstig. Het wordt meestal gebruikt om een multiplexer te implementeren. De constructie als-anders is mogelijk niet geschikt als er veel voorwaarden moeten worden ge

Een for lus is de meest gebruikte lus in software, maar wordt voornamelijk gebruikt om te repliceren hardwarelogica in Verilog. Het idee achter een for lus is het herhalen van een reeks instructies die in de lus zijn gegeven, zolang de gegeven voorwaarde waar is. Dit lijkt erg op de while lus, maar

Verilog