Alle gedragscode is geschreven in module en endmodule . Dus welk digitaal ontwerp je ook wilt maken, het past in een module blok. Het kan al dan niet poorten hebben gedefinieerd - laat signalen het blok binnenkomen als input of ontsnap aan het blok als output . Module De lege module in het ondersta

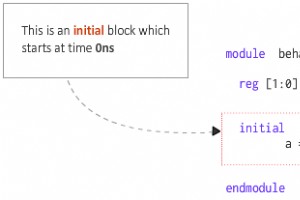

Een set Verilog-instructies wordt meestal achter elkaar uitgevoerd in een simulatie. Deze verklaringen zijn geplaatst in een procedurele blok. Er zijn hoofdzakelijk twee soorten procedurele blokken in Verilog - initieel en altijd Syntaxis initial [single statement] initial begin [multi

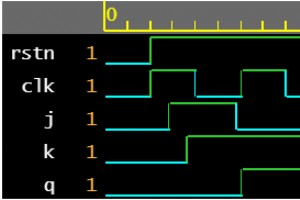

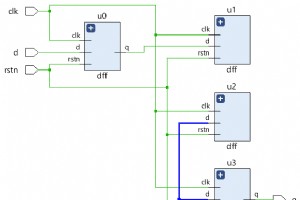

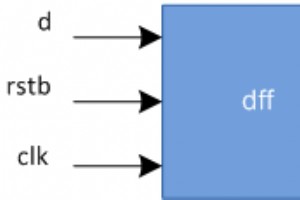

Een vorig artikel toonde verschillende voorbeelden van het gebruik van een always blok om combinatorische logica te implementeren. Een always blok wordt ook voornamelijk gebruikt om sequentiële . te implementeren logica met geheugenelementen zoals flip-flops die waarden kunnen bevatten. JK-teenslipp

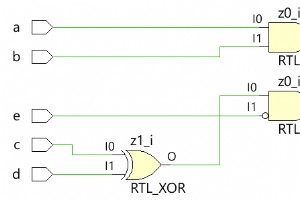

Het verilog always-blok kan worden gebruikt voor zowel sequentiële als combinatorische logica. Een paar ontwerpvoorbeelden werden getoond met een assign uitspraak in een vorig artikel. Dezelfde reeks ontwerpen zal vervolgens worden onderzocht met behulp van een always blok. Voorbeeld #1:Eenvoudige c

Een always blok is een van de procedurele blokken in Verilog. Statements binnen een always-blok worden opeenvolgend uitgevoerd. Syntaxis always @ (event) [statement] always @ (event) begin [multiple statements] end De always blok wordt uitgevoerd bij een bepaalde gebeurtenis. De gebeurt

Multi-bit Verilog-draden en -variabelen kunnen met behulp van aaneenschakeling worden samengevoegd om een grotere multi-netdraad of variabele te vormen operators { en } gescheiden door commas. Aaneenschakeling mag naast draden en variabelen ook uitdrukkingen en grootteconstanten als operanden hebb

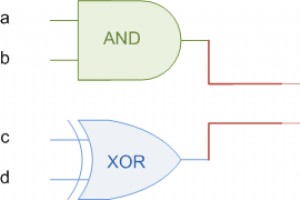

Gegevens die niet kunnen worden verwerkt, zijn vrij nutteloos, er zal altijd een vorm van berekening nodig zijn in digitale circuits en computersystemen. Laten we eens kijken naar enkele van de operators in Verilog waarmee synthesetools geschikte hardware-elementen kunnen realiseren. Verilog rekenku

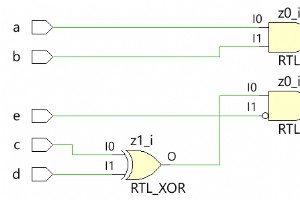

De verilog assign-instructie wordt meestal gebruikt om continu een signaal van wire . te sturen datatype en wordt gesynthetiseerd als combinatorische logica. Hier zijn nog enkele ontwerpvoorbeelden met de assign verklaring. Voorbeeld #1:Eenvoudige combinatorische logica De onderstaande code impleme

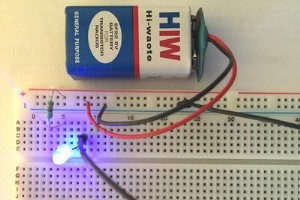

Signalen van het type wire of een soortgelijk draadachtig gegevenstype vereist de continue toewijzing van een waarde. Denk bijvoorbeeld aan een elektrische draad die wordt gebruikt om stukken op een breadboard met elkaar te verbinden. Zolang de +5V-batterij op het ene uiteinde van de draad is aanges

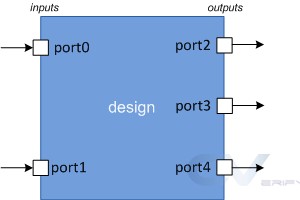

Zoals we in een vorig artikel zagen, worden grotere en complexere ontwerpen gebouwd door meerdere modules op een hiërarchische manier te integreren. Modules kunnen worden geïnstantieerd binnen andere modules en poorten van deze instanties kan worden verbonden met andere signalen in de oudermodule.

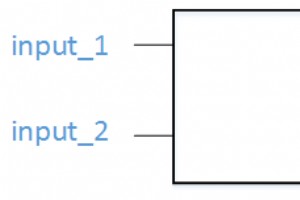

Poorten zijn een reeks signalen die fungeren als in- en uitgangen voor een bepaalde module en zijn de primaire manier om ermee te communiceren. Beschouw een module als een gefabriceerde chip die op een PCB is geplaatst en het wordt vrij duidelijk dat de enige manier om met de chip te communiceren vi

Een module is een blok Verilog-code dat een bepaalde functionaliteit implementeert. Modules kunnen worden ingebed in andere modules en een module op een hoger niveau kan communiceren met de modules op een lager niveau met behulp van hun invoer- en uitvoerpoorten. Syntaxis Een module moet worden ing

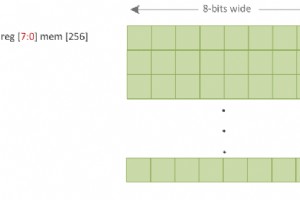

Een array declaratie van een net of variabele kan zowel scalair als vector zijn. Een willekeurig aantal dimensies kan worden gemaakt door een adresbereik op te geven achter de ID-naam en wordt een multidimensionale array genoemd. Arrays zijn toegestaan in Verilog voor reg , wire , integer en real

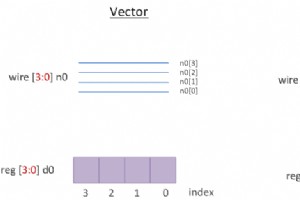

Verilog moet zowel individuele bits als groepen bits vertegenwoordigen. Een sequentieel element met een enkel bit is bijvoorbeeld een flip-flop. Een 16-bits sequentieel element is echter een register dat 16 bits kan bevatten. Voor dit doel heeft Verilog scalar en vector netten en variabelen. Scalair

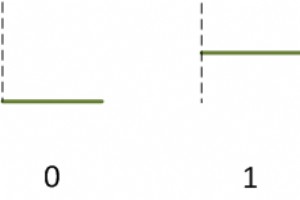

De primaire bedoeling van gegevenstypen in de Verilog-taal is om gegevensopslagelementen zoals bits in een flip-flop en transmissie-elementen zoals draden weer te geven die verbinding maken tussen logische poorten en sequentiële structuren. Welke waarden hebben variabelen? Bijna alle datatypes kun

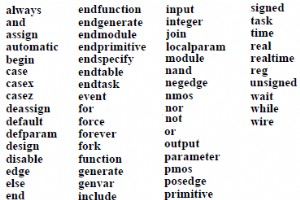

Lexicale conventies in Verilog zijn vergelijkbaar met C in die zin dat het een stroom tokens bevat. Een lexicale token kan bestaan uit een of meer karakters en tokens kunnen opmerkingen, trefwoorden, cijfers, strings of witruimte zijn. Alle regels moeten worden afgesloten met een puntkomma ; . Ve

Voordat we naar meer details van de Verilog-taal kijken, zou het goed zijn om de verschillende abstractielagen in chipontwerp te begrijpen. De bovenste laag is de architectuur op systeemniveau die de verschillende subblokken definieert en groepeert op basis van functionaliteit. Een processorcluster

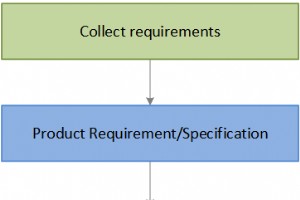

Een typische ontwerpstroom volgt een onderstaande structuur en kan in meerdere stappen worden opgesplitst. Sommige van deze fasen gebeuren parallel en sommige opeenvolgend. We zullen bekijken hoe een typische projectontwerpcyclus er vandaag de dag in de industrie uitziet. Vereisten Een klant van

In de begindagen van geïntegreerde schakelingen moesten ingenieurs gaan zitten en fysiek transistors en hun verbindingen op papier tekenen om ze zo te ontwerpen dat ze op silicium kunnen worden gefabriceerd. Grotere en complexere circuits vereisten meer ingenieurs, tijd en andere middelen en al snel

Verilog is een soort hardwarebeschrijvingstaal (HDL). Verilog is een van de twee talen die door het onderwijs en het bedrijfsleven worden gebruikt om FPGAs en ASICs te ontwerpen. Als je niet bekend bent met hoe FPGAs en ASICs werken, lees dan deze pagina voor een inleiding tot FPGAs en ASICs. Verilo

Verilog