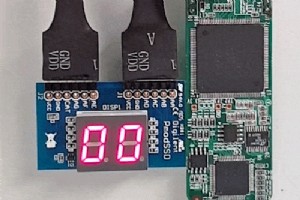

In dit artikel presenteer ik een VHDL-module die een tweecijferig nummer op de Pmod SSD kan weergeven:Seven-segment Display van Digilent. Het dubbele 7-segmentdisplay is compatibel met de Pmod-interface, wat betekent dat u het kunt gebruiken zonder te solderen. Hij past in de Pmod-connector, die sta

* Dit artikel bevat een advertentielink voor UpCloud VPS Continue levering en continue integratie zijn flexibele softwareontwikkelingsmethoden die de cyclustijd tussen codewijziging en implementatie verkorten. Door automatisering te gebruiken om codewijzigingen te verifiëren en releasebestanden sa

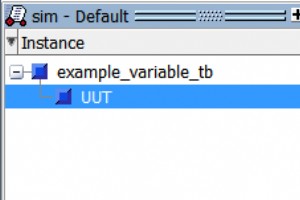

Hoe u VHDL-variabelen op uw simulatiegolfvorm kunt zien Modelsim heeft een manier om uw VHDL-variabelen tijdens een simulatie te bekijken, maar ze maken het niet gemakkelijk om dit te doen. In Modelsim zijn dit de Objecten venster geeft nooit variabelen weer. Modelsim-objectenvenster, geen varia

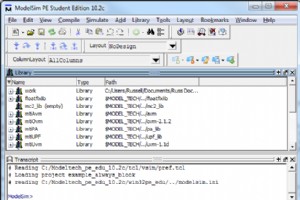

Tutorial – Modelsim gebruiken voor simulatie, voor beginners. Modelsim is een programma gemaakt door Mentor Graphics dat wordt gebruikt voor het simuleren van uw VHDL- en Verilog-ontwerpen. Het is het meest gebruikte simulatieprogramma in het bedrijfsleven en het onderwijs. Deze tutorial legt eerst

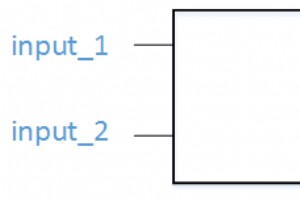

Tutorial – Inleiding tot VHDL VHDL is een vreselijk acroniem. Het staat voor V HSIC H ardware D omschrijving L taal. Een acroniem in een acroniem, geweldig! VHSIC staat voor V ery H hoog S plaste I geïntegreerde C stroom. Daarom is VHDL uitgebreid V ery hogesnelheidsgeïntegreerd circuit H ardware D

Kortom, VHDL is een computertaal die wordt gebruikt voor het ontwerpen van digitale schakelingen. Ik gebruik de term computertaal om VHDL te onderscheiden van andere, meer gebruikelijke programmeertalen zoals Java of C++. Maar is VHDL een programmeertaal? Jazeker. Het is een programmeertaal die

Hoewel VHDL- en FPGA-tools vaak erg duur zijn, is het gemakkelijk om gratis toegang te krijgen tot state-of-the-art software als je student bent. Er zijn verschillende simulatoren, editors en IDEs om met VHDL te werken. In dit artikel wordt uitgelegd hoe u twee van de meest populaire programmas inst

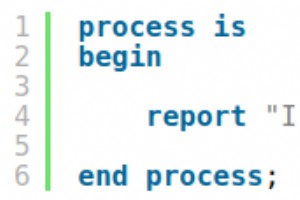

Als ik een nieuwe programmeertaal leer, begin ik altijd graag met het leren printen. Als je het uitvoeren van Hallo wereld! onder de knie hebt, weet je dat de omgeving werkt. Het toont je ook het basisskelet van de taal, de absolute minimumcode die nodig is om output te produceren. Je denkt misschi

In de vorige tutorial hebben we geleerd dat een proces kan worden gezien als een programmathread. We hebben ook geleerd dat een wait; statement zorgt ervoor dat het programma voor onbepaalde tijd pauzeert. Maar is er een manier om een programma te laten wachten op een andere tijdwaarde dan voor al

In de vorige tutorial hebben we geleerd hoe je de tijd kunt uitstellen met behulp van de wait for uitspraak. We leerden ook over de proceslus. We weten nu dat als we het toestaan, de proces-thread voor altijd in het proces zal blijven lopen. Maar wat als we iets slechts één keer willen doen aan het

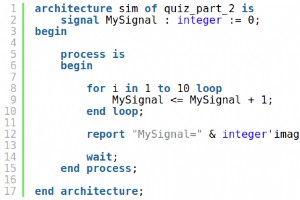

In de vorige tutorial hebben we geleerd om een oneindige lus te maken met behulp van de loop uitspraak. We hebben ook geleerd hoe je een lus kunt doorbreken met behulp van de exit uitspraak. Maar wat als we willen dat de lus een bepaald aantal keren wordt herhaald? De For-Loop is de gemakkelijkste

In de vorige zelfstudie hebben we geleerd hoe u een For-Loop kunt gebruiken om over een geheel getal te itereren. Maar wat als we een meer gedetailleerde controle van de lus willen dan alleen een vast geheel getal? We kunnen hiervoor een While-Loop gebruiken. De While-Loop blijft de bijgevoegde cod

Je hebt dus het eerste deel van de serie Basic VHDL Tutorial afgerond. Gefeliciteerd! Je bent slechts uren en uren verwijderd om een echte VHDL-whizz te worden. Maar je hebt de eerste stap voltooid, en dat is nu het belangrijkste! Voordat we verder gaan, moet je je vaardigheden op de proef stelle

In de vorige tutorial hebben we geleerd hoe je een variabele in een proces declareert. Variabelen zijn goed voor het maken van algoritmen binnen een proces, maar zijn niet toegankelijk voor de buitenwereld. Als een bereik van een variabele zich slechts binnen één proces bevindt, hoe kan het dan inte

In de vorige tutorial leerden we de belangrijkste verschillen tussen signalen en variabelen. We hebben geleerd dat signalen een breder bereik hebben dan variabelen, die alleen binnen één proces toegankelijk zijn. Dus hoe kunnen we signalen gebruiken voor communicatie tussen verschillende processen?

In de vorige tutorial gebruikten we een voorwaardelijke expressie met de Wait Until-instructie. De uitdrukking zorgde ervoor dat het proces alleen werd geactiveerd als de twee tegensignalen gelijk waren. Maar wat als we willen dat het programma in een proces verschillende acties onderneemt op basis

Gebruik altijd een gevoeligheidslijst om processen in productiemodules te activeren. Gevoeligheidslijsten zijn parameters voor een proces waarin alle signalen worden vermeld waarvoor het proces gevoelig is. Als een van de signalen verandert, wordt het proces geactiveerd en wordt de code erin uitgevo

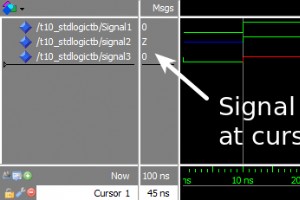

Het meest gebruikte type in VHDL is de std_logic . Zie dit type als een enkele bit, de digitale informatie die wordt gedragen door een enkele fysieke draad. De std_logic geeft ons een meer fijnmazige controle over de bronnen in ons ontwerp dan de integer type, dat we in de vorige tutorials hebben ge

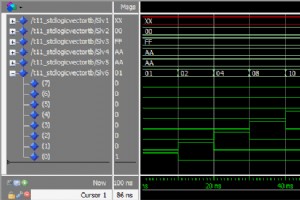

De std_logic_vector type kan worden gebruikt voor het maken van signaalbussen in VHDL. De std_logic is het meest gebruikte type in VHDL, en de std_logic_vector is de array-versie ervan. Terwijl de std_logic is geweldig voor het modelleren van de waarde die kan worden gedragen door een enkele draad,

Test je codeervaardigheden met deze VHDL-quiz na het voltooien van tutorials 6-11 van de Basic VHDL Tutorial-serie! Als je de blogposts hebt gelezen, de videos hebt bekeken en de oefeningen hebt gedaan, zou je gekwalificeerd moeten zijn om de meeste vragen in de quiz te beantwoorden. De quiz is opz

VHDL