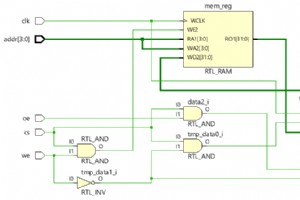

Ontwerp module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); r

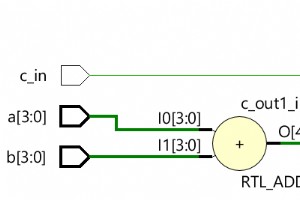

Een opteller is een digitale component die de optelling van twee getallen uitvoert. Het is het belangrijkste onderdeel in een ALU van een processor en wordt gebruikt om adressen, tabelindexen, bufferaanwijzers en op veel andere plaatsen te verhogen waar toevoeging vereist is. Een volledige opteller

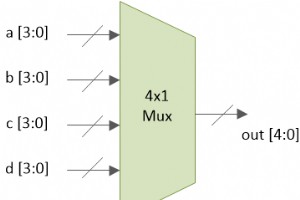

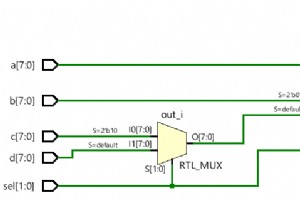

Wat is een mux of multiplexer? Een multiplexer of mux kortom, is een digitaal element dat gegevens overdraagt van een van de N-ingangen naar de uitgang op basis van het geselecteerde signaal. Het onderstaande geval is wanneer N gelijk is aan 4. Een 4-bit multiplexer zou bijvoorbeeld N ingangen va

Ontwerp module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else

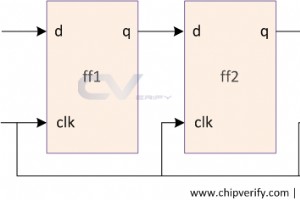

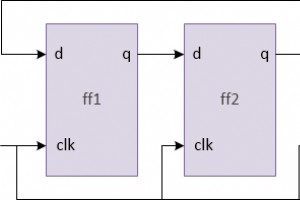

In digitale elektronica, een schuifregister is een cascade van flip-flops waarbij de uitgangspen q van de ene flop is verbonden met de gegevensinvoerpen (d) van de volgende. Omdat alle flops op dezelfde klok werken, zal de bitarray die is opgeslagen in het schuifregister één positie verschuiven. Als

Ontwerp module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (int

Ontwerp module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else o

Ontwerp module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+

Ontwerp module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1)

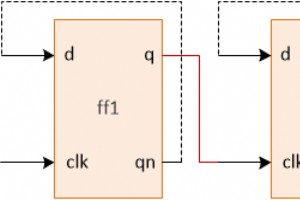

Een rimpeling counter is een asynchrone teller waarin alle flops behalve de eerste worden geklokt door de uitvoer van de voorgaande flop. Ontwerp module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (p

De 4-bits teller begint met ophogen van 4b0000 tot 4h1111 en gaat dan terug naar 4b0000. Het blijft tellen zolang het is voorzien van een lopende klok en de reset hoog wordt gehouden. De rollover vindt plaats wanneer het meest significante deel van de laatste toevoeging wordt weggegooid. Wanneer de

Een flip-flop vangt gegevens op aan de ingang aan de positieve of negatieve flank van een klok. Het belangrijkste om op te merken is dat wat er ook gebeurt met gegevens na de klokflank tot de volgende klokflank, niet wordt weerspiegeld in de uitvoer. Een vergrendeling aan de andere kant, registreert

Ontwerp module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule Testbank module tb; reg clk; reg

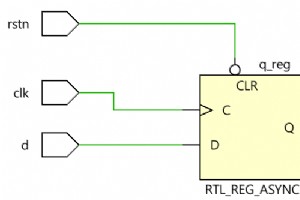

Een D-flip-flop is een sequentieel element dat volgt op de invoerpin d op de gegeven rand van een klok. Ontwerp #1:Met async active-low reset module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or negedge rstn)

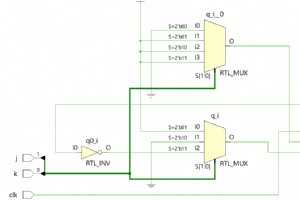

Ontwerp module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule Ha

Het is altijd het beste om aan de slag te gaan met een heel eenvoudig voorbeeld, en geen enkel voorbeeld dient het beste doel behalve Hallo wereld!. // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital

Verilog heeft systeemtaken en -functies die bestanden kunnen openen, waarden in bestanden kunnen uitvoeren, waarden uit bestanden kunnen lezen en in andere variabelen kunnen laden en bestanden kunnen sluiten. Bestanden openen en sluiten module tb; // Declare a variable to store the file handle

Standaard tijdschaal Hoewel wordt verwacht dat Verilog-modules een tijdschaal hebben die vóór de module is gedefinieerd, kunnen simulators een standaardtijdschaal invoegen. De werkelijke tijdschaal die wordt toegepast op elk bereik in een door Verilog uitgewerkte hiërarchie kan worden afgedrukt met

De tijdschaalrichtlijn van Verilog specificeert tijdseenheid en precisie voor simulaties. Verilog $timeformat systeemfunctie specificeert %t formaatspecificatie rapportagestijl in weergave-instructies zoals $display en $strobe . Syntaxis $timeformat(<unit_number>, <precision>, <

Wiskundige functies van Verilog kunnen worden gebruikt in plaats van constante uitdrukkingen en ondersteunen beide integer en echt wiskunde. Gehele wiskundige functies De functie $clog2 geeft het plafond van log2 . terug van het gegeven argument. Dit wordt meestal gebruikt om de minimale breedte t

Verilog