Een RRAM-geïntegreerde 4T SRAM met zelfremmende resistieve schakelbelasting door puur CMOS logisch proces

Abstract

Dit artikel rapporteert een nieuw volledig logisch compatibel 4T2R niet-vluchtig statisch willekeurig toegankelijk geheugen (nv-SRAM) met zijn zelfremmende gegevensopslagmechanisme voor in low-power/high-speed SRAM-toepassingen. Met een compact celoppervlak en volledige logische compatibiliteit, bevat deze nieuwe nv-SRAM twee STI-ReRAM's die zijn ingebed in de 4T SRAM. Gegevens kunnen worden gelezen/geschreven via een cross-couple vluchtige structuur voor het handhaven van een hoge toegangssnelheid. Gegevens kunnen niet-vluchtig worden opgeslagen in een nieuwe SRAM-cel door middel van een unieke zelfremmende bewerking op de resistieve RRAM-belasting (Random Access Memory), waardoor geen statisch vermogen wordt bereikt tijdens het vasthouden van gegevens.

Achtergrond

In de afgelopen jaren zijn er verschillende low-power statische random access-geheugens ontwikkeld om te voldoen aan de behoefte in computersystemen op draagbare apparaten en IOT-toepassingen [1,2,3,4,5,6]. Naarmate de CMOS-technologie verkleint tot nanometer-regime, neemt de lekstroom in de off-state drastisch toe, wat leidt tot een verslechtering van het statische stroomverbruik voor vluchtige geheugenmodules [7, 8]. Het statische stroomverbruik dat wordt veroorzaakt door de lekstroom in transistors op nanoschaal, is een van de belangrijkste uitdagingen geworden voor de vooruitgang van SRAM's met een laag vermogen. [9,10,11]. In de loop der jaren zijn verschillende celstructuren of operatietechnieken [12,13,14,15,16] voorgesteld om het stroomverbruik in SRAM's te minimaliseren. Sommige van de nieuw voorgestelde cellen bevatten niet-vluchtige opslagelementen, zoals resistief willekeurig toegankelijk geheugen (RRAM) en magnetoresistief willekeurig toegankelijk geheugen (MRAM) [17,18,19,20], om een nulhoudvermogen te bereiken met behoud van een lage werking kracht en snelle toegangssnelheid bij het verwerken van vluchtige gegevens. Het toevoegen van niet-vluchtige opslagelementen aan op logica gebaseerde SRAM-arrays vereist echter over het algemeen extra lagen en/of processen naast de standaard logische platforms [21,22,23]. Dit zal onvermijdelijk de procescomplexiteit verhogen voor hun ontwikkeling. Bovendien vereisen deze back-end-gebaseerde RRAM's en MRAM's een grote verbindingsstructuur, bestaande uit meerdere stapels via's en metalen naar de SRAM-cellen. Deze overbruggingsstructuren verhogen de parasitaire capaciteit naar het SRAM-gegevensopslagknooppunt, wat de toegangssnelheid van deze niet-vluchtige SRAM-cellen beïnvloedt [24, 25]. In ons eerdere werk [26] werd eerst een nieuwe, nulstatische kracht 4T nv-SRAM met STI-zijwand RRAM's naast de zwevende opslagknooppunten van 4T SRAM voorgesteld. In deze brief wordt deze 4T2R nv-SRAM met niet-vluchtige gegevensopslag, nulhoudkracht en snelle toegangssnelheid verder geanalyseerd en geoptimaliseerd voor embedded NVM-toepassingen.

Methoden

STI-ReRAM celstructuur

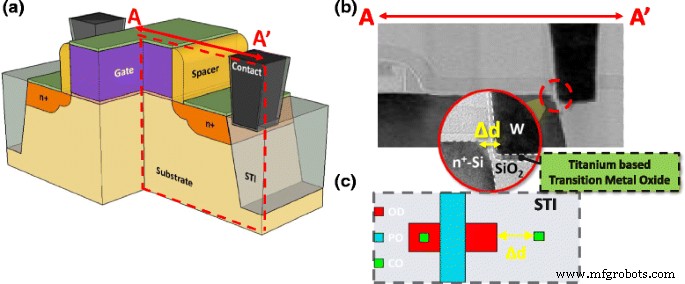

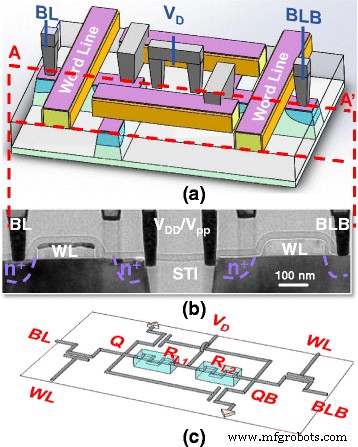

In de 3D STI-RRAM-structuur in figuur 1a bestaat het resistieve opslagknooppunt uit een overgangsmetaaloxide (TMO) tussen twee elektroden, het N+-gebied en een wolfraamplug aan de linker- en rechterkant, respectievelijk. Zoals getoond in de TEM-afbeelding in Fig. 1b en lay-out in Fig. 1c, door het contact op het STI-gebied te plaatsen met de juiste afstand tot het N+-gebied, de resterende SiO2 en barrièrelaag onder wolfraamplug worden TMO-film en presenteren met de resistieve schakelkwaliteit.

een 3D-afbeelding van een 1T1R-cel met STI-ReRAM direct naast de n+-junctie. b Het overeenkomstige TEM-beeld van een resistief opslagknooppunt bestaande uit overgangsmetaaloxiden, gevormd tussen een speciaal geplaatst contact en het n+-gebied van de geselecteerde transistor. c Lay-out

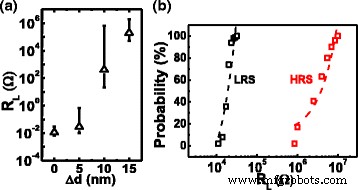

De TMO-dikte kan worden gecontroleerd door een juiste afstand Δd te kiezen tussen een contact en het N+-diffusiegebied. Op basis van de meting in figuur 2a is er een positieve correlatie tussen het initiële weerstandsniveau en de getrokken afstand, Δd, bepaald door de maskers die respectievelijk STI- en contactgebieden definiëren. Voor de volgende studie wordt RRAM met Δd gelijk aan 10 nm gekozen vanwege de lagere vormingsspanning en bij voorkeur RL distributie in zowel lage-weerstandstoestand (LRS) als hoge-weerstandstoestand (HRS) zoals samengevat in Fig. 2b. Met de juiste spanningsregeling van de woordlijn (WL) tijdens set/forming-bewerkingen, kan de ingestelde stroom lokaal worden vastgeklemd door de geselecteerde transistor, waardoor betere uithoudingsvermogenprestaties mogelijk zijn.

een De gemeten initiële weerstand van STI-RRAM-monsters met verschillende △d. b Cumulatieve waarschijnlijkheid van de belastingsweerstand na reset/set van de STI-RRAM bij zowel hoge als lage weerstandstoestanden

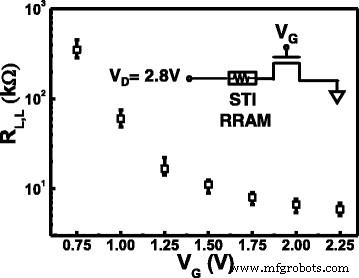

Gegevens in Fig. 3 laten verder zien dat het leesstroomniveau in LRS goed kan worden geregeld door de poortspanning, VG . Tijdens het vormen bij VD =-2,8 V, de geselecteerde transistor begrenst de maximale stroom die door de STI-RRAM gaat nadat het apparaat is ingesteld op LRS. Het daaropvolgende LRS-statusweerstandsniveau is omgekeerd evenredig met de lokaal geklemde stroom, die is gevonden in verschillende op TaO gebaseerde RRAM-apparaten [27, 28].

Correlatie tussen belastingsweerstandsniveaus, RL,L , en de toegepaste poortspanning tijdens het instellen. Gegevens suggereren dat verschillende RL,L kan worden verkregen door een ander niveau van de geselecteerde poortspanning in te stellen

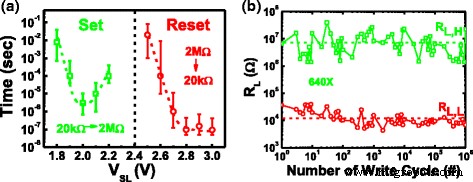

Om de resistieve schakelkarakteristieken van STI-RRAM te garanderen, worden time-to-set en time-to-reset getest, zoals weergegeven in figuur 4a. Instel- en resetbewerkingen kunnen worden geoptimaliseerd wanneer VSL =2 en 2,8 V, respectievelijk. De RRAM-duurzaamheidstest is samengevat in figuur 4b. Door gebruik te maken van een incrementeel stappuls-programmeeralgoritme, kan het leesvenster stabiel blijven na 1 miljoen cycli.

een Samengevatte time-to-set en time-to-reset vs. VPP . b Resultaat van een miljoen cycli duurtest van de STI-RRAM met behulp van het algoritme voor incrementele stappulsprogrammering

Niet-vluchtig SRAM-concept

De 3D-illustratie in Fig. 5 toont de nieuw voorgestelde 4T2R nv-SRAM-celstructuur en de bijbehorende TEM-afbeelding in dwarsdoorsnede langs de AA'-cutline. Twee STI-RRAM's dienen als zowel de niet-vluchtige opslagknooppunten als laadweerstanden, die zijn ingeklemd tussen de Q- en QB N+-diffusiegebieden en een contact dat nauw op de STI-randen is geland met het juiste afstandsontwerp. De TEM-afbeelding toont een goed gevormde STI-RRAM aan zowel de linker- als de rechterkant van het isolatiegebied en resulteert in een vrij compacte cel met deze dicht bij elkaar geplaatste niet-vluchtige opslagknooppunten op hetzelfde niveau van de transistors.

een 3D illustratie van de voorgestelde 4T2R nv-SRAM celstructuur en de b overeenkomstige transversale TEM-afbeelding. c Het schakelschema van een SRAM-cel wordt weergegeven met twee RRAM-weerstanden als laadapparaten

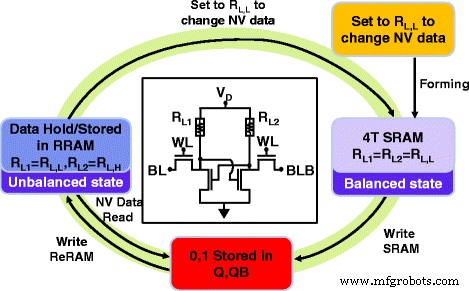

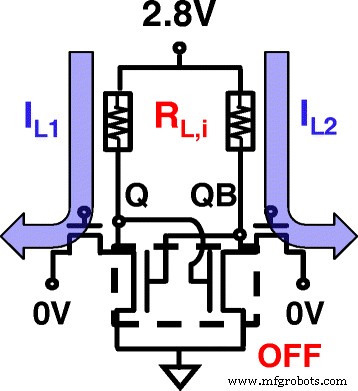

De voorgestelde 4T nv-SRAM kan worden gebruikt in vluchtige en niet-vluchtige modi. De vier verschillende toestanden en het werkingsschema worden geïllustreerd in Fig. 6.

Schakelschema van nv-SRAM-cel en het bijbehorende stroomschema voor het schakelen tussen vluchtige en niet-vluchtige SRAM-bewerkingen

In de begintoestand heeft STI-RRAM doorgaans een weerstandsniveau van 10 8 Ω, terwijl de TMO-film intact is. Door middel van een dekenvormende bewerking kunnen de nv-SRAM-cellen tegelijkertijd blok voor blok worden geïnitialiseerd op VD = 2.8 V. Beide RL1 en RL2 (laadweerstand respectievelijk links en rechts) worden geïnitialiseerd op RL,L . De laatste RL,L niveau van 20~370 kΩ kan worden geregeld door tijdens het vormen een verschillende WL-spanning te geven. De cel bereikt dan een evenwichtstoestand, wat betekent dat de twee laadweerstanden zich in dezelfde toestand bevinden. In deze toestand kan deze cel nu functioneren als de typische 4T2R SRAM, waarbij vluchtige gegevens op een conventionele manier worden verwerkt, door gegevens op te slaan in de kruislings gekoppelde vergrendeling.

Om de gegevens niet-vluchtig op te slaan, kunnen de complementaire vergrendelde gegevens op de RRAM's worden opgeslagen door een zelfremmend mechanisme dat in deze cel wordt geërfd. Wanneer de gegevens met succes zijn opgeslagen in het RRAM-paar, kan men de voeding uitschakelen voor permanente gegevensopslag. Om toegang te krijgen tot de opgeslagen status, past u eenvoudig VDD . opnieuw toe naar de array. De niet-vluchtige gegevens worden automatisch hersteld naar de Q- en QB-knooppunten en zijn toegankelijk via de conventionele SRAM-leesmodus. Ten slotte wordt, om de niet-vluchtige gegevens te vernieuwen, een algemene set-bewerking toegepast op de SRAM-arrays, zodat de array terugkeert naar zijn evenwichtstoestanden.

Resultaten en discussie

Elektrische analyse

De werkingsvoorwaarden voor overgangen tussen verschillende fasen zijn samengevat in Tabel 1.

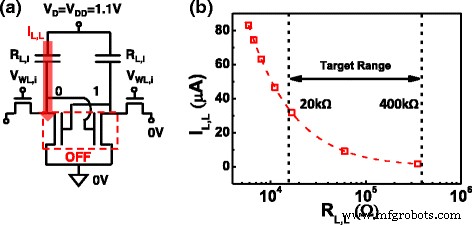

Verschillende RL,L niveau kan worden verkregen door een verschillende WL-spanning in te stellen tijdens de initialisatie van een blok of array. Gezien de stabiliteit en de bedrijfsspanning is de RL,L niveau variërend tussen 20 en 400 kΩ is het eerste doel voor onderzoek in deze studie. Corresponderende WL-spanning van 0,75 tot 1,25 V, de resulterende belastingsweerstand neemt vrij lineair af, zoals weergegeven in Fig. 3. Zoals verwacht, lagere RL,L niveau zal leiden tot een hogere stand-bystroom, zie Fig. 7. Echter, RL,L moet laag genoeg blijven om een groot vergroot gegevensvenster tussen de twee weerstandstoestanden te garanderen. Er moet rekening worden gehouden met zowel statische, dynamische als niet-vluchtige gegevensvensters voor verdere optimalisatie van de beoogde RL,L , die wordt ingesteld door de initialisatievoorwaarde.

een 4T2R SRAM-cel in de wachtstand. b Zoals verwacht, laadweerstandsniveau, IL,L tijdens het vasthouden kan effectief worden verlaagd door een hogere RL,L . te kiezen

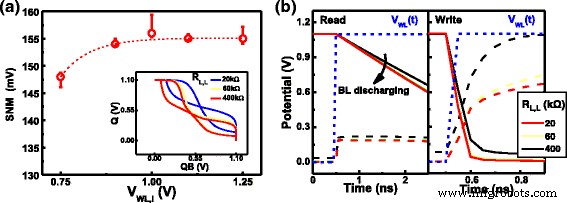

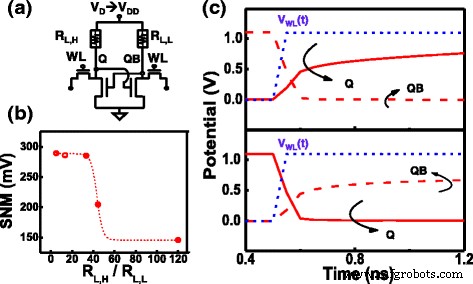

De statische en dynamische karakterisering van de nv-SRAM in de balanstoestand wordt eerst onderzocht, rekening houdend met cellen die onder verschillende omstandigheden zijn geïnitialiseerd. In Fig. 8, de statische ruismarge (SNM) verkregen door de meervoudige vlinderkrommen van cellen geïnitialiseerd door verschillende WL-spanning. Uit gegevens blijkt dat RL,L niveau heeft een minimaal effect op de leesmarge van gebalanceerde cellen, wanneer de laadweerstanden binnen het doelbereik liggen. De SNM-verdeling van meerdere cellen in de balanstoestanden onder verschillende initialisatieomstandigheden is samengevat in figuur 8a. Algehele SNM's blijven redelijk stabiel van cel tot cel, terwijl een redelijke leesmarge kan worden vastgesteld met een WL-spanning lager dan VDD , wat gunstig kan zijn voor toepassingen met een laag stroomverbruik. Om de dynamische lees- en schrijfkenmerken van deze cel in de gebalanceerde toestand te onderzoeken, is de tijdelijke respons van het schrijven van "1" en "0" samengevat in Fig. 8b. Het blijkt dat een hogere RL,L vermindert de optreksnelheid naar de Q, QB-knooppunten, wat de transiënte tijd enigszins kan verhogen tijdens zowel lees- als schrijfbewerkingen. De reactiesnelheid ligt echter nog steeds binnen het verwachte bereik. De bovenstaande gegevens suggereren dat deze 4T2R nv-SRAM vluchtige gegevens in de balanstoestand kan verwerken als conventionele SRAM's.

een De uitgelezen statische ruismarge (SNM) van de voorgestelde SRAM-cellen met verschillende WL-spanning tijdens initialisatie. Redelijke SNM kan worden gehandhaafd binnen een vrij groot bereik van RL,L van 20~400 kΩ. b Dynamische lees- en schrijfkenmerken van een cel onder gebalanceerde belasting laten een goede responstijd zien binnen nanoseconden. Hogere RL,L vermindert de optreksnelheid enigszins tijdens het schrijven

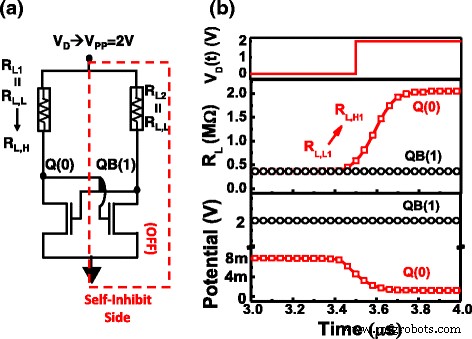

Om gegevens in een STI-RRAM-paar op te slaan, maakt deze cel een zelfselectieve reset mogelijk van slechts één van de RRAM's in het laadweerstandspaar, waardoor de gegevens niet-vluchtig kunnen worden geschreven door een hogere Vpp spanning naar het voedingsknooppunt naar het celblok uniform. Zodra de vergrendelingsgegevens zijn opgeslagen in het Q- en QB-knooppunt, wordt niet-vluchtig schrijven bereikt door het zelfremmende mechanisme in de kruiskoppelingsstructuur met RRAM, zoals weergegeven in figuur 9a. Slechts één kant van RRAM met lage spanning op Q-knooppunt wordt gereset naar RL,H . De stroom op de andere tak is bijna nul omdat de pull-down-transistor wordt uitgeschakeld door de lage VQ .

een Illustratie van een zelfremmend mechanisme tijdens het schrijven van niet-vluchtige gegevens door een kant van twee RRAM's opnieuw in te stellen. b Dynamische verandering van RL en Q, QB-potentieel verifiëren zelfblokkerend schrijven van vergrendelingsgegevens naar RRAM's

Gegevens worden in het RRAM-paar opgeslagen als VPP puls wordt toegepast op het voedingsknooppunt. Bij het schrijven van niet-vluchtige gegevens, de dynamische schakeling van RL en de tijdelijke respons van Q, QB-potentiaal zijn samengevat in Fig. 9b. Meetgegevens suggereerden dat om de STI-RRAM selectief aan één kant te resetten, een puls van 300 ns bij Vpp = 2 V is voldoende. Om ervoor te zorgen dat de vluchtige werking nog steeds onaangetast blijft wanneer de cellen zich in de ongebalanceerde toestand bevinden, zoals Fig. 10a, de SNM-verdeling van cellen met verschillende RL,H /RL,L verhouding zijn samengevat in Fig. 10b. Het is gebleken dat de lage-weerstandsverhouding tussen de toestanden de hold-SNM niet verslechtert. Om ervoor te zorgen dat een cel met een ongebalanceerde belasting, wordt dynamisch schrijven van gegevens naar een dergelijke cel gekarakteriseerd. Gegevens laten zien dat beide toestanden met succes kunnen worden geschreven, waarbij de initiële onbalansweerstandsverhouding van 2 M/400 k wordt overwonnen, zoals weergegeven in Fig. 10c.

een Cross-koppel structuur tijdens onbalans belasting. b Statische ruismarge met verschillende WL-spanningen tijdens initialisatie. c Dynamisch schrijven voor twee verschillende gegevensstatussen. Onbalans RL,L = 400 kΩ kan ook worden geschreven

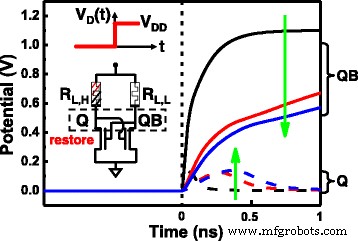

Om de vluchtige gegevens terug te laden die eerder in RRAM waren opgeslagen, kan men eenvoudig VDD . toepassen naar het voedingsknooppunt, wordt de onbalansbelasting in de RRAM's zelf hersteld naar de vergrendelingsknooppunten van Q en QB, zoals geïllustreerd in Fig. 11.

Herstel van de niet-vluchtige gegevens die zijn opgeslagen in Q en QB vanuit een onevenwichtige RRAM-laadstatus. Potentieel van Q- en QB-knooppunten kunnen beide binnen nanoseconden worden hersteld nadat de stroom weer is ingeschakeld

Parasitisch effect en vergelijking

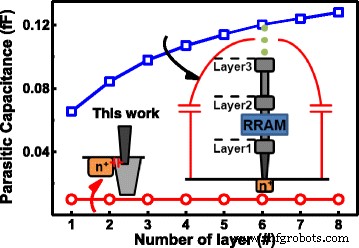

Door de volledig logische compatibele STI-RRAM in deze nieuwe SRAM-cel op te nemen, kan deze cel eenvoudig worden geïmplementeerd door de meeste standaard logische processen zonder maskeringslagen en processtappen toe te voegen. Deze functie kan de toepassingen en flexibiliteit in verschillende niet-vluchtige geheugen-IP-modules die in veel IC-systemen nodig zijn, aanzienlijk verbeteren. Bovendien heeft de voorgestelde 4T2R nv-SRAM een veel kleinere parasitaire capaciteit in vergelijking met andere eerder gerapporteerde nv-SRAM's [29,30,31] die back-end-of-line (BEOL) niet-vluchtige componenten vereisen. Om het Q- en QB-knooppunt van het oppervlak van Si met deze BEOL RRAM of MRAM's te verbinden, zijn meerdere stapels metaal en via-lagen nodig. Deze grote overbruggingsstructuren leiden tot een significant parasitair RC-effect. Grote parasitaire capaciteit geïntroduceerd in de interne knooppunten in de SRAM-cellen kan de reactietijd van de apparaten kritisch beïnvloeden.

Om het parasitaire effect hierop te vergelijken, worden nv-SRAM's onderzocht op basis van de schatting van post-layout simulatie. Ervan uitgaande dat alle cellen worden geïmplementeerd door dezelfde standaard CMOS-technologie, neemt de parasitaire capaciteit op de vergrendelingsknooppunten toe naarmate het aantal metaallagen toeneemt voor cellen die grote overbruggingsstructuren nodig hebben. Voor de nieuwe nv-SRAM die STI-RRAM gebruikt, is er zeer weinig toename van de totale capaciteit op de vergrendelde knooppunten. Verder is het onafhankelijk van het aantal metaallagen dat in een bepaalde schakeling is aangepast. Om het effect van parasitaire capaciteit van de SRAM-snelheid verder te onderzoeken, wordt de gesimuleerde dynamische respons van de SRAM-cellen voorgesteld in [29,30,31] en dit werk vergeleken in Fig. 12.

Parasitaire capaciteit op de vergrendelingsknooppunten van nv-SRAM-cellen uit ref [30] en dat uit dit werk op basis van 40 nm CMOS-technologie een significante toename van parasitaire capaciteit wordt gevonden naarmate het aantal metaallagen toeneemt

Een veel kleinere parasitaire capaciteit van deze embedded nv-SRAM kan leiden tot een snellere responstijd tijdens dynamische leesbewerkingen in de SRAM-cel. Dit voorkomt dat de grote interne capaciteit van de verbindingsbrug invloed heeft op de responstijd van de op logica gebaseerde SRAM-array.

Tabel 2 vergelijkt de belangrijkste kenmerken van eerder gerapporteerde niet-vluchtige SRAM's die zijn geïntegreerd met back-end RRAM's of MRAM's en dit werk. Ondanks de hogere schakelspanning, wordt de op STI-RRAM gebaseerde nv-SRAM gepresenteerd met een veel kleinere parasitaire capaciteit op de interne vergrendelde knooppunten in SRAM-cellen en volledige logische compatibiliteit.

Variatie-geïnduceerde verslechtering van statische ruismarge

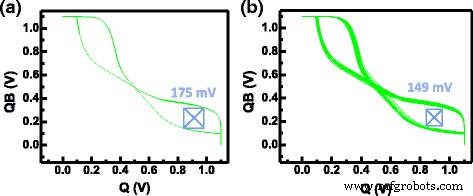

Om de stabiele SNM te garanderen met cellen die onderhevig zijn aan procesvariaties, fluctuaties in RRAM-weerstandsniveaus en in de drempelspanning van de transistor, VT , worden meegenomen in de volgende onderzoeken:mismatches in VT het is bekend dat het SNM-verschuiving in SRAM veroorzaakt door geschaalde technologieën [32, 33]. Bovendien kan het ook een verschillende ingestelde compliantiestroom veroorzaken, wat op zijn beurt kan resulteren in een grotere variatie in het weerstandsniveau van de twee RL,L . Zoals geïllustreerd in Fig. 13, verschillende VT leiden tot verschillende compliantiestroom voor initialisatie in de STI-RRAM-cel, wat leidt tot een verdere mismatch in RL,L . Om de impact van VT . te analyseren variatie op SNM, we gaan uit van VT een Gauss-willekeurige variabele zijn met gemiddelde en variatie op basis van eerdere rapporten [34]. Door Monte-Carlo-simulatie, de distributie van vlindercurven onderworpen aan variaties in RL,L zijn samengevat in Fig. 14a. Wanneer beide varianten in RL,L en VT worden beschouwd, wordt een significante vernauwing van het SNM-venster waargenomen, zoals weergegeven in Fig. 14b. Verhoogde variabiliteit in de nv-SRAM moet in toekomstige studies worden aangepakt.

VT variatie leidt tot verschillende initialisatie-conformiteit IL,1 en ikL,2

Vlindercurven door Monte-Carlo-simulaties die SNM-degradaties vergelijken veroorzaakt door a variatie in RL,L na initialisatie en b variaties in zowel RL,L en VT

Conclusies

Een nieuw 4T2R STI-RRAM-gebaseerd niet-vluchtig SRAM dat volledig logisch compatibel is met het CMOS-logische proces is met succes gedemonstreerd in puur CMOS-logisch proces op 40 nm-technologieknooppunt zonder extra maskers of stappen. Deze nv-SRAM-cel heeft een zelfremmend, zelfherstelmechanisme voor niet-vluchtige gegevens, een kleine parasitaire capaciteit op vergrendelingsknooppunten en nul statisch vermogen tijdens het vasthouden van gegevens. Deze superieure eigenschappen maken op STI-RRAM gebaseerde nv-SRAM een veelbelovende oplossing voor logische niet-vluchtige geheugentoepassingen met laag vermogen/hoge snelheid in de toekomst.

Nanomaterialen

- Inleiding tot digitale geïntegreerde schakelingen

- Geïntegreerde circuits

- Digitale logica met feedback

- Diodeschakelcircuits

- Vermogen in resistieve en reactieve AC-circuits

- Praktische powerfactorcorrectie

- Retentiemodel van TaO/HfO x en TaO/AlO x RRAM met zelfherstellende schakelkenmerken

- Bipolaire resistieve schakelkenmerken van HfO2/TiO2/HfO2 drielaagse structuur RRAM-apparaten op Pt- en TiN-gecoate substraten vervaardigd door atomaire laagafzetting

- Compliance-vrij ZrO2/ZrO2 − x /ZrO2 resistief geheugen met controleerbaar interfaciaal multistate schakelgedrag

- Geleidingsmechanisme en verbeterd uithoudingsvermogen in HfO2-gebaseerd RRAM met nitridatiebehandeling

- Onderzoek naar het effect van het beïnvloeden van richting op het schurende nanometrische snijproces met moleculaire dynamiek