Shift Registers:Serial-in, Serial-out

Serieel-in, serieel-uit schuifregisters vertragen de gegevens met één kloktijd voor elke fase.

Ze slaan een beetje gegevens op voor elk register. Een serieel-in, serieel-uit schuifregister kan één tot 64 bits lang zijn, langer als registers of pakketten in cascade worden geschakeld.

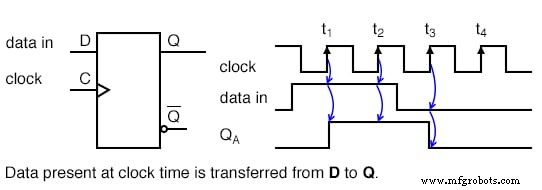

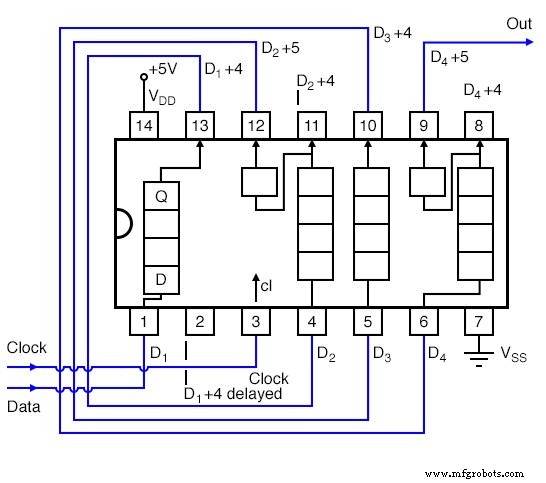

Hieronder ziet u een eentraps schuifregister dat gegevens ontvangt die niet zijn gesynchroniseerd met de registerklok.

De "data in" bij de D pin van het type D FF (Flip-Flop) verandert de niveaus niet wanneer de klok van laag naar hoog verandert.

Mogelijk willen we de gegevens synchroniseren met een systeembrede klok in een printplaat om de betrouwbaarheid van een digitaal logisch circuit te verbeteren.

Het voor de hand liggende punt (in vergelijking met de onderstaande afbeelding) die hierboven is geïllustreerd, is dat alle "data in" aanwezig is op de D pin van het type D FF wordt op kloktijd overgedragen van D naar uitgang Q.

Aangezien ons voorbeeldschuifregister positieve randgevoelige opslagelementen gebruikt, is de uitvoer Q volgt de D invoer wanneer de klok overgaat van laag naar hoog, zoals aangegeven door de pijlen omhoog in het bovenstaande diagram.

Het lijdt geen twijfel welk logisch niveau aanwezig is op kloktijd, omdat de gegevens ruim voor en na de klokflank stabiel zijn.

Dit is zelden het geval in meertraps schuifregisters. Maar dit was een gemakkelijk voorbeeld om mee te beginnen. We houden ons alleen bezig met de positieve, lage naar hoge klokrand.

De dalende flank kan worden genegeerd. Het is heel gemakkelijk om Q . te zien volg D op kloktijd hierboven.

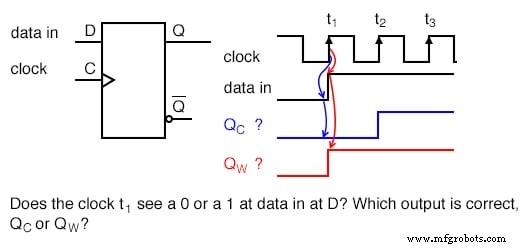

Vergelijk dit met het onderstaande diagram waar de "data in" lijkt te veranderen met de positieve klokflank.

Aangezien "data in" lijkt te veranderen op kloktijd t1 hierboven, wat betekent het type D FF zien op kloktijd?

Het korte, vereenvoudigde antwoord is dat het de gegevens ziet die aanwezig waren op D voor de klok.

Dat is wat wordt overgebracht naar Q op kloktijd t1 . De juiste golfvorm is QC . Op t1 Q gaat naar een nul als deze niet al nul is.

De D register ziet geen een tot tijd t2 , waarna Q hoog wordt.

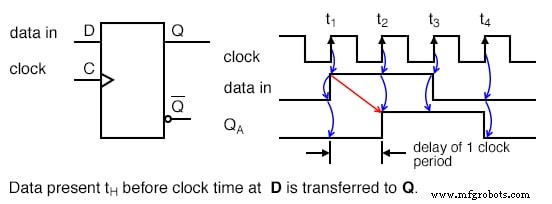

Aangezien gegevens hierboven aanwezig zijn op D wordt geklokt naar Q op kloktijd, en Q kan niet veranderen tot de volgende kloktijd, de D FF vertraagt gegevens met één klokperiode, op voorwaarde dat de gegevens al met de klok zijn gesynchroniseerd. De QA golfvorm is hetzelfde als "data in" met een vertraging van één klokperiode.

Een meer gedetailleerde kijk op wat de invoer van het type D Flip-Flop ziet op kloktijd volgt.

Raadpleeg de onderstaande afbeelding. Aangezien "gegevens in" op kloktijd lijkt te veranderen (hierboven), hebben we meer informatie nodig om te bepalen wat de D FF ziet.

Als de "data in" van een ander schuifregisterstadium is, een ander zelfde type D FF, we kunnen enkele conclusies trekken op basis van gegevensblad informatie.

Fabrikanten van digitale logica stellen informatie over hun onderdelen beschikbaar in gegevensbladen, die voorheen alleen beschikbaar waren in een verzameling die een gegevensboek wordt genoemd .

Databoeken zijn nog beschikbaar; de website van de fabrikant is echter de moderne bron.

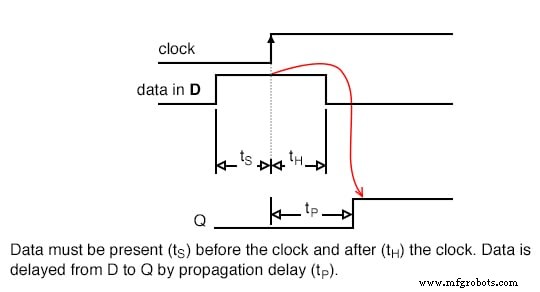

De volgende gegevens zijn geëxtraheerd uit het gegevensblad van de CD4006b voor gebruik bij 5VDC , dat als voorbeeld dient om timing te illustreren. [*]

- tS =100ns

- tH =60ns

- tP =200-400ns typ/max

tS is de insteltijd , moeten de tijdgegevens vóór de kloktijd aanwezig zijn. In dit geval moeten de gegevens aanwezig zijn op D 100ns voor de klok.

Bovendien moeten de gegevens houdtijd worden bewaard tH =60ns na kloktijd. Aan deze twee voorwaarden moet worden voldaan om gegevens van D . betrouwbaar te klokken naar Q van de teenslipper.

Het is geen probleem om de insteltijd van 60ns te halen, aangezien de gegevens op D is er de hele vorige klokperiode geweest als het uit een ander schuifregisterstadium komt.

Bij een klokfrequentie van 1 Mhz is de klokperiode bijvoorbeeld 1000 µs, ruimschoots voldoende.

Gegevens zullen daadwerkelijk aanwezig zijn gedurende 1000 µs voorafgaand aan de klok, wat veel groter is dan de minimaal vereiste tS van 60ns.

De vasthoudtijd tH =60ns wordt gehaald omdat D verbonden met Q van een andere trap niet sneller kan veranderen dan de voortplantingsvertraging van de vorige trap tP =200ns.

Houdtijd wordt gehaald zolang de voortplantingsvertraging van de vorige D FF is groter dan de vasthoudtijd.

Gegevens op D gedreven door een andere etappe Q zal niet sneller veranderen dan 200ns voor de CD4006b.

Om samen te vatten, output Q volgt invoer D op bijna kloktijd als Flip-Flops worden gecascadeerd in een meertraps schuifregister.

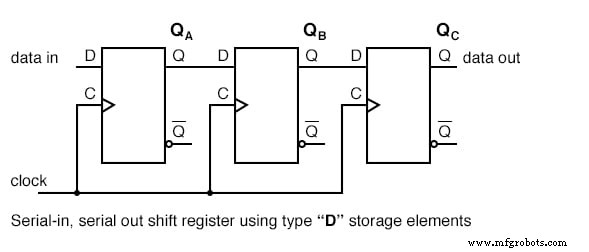

Drie typen D Flip-Flops lopen in cascade van Q naar D en de klokken lopen parallel om een drietraps schuifregister hierboven te vormen.

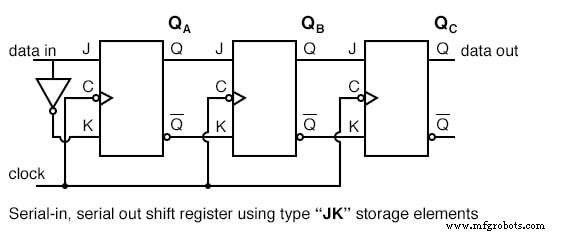

Typ JK Flip Flopss cascadeerde Q naar J, Q' naar K met klokken parallel om een alternatieve vorm van het bovenstaande schuifregister op te leveren.

Een serieel-in/seriële-uit schuifregister heeft een klokinvoer, een gegevensinvoer en een gegevensuitvoer van de laatste trap.

Over het algemeen zijn de andere trapuitgangen niet beschikbaar. Anders zou het een serieel-in, parallel-uit schuifregister zijn.

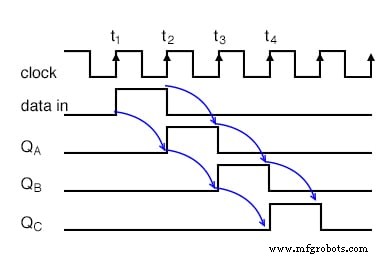

De onderstaande golfvormen zijn van toepassing op een van de voorgaande twee versies van het serieel-in, serieel-uit schuifregister.

De drie paar pijlen laten zien dat een drietraps schuifregister tijdelijk 3-bits gegevens opslaat en deze met drie klokperioden vertraagt van invoer naar uitvoer.

Op kloktijd t1 een “data in” van 0 wordt geklokt vanaf D naar Q van alle drie de fasen. In het bijzonder D van fase A ziet een logische 0 , die wordt geklokt naar QA waar het blijft tot tijd t2 .

Op kloktijd t2 een "data in" van 1 wordt geklokt vanaf D naar QA . In stadia B en C , een 0 , gevoed vanuit voorgaande etappes wordt geklokt naar QB en QC .

Op kloktijd t3 een “data in” van 0 wordt geklokt vanaf D naar QA . QA gaat laag en blijft laag voor de resterende klokken omdat "data in" 0 is . QB gaat hoog op t3 vanwege een 1 uit de vorige fase. QC is nog steeds laag na t3 vanwege een dieptepunt uit de vorige fase.

QC gaat eindelijk hoog op klok t4 vanwege de hoge toevoer naar D uit de vorige fase QB . Alle eerdere fasen hebben 0 s verschoven in hen. En, na de volgende klokpuls op t5 , alle logica 1 s zullen zijn verschoven, vervangen door 0 s

Serial-in/serial-out apparaten

We zullen de volgende onderdelen die beschikbaar zijn als geïntegreerde schakelingen, met dank aan Texas Instruments nader bekijken.

Volg de links voor volledige apparaatgegevensbladen.

- CD4006b 18-bit serieel-in/serieel-uit schuifregister

- CD4031b 64-bit serieel-in/serieel-uit schuifregister

- CD4517b dubbel 64-bit serieel-in/serieel-uit schuifregister

De volgende serie-in/serieel-uit schuifregisters zijn 4000 series CMOS (Complementaire Metal Oxide Semiconductor) familie onderdelen.

Als zodanig accepteren ze een VDD , positieve voeding van 3 Volt tot 15 Volt. De VSS pin is geaard.

De maximale frequentie van de ploegenklok, die varieert met VDD , is een paar megahertz.

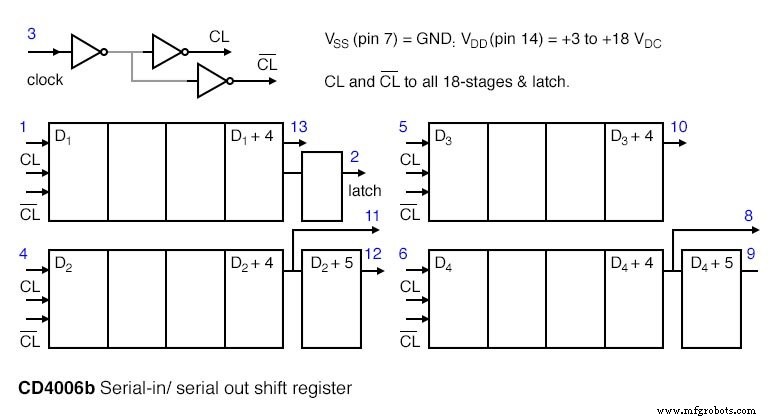

De 18-bits CD4006b bestaat uit twee fasen van 4-bits en nog twee fasen van 5-bits met een uitgangsaftakking op 4-bits.

De 5-bits trappen kunnen dus worden gebruikt als 4-bits schuifregisters.

Om een volledig 18-bits schuifregister te krijgen, moet de uitvoer van het ene schuifregister worden gecascadeerd naar de invoer van een ander, enzovoort, totdat alle fasen een enkel schuifregister vormen, zoals hieronder wordt weergegeven.

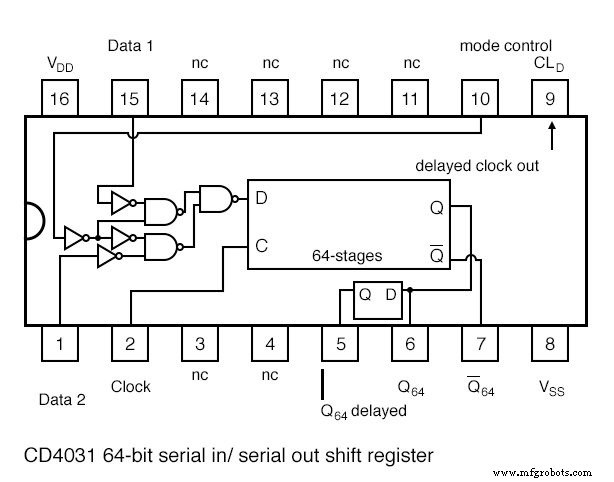

Een CD4031 64-bit serieel-in/serieel-uit schuifregister wordt hieronder getoond.

Een aantal pinnen is niet aangesloten (nc). Zowel Q als Q' zijn beschikbaar vanaf de 64e fase, eigenlijk Q64 en Q'64 .

Er is ook een Q64 "vertraagd" van een halve fase die is vertraagd met een halve klokcyclus. Een belangrijk kenmerk is een gegevenskiezer die zich bij de gegevensinvoer voor het schuifregister bevindt.

De “mode control” selecteert tussen twee inputs:data 1 en data 2. Als “mode control” hoog is, worden data geselecteerd uit “data 2” voor invoer in het schuifregister.

In het geval dat "mode control" logisch laag is, wordt "data 1" geselecteerd. Voorbeelden hiervan worden getoond in de twee onderstaande afbeeldingen.

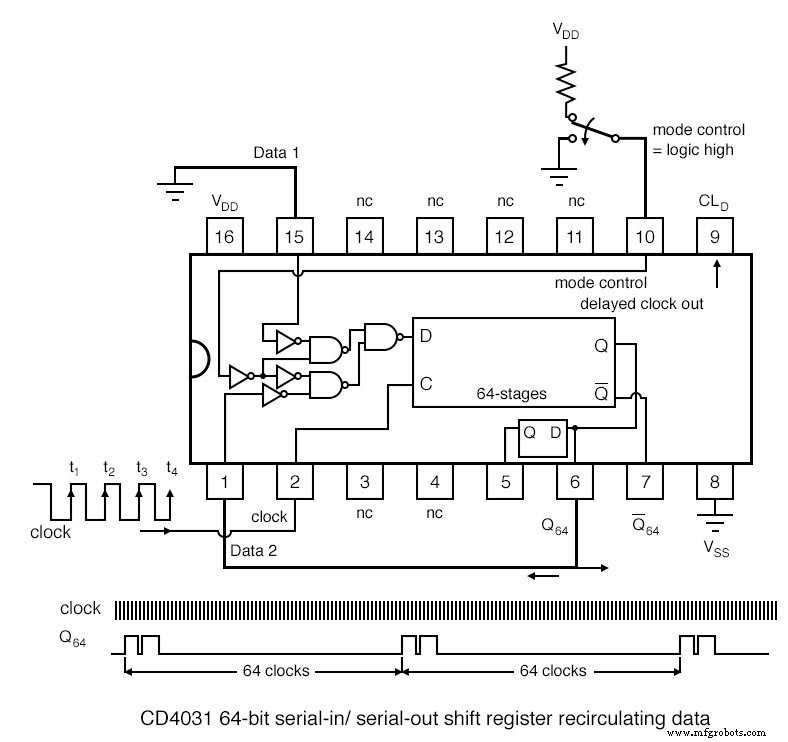

De "data 2" hierboven is aangesloten op de Q64 uitgang van het schuifregister. Met "mode control" hoog, de Q64 output wordt teruggestuurd naar de shifter data input D.

Gegevens zullen recirculeren van uitgang naar ingang. De gegevens worden elke 64 klokpulsen herhaald, zoals hierboven weergegeven.

De vraag die rijst is hoe dit gegevenspatroon in de eerste plaats in het schuifregister is gekomen?

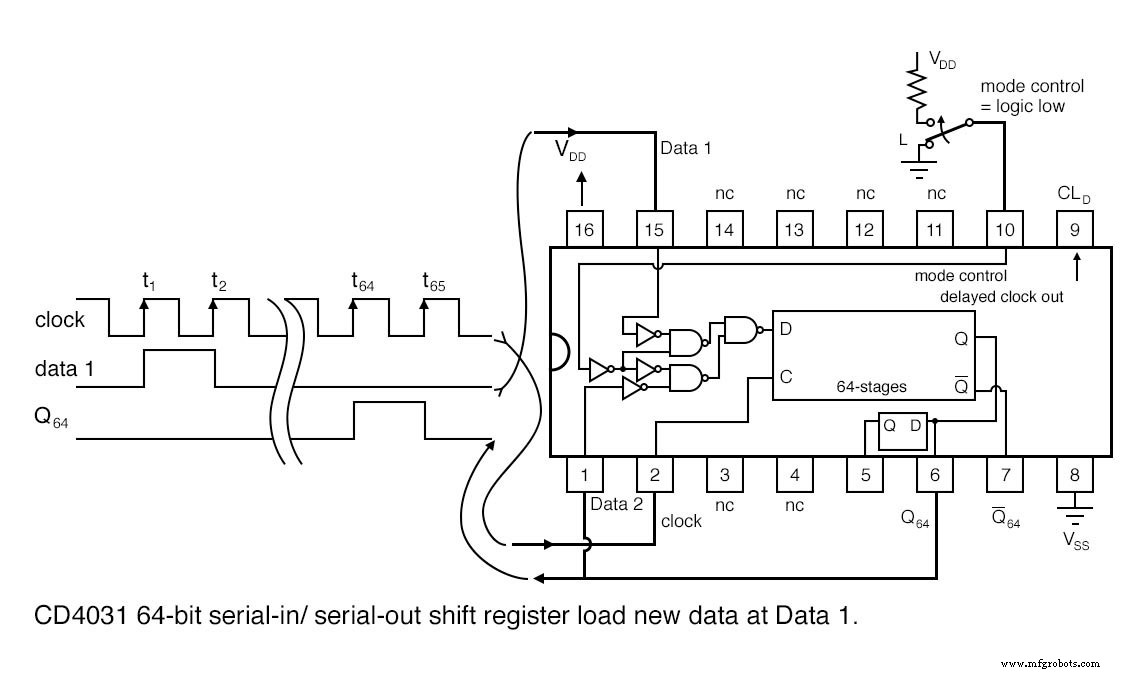

Met "mode control" laag, wordt de CD4031 "data 1" geselecteerd voor invoer naar de shifter.

De uitvoer, Q64 , wordt niet opnieuw gecirculeerd omdat de onderste gegevensselectiepoort is uitgeschakeld .

Met uitgeschakeld bedoelen we dat de logische lage "modusselectie" tweemaal omgekeerd naar een laag bij de onderste NAND-poort, voorkomt dat het een signaal op de onderste pin (data 2) naar de poortuitgang doorgeeft.

Het is dus uitgeschakeld.

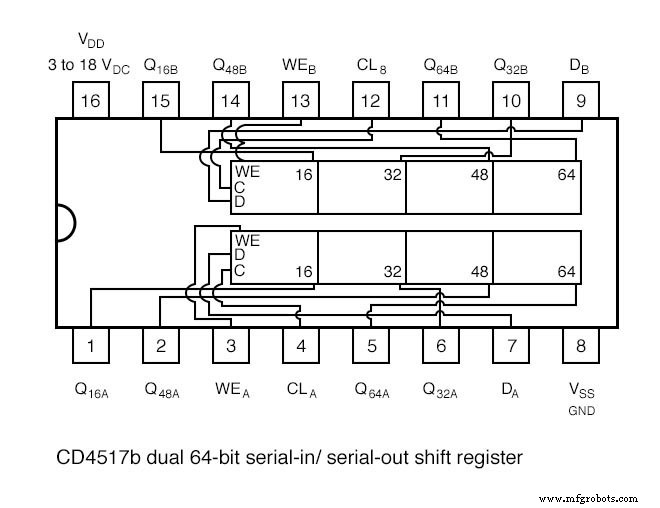

Een CD4517b dubbel 64-bit schuifregister wordt hierboven getoond. Let op de taps in de 16e, 32e en 48e fase.

Dat betekent dat schuifregisters van die lengtes kunnen worden geconfigureerd vanaf een van de 64-bits shifters.

Natuurlijk kunnen de 64-bits shifters worden gecascadeerd om een 80-bits, 96-bits, 112-bits of 128-bits schuifregister te verkrijgen.

De klok CLA en CLB moeten parallel worden geschakeld bij het cascaderen van de twee shifters. WIJB en WEB zijn geaard voor normale schakelhandelingen.

De gegevensinvoer naar de schuifregisters A en B zijn DA en DB respectievelijk.

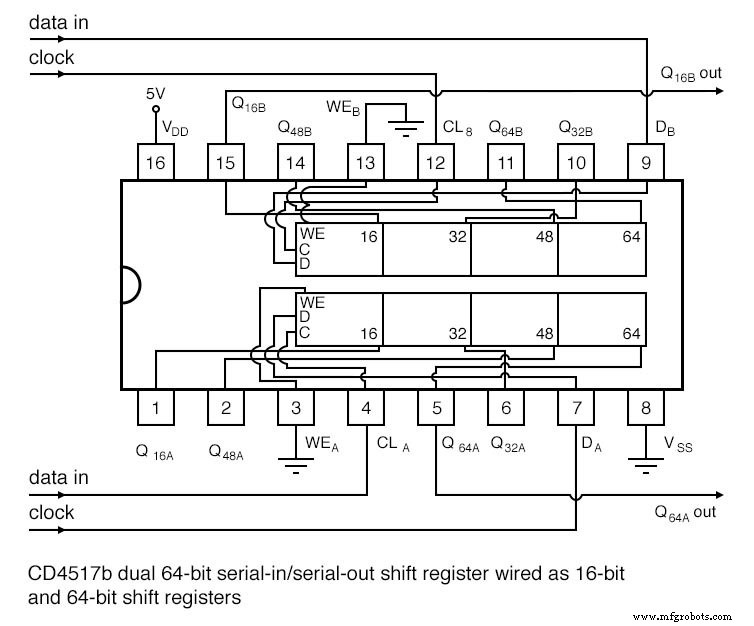

Stel dat we een 16-bits schuifregister nodig hebben.

Kan dit worden geconfigureerd met de CD4517b? Wat dacht je van een 64-shift register van hetzelfde part?

Hierboven tonen we A CD4517b bedraad als een 16-bits schuifregister voor sectie B.

De klok voor sectie B is CLB . De gegevens worden ingeklokt bij CLB . En de gegevens die met 16 klokken zijn vertraagd, zijn afkomstig van Q16B . WIJB , de schrijfmogelijkheid, is geaard.

Hierboven tonen we dezelfde CD4517b bedraad als een 64-bits schuifregister voor de onafhankelijke sectie A.

De klok voor sectie A is CLA . De gegevens komen binnen bij CLA . De gegevens die met 64 klokpulsen zijn vertraagd, worden opgehaald uit Q64A . WIJA , de schrijfmogelijkheid voor sectie A, is geaard.

GERELATEERDE WERKBLAD:

- Werkblad Ploegregisters

Industriële technologie