De programmeeroptimalisatie van condensatorloze 1T DRAM op basis van de Dual-Gate TFET

Abstract

Het grotere condensatorvolume en de hogere lekstroom van de transistor zijn de inherente nadelen geworden van het traditionele dynamische willekeurig toegankelijke geheugen (DRAM) met één transistor (1T) en één condensator (1C). Onlangs is de tunneling FET (TFET) toegepast in DRAM-cellen vanwege de lage stroom uit de staat en de hoge schakelverhouding. De dual-gate TFET (DG-TFET) DRAM-cel met de condensatorloze structuur heeft de superieure prestatie-hogere retentietijd (RT) en zwakke temperatuurafhankelijkheid. Maar de prestaties van de TFET DRAM-cel zijn gevoelig voor de programmeerconditie. In dit artikel wordt de richtlijn voor programmeeroptimalisatie in detail besproken met behulp van de simulatietool Silvaco Atlas. Zowel de schrijf- als leesbewerkingen van DG-TFET DRAM zijn afhankelijk van band-naar-band tunneling (BTBT). Tijdens het schrijven worden de gaten die afkomstig zijn van BTBT die wordt beheerd door Gate2 opgeslagen in een potentiaalput onder Gate2. Bij Gate2 wordt een kleine negatieve spanning aangelegd om de gaten lang vast te houden tijdens het vasthouden van "1". De door Gate1 aangestuurde BTBT heeft vooral invloed op de leesstroom. Met behulp van de geoptimaliseerde programmeerconditie verkrijgt de DG-TFET DRAM de hogere stroomverhouding van het lezen van "1" tot het lezen van "0" (10 7 ) en RT van meer dan 2 s. De hogere RT vermindert de verversingssnelheid en het dynamische stroomverbruik van DRAM.

Achtergrond

Het dynamische willekeurig toegankelijke geheugen (DRAM) is een integrale geheugencel geworden in het mobiele en computersysteem [1,2,3]. Met de krimp van de geometrie van het apparaat, is het grote volume van de condensator een inherent nadeel voor de traditionele DRAM-cel met één transistor (1T) en één condensator (1C), wat de grootschalige toepassing ervan beperkt. De condensatorloze 1T DRAM-cel op basis van de zwevende-poorttransistor heeft het potentiële voordeel aangetoond in vergelijking met de conventionele 1T-1C DRAM voor de verpakking van geheugen met hoge dichtheid [4]. In de zwevende-poorttransistor worden de ladingen in het substraatgebied opgeslagen in het zwevende-poortgebied door de Fowler-Nordheim-tunneling. En de leesbewerking hangt af van de thermionische emissie [5, 6], die hetzelfde is als de metaaloxide-halfgeleider-veldeffecttransistor (MOSFET). Hierdoor is de leesstroom van de DRAM met de floating-gate transistor sterk temperatuurafhankelijk. Bovendien zorgt de thermionische emissie ervoor dat de subthreshold swing (SS) van de transistor hoger is dan 60 mV/dec, waardoor de hoge lekstroom en het stroomverbruik de grootste uitdagingen worden [7,8,9].

Onlangs werd de tunneling-veldeffecttransistor (TFET) beschouwd als een veelbelovende kandidaat voor de toekomstige elektrische apparaten met laag vermogen [10,11,12]. Het belangrijkste geleidingsmechanisme van TFET is band-to-band tunneling (BTBT) in plaats van thermionische emissie, waardoor het de verschillende voordelen verkrijgt, zoals de sub-60 mV / dec SS, lage lekstroom buiten de toestand en zwakke temperatuurafhankelijkheid [13, 14]. Tot dusverre zijn grote hoeveelheden onderzoekswerk over TFET voornamelijk gericht op het onderzoek naar de apparaatprestaties van enkele TFET's en enkele eenvoudige circuits bestaan uit de TFET's. Echter, de hoge I aan /Ik uit van de TFET maakt het mogelijk om te dienen voor de DRAM-cel [15]. Vooral de lage lekstroom uit de staat kan de leesstroom "0" en het stroomverbruik van de DRAM-cel verminderen. De onderzoekers hebben een dual-gate TFET (DG-TFET) DRAM ontworpen met de condensatorloze structuur [16]. In de DG-TFET DRAM is de ladingsopslag tijdens het schrijven gebaseerd op de BTBT tussen het kanaal en de afvoer, die voornamelijk wordt geproduceerd door Gate2. Tegelijkertijd bevordert het tunnelen van elektronen de accumulatie van gaten in het kanaalgebied onder Gate2. Gate1 is voornamelijk verantwoordelijk voor het lezen. De leesstroom van DGTFET DRAM is voornamelijk afhankelijk van de BTBT tussen het brongebied en het kanaalgebied. Er zijn enkele onderzoeksgroepen die hebben aangetoond dat de leesstroom van DG-TFET DRAM een zwakke afhankelijkheid van temperatuur heeft. En DG-TFET DRAM kan een retentietijd behalen die hoger is dan het doel (64 ms) [17]. Maar de huidige verhouding van het lezen van "1" tot het lezen van "0" en RT zijn niet de optimale waarde vanwege de niet-geoptimaliseerde programmeerconditie.

De prestaties van TFET DRAM, met name de huidige verhouding tussen het lezen van "1" en het lezen van "0", zijn sterk afhankelijk van de programmeerconditie. Gate2 beïnvloedt voornamelijk de BTBT tijdens de schrijfbewerking, die het opslaggebied van ladingen en potentiaal ruim onder Gate2 domineert. Gate1 bestuurt de BTBT tijdens de leesbewerking, die voornamelijk de leesstroom "1" beïnvloedt. Door de juiste vooroordelen van zowel Gate1 als Gate2 kan DGTFET DRAM de hogere stroomverhouding verkrijgen. Er is wat literatuur die de invloed van de programmeerconditie op de leesstroom bestudeert. In dit artikel wordt een gedetailleerde richtlijn voor programmeeroptimalisatie voorgesteld, inclusief schrijf-, houd- en leesbewerkingen. Door de geoptimaliseerde programmeerconditie toe te passen, verkrijgt de DG-TFET DRAM de optimale prestaties:de leesstroomverhouding van maximaal 10 7 en de RT van meer dan 2 s. En door de geoptimaliseerde programmeerspanning toe te passen, is de leesstroom "0" veel lager dan die vermeld in referentie [16, 18], wat handig is voor het verminderen van het stroomverbruik.

Methoden

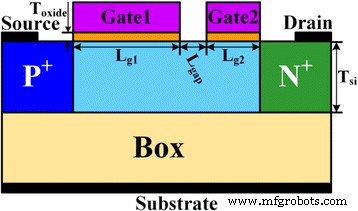

De structuur van DG-TFET die in dit artikel wordt onderzocht, wordt geïllustreerd in Fig. 1. De dopingconcentratie van zowel de P + bron en N + afvoer is 1 × 10 20 /cm 3 . Het intrinsieke kanaal is verdeeld in twee segmenten:Gate1 en Gate 2, en er is een korte opening tussen Gate1 en Gate2. Gate1 en Gate2 zijn N + polysilicium en P + respectievelijk polysilicium. De P + polysilicium Gate2 kan de fysieke bron creëren en onderhouden voor ladingopslag en om de conventionele op TFET gebaseerde DRAM te vervangen die gebruikmaakt van een P + zakgebied als opslagruimte. Terwijl voor een N + polysilicium Gate1, de gatenconcentratie in het onderlappingsgebied tussen Gate1 en Gate2 is laag, wat handig is voor de leesbewerking. Dus een P + polysilicium Gate2 is gekozen om een dieper opslaggebied te hebben dat langere retentie zou kunnen vergemakkelijken, terwijl een N + polysilicium Gate1 is geselecteerd om het tunnelmechanisme te besturen tijdens het lezen [18].

Schema van DG-TFET DRAM-cel. Deze afbeelding toont het schema van een dual-gate TFET (DGTFET) DRAM-cel, inclusief Gate1, Gate2, source, drain en channel. In dit ontwerp zijn het brongebied en het afvoergebied P + doping en N + doping, respectievelijk. Gate1 en Gate2 zijn N + polysilicium en P + polysilicium, respectievelijk

De gedetailleerde apparaatparameters in de simulaties zijn als volgt:de dikte van bulksilicium (T si ) is 20 nm; de lengtes van Gate1 (Lg1 ) en Gate2 (Lg2 ) zijn respectievelijk 400 nm en 200 nm; de lengte van de opening (L kloof ) tussen Gate1 en Gate2 is 50 nm; de dikte van poortoxide (HfO2 ) (T oxide ) is 3 nm. De geoptimaliseerde programmeervoorwaarden worden weergegeven in Tabel 1. De optimalisatierichtlijnen van de programmeervoorwaarden worden in de volgende paragrafen in detail besproken.

Alle analyses worden uitgevoerd in de Silvaco-Atlas-tool met behulp van het niet-lokale BTBT-model [19]. De niet-lokale BTBT houdt rekening met de niet-lokale generatie van elektronen en gaten, zodat het tunnelproces nauwkeuriger kan worden gemodelleerd. De parameters van het tunnelmodel zijn gekalibreerd volgens de experimentele gegevens in de referentie [20]. Bovendien worden ook fysieke modellen gebruikt, waaronder Shockley-Read-Hall-recombinatie, Fermi-statistieken en doping en elektrisch veldafhankelijke mobiliteit. Volgens de benaderingen van [16, 18] zijn de elektron- en gatlevensduur ingesteld op 100 ns. De standaardtemperatuur is 300 K.

Resultaten en discussie

Het werkingsprincipe van de DG-TFET DRAM-cel is anders dan die van de traditionele DRAM. Zowel de schrijf- als leesbewerkingen zijn gebaseerd op de BTBT, maar hebben elk een andere functie. De BTBT tijdens het schrijven van "1" leidt ertoe dat de gaten worden opgeslagen in de potentiaalput onder Gate2, wat de leesstroom "1" kan verhogen. Tijdens het uitlezen hangt de afvoerstroom voornamelijk af van de BTBT nabij de bronzijde. Verder fungeren de twee poorten ook als de verschillende rollen:Gate1 en Gate2 bepalen voornamelijk respectievelijk de lees- en schrijfbewerking.

Schrijfbewerking

Tijdens het schrijven van "1" zal Gate2 met de negatieve bias de energieband van kanaal onder Gate2 versterken, waardoor de barrièrebreedte kleiner wordt en de BTBT tussen het kanaal en de afvoer wordt geproduceerd. En deze negatieve Gate2-bias veroorzaakt ook een diepe potentiaalbron onder Gate2. Door het tunnelen van elektronen van het kanaal naar de afvoer, is het kanaalgebied onder Gate2 volledig uitgeput en worden er veel gaten geaccumuleerd in deze potentiaalput. Tijdens het schrijven van "0" zorgt Gate2 met de positieve voorspanning ervoor dat de gaten uit de potentiaalput verdrijven die zich aan de afvoerzijde recombineert [21].

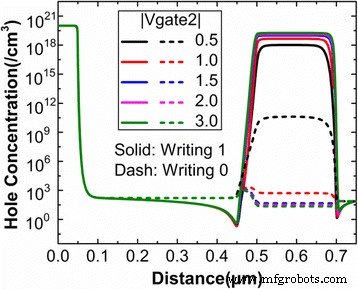

Over het algemeen blijft de absolute waarde van Gate2-spanning ongewijzigd voor het schrijven van "1" en schrijven van "0". Figuur 2 toont de variatie van de gatenconcentratie met de Gate2-spanning na de schrijfbewerking. Wanneer de Gate2-spanning 0,5 V is, is de gatenconcentratie na het schrijven van "0" hoger vanwege de aanwezigheid van een potentiaalbron, wat nadelig is voor de toestand "0". Wanneer de absolute waarde van de Gate2-spanning hoger is dan 1 V, heeft de gatenconcentratie na zowel het schrijven van "0" als het schrijven van "1" geen duidelijke variatie. Het suggereert dat BTBT verzadigd is voor het schrijven van "1" en dat alle geaccumuleerde gaten tijdens het schrijven van "1" uit de potentiaalbron verdrijven na het schrijven van "0". En het verschil in gatenconcentratie tussen het schrijven van "1" en het schrijven van "0" is heel duidelijk, wat gunstig is voor het onderscheid tussen de staat "1" en staat "0".

Gatenconcentraties op het oppervlak van het kanaal na schrijfbewerking. Deze afbeelding toont de variaties van de gatenconcentratie met de verschillende Gate2-spanningen. De snijlijn wordt aan het oppervlak van het apparaat genomen van het brongebied naar het afvoergebied. In deze afbeelding vertegenwoordigen de ononderbroken lijn en de streepjeslijn de gatenconcentratie na respectievelijk het schrijven van "1" en het schrijven van "0"

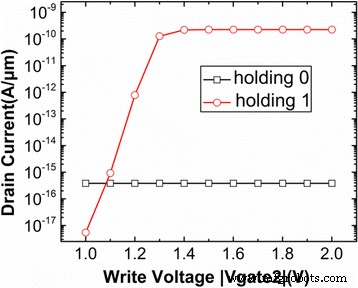

Maar de Gate2-bias tijdens het schrijven kan niet alleen worden bepaald door de gatenconcentratie. Afbeelding 3 geeft aan dat Gate2-bias tijdens het schrijven een significant effect heeft op de afvoerstroom na het vasthouden. De set programmeerspanningen tijdens het vasthouden wordt in de volgende sectie besproken. Figuur 3 laat zien dat de afvoerstroom na vasthouden geen duidelijke variatie heeft wanneer de absolute waarde van de schrijfspanning hoger is dan 1,3 V. Daarom worden de -1,3 en 1,3 V beschouwd als de optimale Gate2-spanning tijdens het schrijven van "1" en door respectievelijk “0” te schrijven.

De stroom van DG-TFET aftappen nadat u "0" ingedrukt heeft gehouden en "1" ingedrukt heeft gehouden. Deze afbeelding toont de variatie van de afvoerstroom na het vasthouden van "0" en het vasthouden van "1" met betrekking tot schrijfspanning

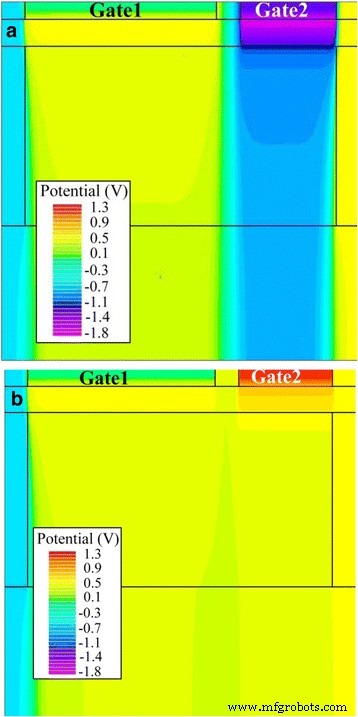

Figuur 4a, b geeft respectievelijk de potentiaalcontour aan na het schrijven van "1" en het schrijven van "0" wanneer de absolute waarde van de schrijfspanning 1,3 V is. Het is duidelijk dat er een zeer diepe potentiaalput wordt gecreëerd in het kanaalgebied onder Gate2 na het schrijven " 1”, zoals getoond in Fig. 4a. De geaccumuleerde gaten worden tijdens het schrijven van "1" in deze potentiaalput bewaard. De opgehoopte gaten ontsnappen echter uit deze potentiaalput tijdens het schrijven van "0".

Potentiële contouren na a schrijven "1" en b schrijven "0" wanneer de absolute waarde van Gate2-spanning 1,3 V is. a , b De potentiële contouren na het schrijven van respectievelijk "1" en "0". De potentiële contouren in deze afbeelding worden geëxtraheerd wanneer de absolute waarde van Gate2-spanning is ingesteld op 1,3 V

Houderbewerking

Het holdingproces wordt voornamelijk gebruikt om de inhouding van de kosten te wijzigen. Gewoonlijk wordt de nulinstelling gebruikt tijdens het vasthouden om het stroomverbruik te verminderen [22]. Tijdens het vasthouden worden de geaccumuleerde gaten in de potentiaalput geleidelijk opnieuw gecombineerd als gevolg van de afname van de potentiaalputdiepte. Daarom is het belangrijkste doel van de optimalisatie van de vasthoudwerking om recombinatie van gaten tijdens het vasthouden van "1" te voorkomen. In dit ontwerp wordt een kleine negatieve bias toegepast bij Gate2 om gaten in de potentiaalput vast te houden nadat "1" is vastgehouden, terwijl de potentiaalput geen gaten meer heeft na het vasthouden van "0".

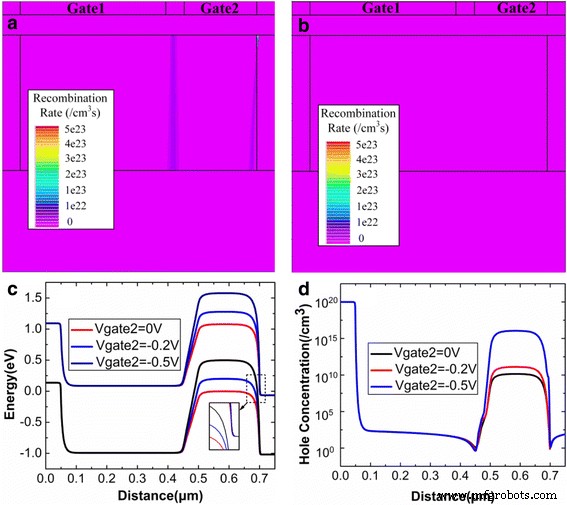

Met de meer negatieve Gate2-spanning (−0,5 V) tijdens het vasthouden, wordt de recombinatie van gaten geëlimineerd na het vasthouden van "1", zoals weergegeven in Fig. 5a, b. De eliminatie van recombinatie van gaten is gunstig voor het vasthouden van gaten tijdens het vasthouden van "1". Bij Gate2 wordt een kleine negatieve bias toegepast om de potentiële putdiepte te vergroten en gaten voor een lange tijd vast te houden, wat gunstig is voor de retentietijd van DGTFET DRAM. Tijdens het vasthouden van "0" kan een negatieve Gate2-bias de energieband van het kanaalgebied onder Gate2 omhoog trekken, wat kan voorkomen dat elektronen die van BTBT komen tussen de bron en het kanaal naar de afvoerzijde stromen. Daarom kan Gate2 met een negatief de leesstroom "0" verminderen. Gate2 met meer negatieve spanning (−0,5 V) vermindert echter de tunnelafstand nabij de afvoerzijde, zoals weergegeven in figuur 5c. Deze verminderde tunnelafstand veroorzaakt de BTBT nabij de afvoerzijde tijdens het vasthouden "0", wat de accumulatie van gaten in de potentiaalput tijdens het vasthouden "0" bevordert, zoals weergegeven in Fig. 5d. Dus de meer negatieve Gate2-spanning (−0,5 V) tijdens het vasthouden van "0" zal de toestand "0" degraderen. Om de recombinatie van gaten en BTBT te elimineren tijdens respectievelijk "1" en "0" vasthouden, wordt −0,2 V beschouwd als de optimale Gate2-bias tijdens het vasthouden.

Recombinatiesnelheid in DG-TFET DRAM-cel na vasthouden van "1" wanneer de Gate2-spanning a is 0 V en b −0,5 V; c energiebanddiagram en d gatenconcentratie na het vasthouden van "0". een , b De recombinatiesnelheid na het vasthouden van "1" wanneer de Gate2-spanning is ingesteld op respectievelijk 0 V en -0,5 V. c De energieband van het apparaat van het brongebied naar het afvoergebied. d De gatenconcentratie van het apparaat na het doorboren van "0". De energieband en de gatenconcentratie worden geëxtraheerd op de 3 nm onder het poortoxide

Leesbewerking

Vervolgens wordt ook de optimalisatie van de leeswerking onderzocht. De leesbewerking is sterk afhankelijk van de BTBT tussen de P + bron en kanaal. Tijdens de lezing "1" bevordert Gate1 voornamelijk de BTBT aan de bronzijde, terwijl Gate2 met de hoge spanning de energiebarrière verlaagt die weerstand biedt aan het stromen van elektronen van het kanaal naar de afvoer. Maar tijdens de lezing "0", is het noodzakelijk dat Gate2 met de kleine spanning kan voorkomen dat elektronen uit het kanaal naar de afvoer stromen. Daarom is de optimalisatie van zowel de Gate1- als Gate2-spanningen erg belangrijk voor de leesbewerking.

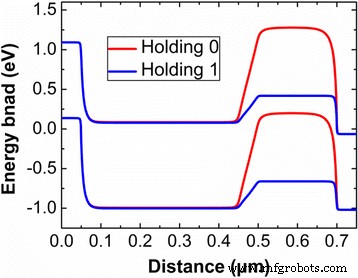

Afbeelding 6 toont de verschillende energiebanddiagrammen nadat u "1" ingedrukt heeft gehouden en "0" ingedrukt hebt gehouden. Dezelfde spanningen worden aan de Gate-zijden toegepast tijdens het lezen van "1" en het lezen van "0". Aangezien de positieve Gate-bias wordt gebruikt tijdens het lezen, zal de energieband worden verlaagd wanneer "1" of "0" wordt gelezen. De energieband van kanaal onder Gate2 na het vasthouden van "0" is hoger dan die na het vasthouden van "1", en deze energieband is ook hoger tijdens het lezen van "0" vergeleken met die tijdens het lezen van "1". De hogere energie van het kanaal onder Gate2 zal een effectieve barrière creëren om weerstand te bieden aan elektronen die naar de afvoerzijde stromen, waardoor de leesstroom "0" zal afnemen.

Energiebanddiagram na a houd "1" en b . ingedrukt “0” vasthouden. een , b De energieband van het apparaat nadat respectievelijk "1" en "0" ingedrukt zijn. De energieband wordt geëxtraheerd op de 3 nm onder het poortoxide

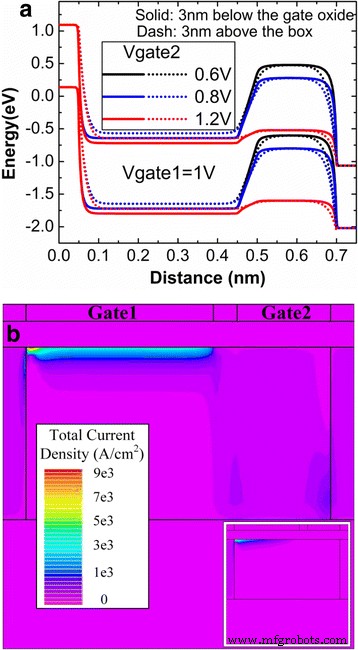

Tijdens het uitlezen wordt de drain-bias ingesteld op 1 V, zodat de drain-stroom in de DG-TFET kan worden uitgelezen. Ten eerste, houd de Gate1-spanning van 1 V aan en verander de bias van Gate2 om de optimale Gate2-spanning te kiezen. Omdat de Gate2-spanning voornamelijk de afleesstroom "0" beïnvloedt, wordt de optimalisatie van de Gate2-spanning geanalyseerd door het afleesmechanisme "0". Afbeelding 7a geeft de variatie van de energieband weer met de Gate2-spanning na het lezen van "0". Wanneer de Gate2-spanning lager is (0,6 of 0,8 V), raakt het kanaal onder Gate2 volledig uitgeput. Maar wanneer de Gate2-spanning stijgt tot 1,2 V, kan de neerwaartse energieband van het kanaal onder Gate2 geen effectieve barrière vormen om te voorkomen dat elektronen naar de afvoerzijde stromen. Figuur 7b en zijn inzet tonen respectievelijk de totale stroomdichtheid na het lezen van "0" wanneer de Gate2-spanning 1V en 0,8 V is. De voor de hand liggende stroomdichtheid is duidelijk te vinden in het kanaalgebied onder Gate2 wanneer de Gate2-spanning 1 V is, wat zal aanleiding geven tot de hogere aflezing "0" stroom. Dus de 0,8 V wordt beschouwd als de optimale Gate2-spanning voor het leesproces.

een Energiebanddiagram en b totale stroomdichtheid na het lezen van "0". een , b De energieband en de totale stroomdichtheid na het lezen van respectievelijk "0". De energieband wordt geëxtraheerd op de 3 nm onder het poortoxide

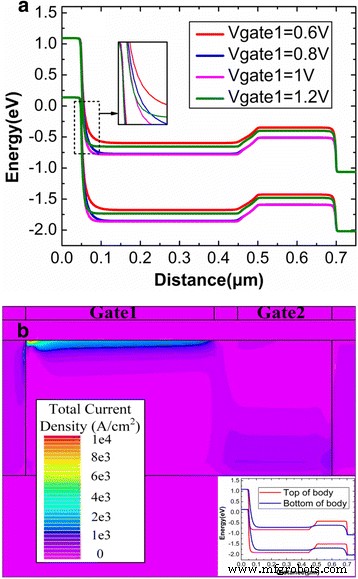

Ten slotte wordt ook de optimalisatie van de Gate1-bias uitgevoerd. Figuur 8a toont de variatie van de bovenste energieband met de Gate1-spanning. De breedte van de BTBT-barrière aan de bronzijde neemt geleidelijk af met de toename van de Gate1-spanning, maar deze afnemende trend begint te verzadigen wanneer de Gate1-spanning hoger is dan 1 V. En de Gate1-spanning van 1 V kan geen grote invloed hebben op het lezen van "0 ” werking, die is aangetoond door Fig. 7b. Daarom wordt 1 V beschouwd als de optimale Gate1-bias tijdens het lezen.

een Energiebanddiagram en b totale stroomdichtheid na het lezen van "1". een , b De energieband en de totale stroomdichtheid na het lezen van respectievelijk "1". De energieband wordt geëxtraheerd op de 3 nm onder het poortoxide

Door de bovenstaande analyse wordt de diepe potentiaalbron pas gevormd aan de bovenkant van het kanaal onder Gate2 na het schrijven van "1". Daarom is in het kanaalgebied onder Gate2 de energieband aan de bovenkant van het kanaal veel hoger dan die aan de onderkant van het kanaal. Dit toont aan dat er een barrière zal zijn aan de bovenkant van het kanaal onder Gate2 tijdens het lezen "1". De inzet van Fig. 8b geeft de energieband weer aan zowel de boven- als onderkant van het kanaal na het lezen van "1". Het is duidelijk te zien dat er een hogere kanaalbarrière bestaat tussen Gate1 en Gate2 aan de bovenkant van het kanaal, maar deze barrière bestaat niet aan de onderkant van het kanaal. Daarom bevindt het geleidingspad zich aan de bovenkant van het kanaal onder Gate1 en de onderkant van het kanaal onder Gate2 tijdens de lezing "1", wat duidelijk kan worden aangetoond door de stroomdichtheid in Fig. 8.

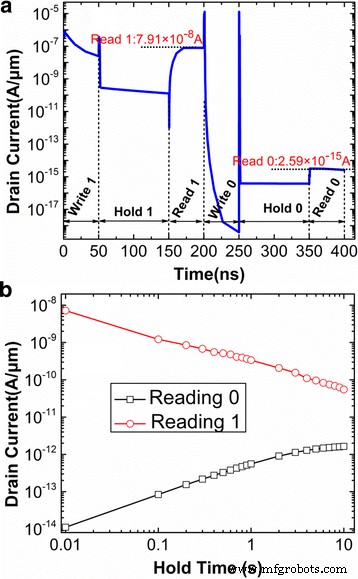

Door de bovenstaande geoptimaliseerde programmeerconditie toe te passen, wordt de tijdelijke respons van de DG-TFET DRAM-cel getoond in Fig. 9. Zowel de schrijf- als leestijden zijn ingesteld op 50 ns en de houdtijd is ingesteld op 100 ns. In Fig. 9a is de huidige verhouding tussen het lezen van "1" en het lezen van "0" zo hoog als 10 7 , wat veel hoger is dan 10 2 ~10 3 in referentie [16, 18, 23]. Bovendien, wanneer de houdtijd stijgt tot 10 s, is de stroomverhouding nog steeds groter dan 10. In referentie [16], wanneer de houdtijd wordt verhoogd tot 2 s, is de stroomverhouding slechts ongeveer 10. Daarom is de RT van DG-TFET DRAM met de geoptimaliseerde programmeerconditie is hoger dan 2 s. Dus de geoptimaliseerde programmeerconditie zorgt ervoor dat de DG-TFET DRAM-cel niet alleen de hogere leesstroomverhouding krijgt, maar ook de grotere RT. Bovendien is de leesstroom "0" met geoptimaliseerde programmeerspanning veel minder dan die in referentie [16, 18, 22, 23], waardoor deze kan voldoen aan de toepassing met lager vermogen.

een Voorbijgaande afvoerstromen in de volgorde van de bewerking; b variatie van de leesstroom met de houdtijd. een De tijdelijke stroom van de DGTFET DRAM-cel tijdens het schrijven, vasthouden en lezen. b De variaties van het lezen van "1" en het lezen van "0" stroom met de verschillende gatentijden

Conclusies

De gedetailleerde optimalisatierichtlijn van de programmeerconditie voor de DG-TFET DRAM wordt in dit artikel voorgesteld met behulp van de Silvaco-Atlas-simulatietool. Tijdens het schrijven van "1" creëert Gate2 met de negatieve spanning (-1,3 V) een potentiaalput, en de BTBT tussen het kanaal en de afvoer zorgt ervoor dat de gaten in deze potentiaalput worden geaccumuleerd. Tijdens het schrijven van "0" laat Gate2 met de positieve spanning (1,3 V) gaten ontsnappen uit de potentiaalbron. Voor de vasthoudbewerking wordt de kleine negatieve spanning (−0,2 V) toegepast bij Gate2 om de gaten vast te houden, wat de leesstroom "1" kan verbeteren. Na het vasthouden van "0", kan de barrière van kanaal onder Gate2 weerstand bieden aan elektronen die naar de afvoerzijde stromen om de leesstroom "0" te verminderen. Voor de optimalisatie van de leesbewerking wordt de grotere Gate1-spanning (1 V) voornamelijk gebruikt om BTBT aan de bronzijde te verbeteren tijdens het lezen van "1", terwijl een geschikte Gate2-spanning (0,8 V) wordt gebruikt om weerstand te bieden aan elektronen die tijdens het lezen naar de afvoer stromen “0”. De geoptimaliseerde programmeerconditie zorgt ervoor dat de DG-TFET DRAM de hogere stroomverhouding krijgt (10 7 ) van het lezen van "1" tot het lezen van "0" en een bewaartijd van meer dan 2 s. En de extreem lage afleesstroom "0" is nuttig voor het verminderen van het stroomverbruik.

Nanomaterialen

- De voordelen van bewaking op afstand, programmering op afstand en voorspellend onderhoud

- De uitdagingen van multicore-programmeren en debuggen aankunnen

- Breadboarden en programmeren van de ATmega328P &ATtiny45 in Atmel Studio 7

- Leer de Embedded C-programmeertaal:het Union Data Object begrijpen

- Gebruikmaken van op IoT gebaseerde technologieën op de bouwplaats

- Biometrisch beveiligingssysteem op basis van de menselijke hartslag

- Commentaar:de methoden van robotprogrammering begrijpen

- Het ontwerp- en implementatieproces voor fabrieksautomatisering

- Vul de lege plek in CNC-programmeeroefening Meerdere bogen

- Vul de blanco CNC-programmeerfreesoefening in

- Vul de blanco CNC-programmeeroefening in