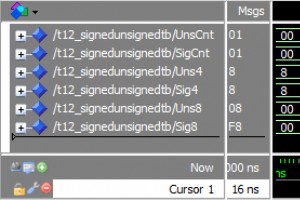

De ondertekende en niet-ondertekende typen in VHDL zijn bitvectoren, net als het type std_logic_vector. Het verschil is dat, hoewel de std_logic_vector geweldig is voor het implementeren van databussen, het nutteloos is voor het uitvoeren van rekenkundige bewerkingen. Als u een nummer probeert toe

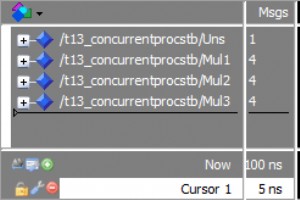

Een gelijktijdige instructie in VHDL is een signaaltoewijzing binnen de architectuur, maar buiten een normale procesconstructie. De gelijktijdige instructie wordt ook wel een gelijktijdige toewijzing of gelijktijdig proces genoemd. Wanneer u een gelijktijdige verklaring maakt, creëert u in feite ee

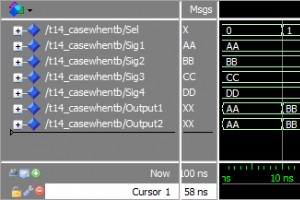

De Case-When-instructie zorgt ervoor dat het programma één van meerdere verschillende paden neemt, afhankelijk van de waarde van een signaal, variabele of uitdrukking. Het is een eleganter alternatief voor een If-Then-Elsif-Else-statement met meerdere Elsifs. Andere programmeertalen hebben vergelij

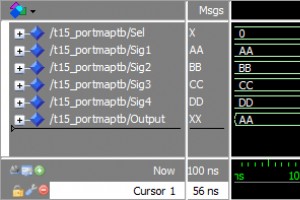

Een module is een op zichzelf staande eenheid van VHDL-code. Modules communiceren met de buitenwereld via de entiteit . Havenkaart is het deel van de module-instantiatie waar u aangeeft op welke lokale signalen de in- en uitgangen van de module moeten worden aangesloten. In eerdere tutorials in dez

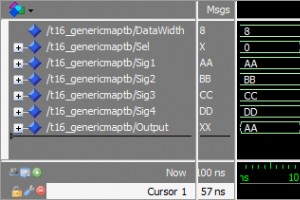

Het maken van modules is een geweldige manier om code opnieuw te gebruiken, maar vaak heb je dezelfde module nodig met kleinere variaties in je ontwerp. Dit is waar generieke geneesmiddelen en de generieke kaart voor zijn. Hiermee kunt u bepaalde delen van de module configureerbaar maken tijdens het

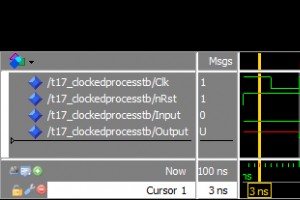

De overgrote meerderheid van VHDL-ontwerpen gebruikt geklokte logica , ook bekend als synchrone logica of sequentiële logica . Een geklokt proces wordt alleen geactiveerd door een hoofdkloksignaal, niet wanneer een van de andere ingangssignalen verandert. De basisbouwsteen van geklokte logica is ee

Test je voortgang met deze VHDL-quiz na het voltooien van tutorials 12-17 uit de Basic VHDL Tutorial-serie! Welke uitspraak is waar over het ondertekende type? Ze kunnen vertegenwoordigen hogere waarden dan niet-ondertekende typen Als de meest linkse bit is 1 de waarde moet negatief zijn O

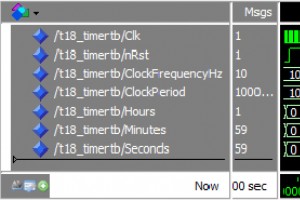

In eerdere tutorials hebben we de wait for . gebruikt verklaring om de tijd in de simulatie te vertragen. Maar hoe zit het met productiemodules? De wait for verklaring kan daar niet voor worden gebruikt. Dat werkt alleen in simulatie omdat we de elektronen in een circuit niet zomaar kunnen vertellen

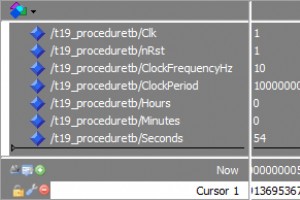

Een procedure is een soort subprogramma in VHDL dat ons kan helpen herhalende code te voorkomen. Soms ontstaat de behoefte om op meerdere plaatsen in het ontwerp identieke bewerkingen uit te voeren. Hoewel het maken van een module misschien overkill is voor kleine bewerkingen, is een procedure vaak

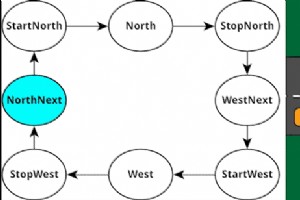

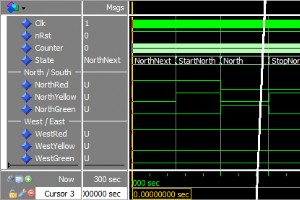

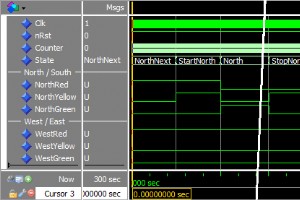

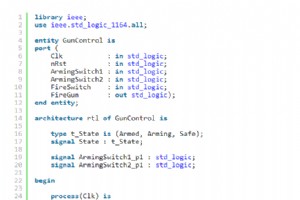

Een eindige-toestandsmachine (FSM) is een mechanisme waarvan de uitvoer niet alleen afhankelijk is van de huidige status van de invoer, maar ook van eerdere invoer- en uitvoerwaarden. Wanneer u een soort tijdsafhankelijk algoritme in VHDL moet maken, of als u wordt geconfronteerd met het probleem v

Functies zijn subprogrammas in VHDL die kunnen worden gebruikt voor het implementeren van veelgebruikte algoritmen. Een functie heeft nul of meer invoerwaarden en retourneert altijd een waarde. Wat een functie behalve de retourwaarde onderscheidt van een procedure, is dat deze geen Wait-statements k

Een onzuivere functie kan elk signaal binnen zijn bereik lezen of schrijven, ook signalen die niet op de parameterlijst staan. We zeggen dat de functie bijwerkingen . heeft . Wat we bedoelen met bijwerkingen is dat het niet gegarandeerd is dat de functie elke keer dat deze wordt aangeroepen met dez

Het is mogelijk om vanuit een procedure externe signalen aan te sturen. Zolang het signaal binnen het bereik van de procedure valt, is het toegankelijk voor lezen of schrijven, zelfs als het niet in de parameterlijst staat. Procedures die zijn gedeclareerd in het declaratieve gebied van de architec

Test je voortgang met deze VHDL-quiz na het voltooien van deel 4 van de serie Basis VHDL-zelfstudies! Hoe meten we realtime in VHDL? Met behulp van een wait for 1 ns statement Door te tellen klokperioden Door misbruik te maken voortplantingsvertraging Juist! Mis! - Welke bewering is waar

De gekoppelde lijst is een dynamische gegevensstructuur. Een gekoppelde lijst kan worden gebruikt wanneer het totale aantal elementen niet van tevoren bekend is. Het groeit en krimpt in het geheugen, in verhouding tot het aantal items dat het bevat. Gelinkte lijsten kunnen het gemakkelijkst worden

Een self-checking testbench is een VHDL-programma dat de juistheid van het te testen apparaat (DUT) verifieert zonder afhankelijk te zijn van een operator om de output handmatig te inspecteren. De zelfcontrolerende testbench werkt volledig zelfstandig en drukt uiteindelijk een bericht OK of Mislukt

Een interactieve testbank is een simulatoropstelling waarbij invoer voor het te testen apparaat (DUT) wordt geleverd door een operator terwijl de testbank draait. Meestal betekent dit dat u commandos moet invoeren in de simulatorconsole om de TU Delft van een stimulans te voorzien. Terwijl je altij

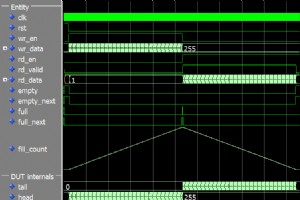

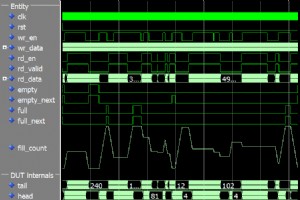

Circulaire buffers zijn populaire constructies voor het maken van wachtrijen in sequentiële programmeertalen, maar ze kunnen ook in hardware worden geïmplementeerd. In dit artikel zullen we een ringbuffer in VHDL maken om een FIFO in blok-RAM te implementeren. Er zijn veel ontwerpbeslissingen die

Beperkte willekeurige verificatie is een testbench-strategie die berust op het genereren van pseudo-willekeurige transacties voor het te testen apparaat (DUT). Het doel is om een functionele dekking van een aantal vooraf gedefinieerde gebeurtenissen te bereiken door middel van willekeurige interac

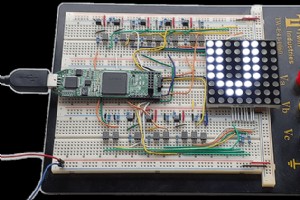

Ik ben verheugd om aan te kondigen dat de VHDL- en FPGA-cursus waar ik de afgelopen zes maanden aan heb gewerkt, voltooid begint te worden. De cursus is momenteel in bèta en ik ben van plan om deze dit najaar voor het eerst te lanceren. Voor wie is de FPGA-cursus? De FPGA-cursus is bedoeld voor de

VHDL