Interactieve testbank met Tcl

Een interactieve testbank is een simulatoropstelling waarbij invoer voor het te testen apparaat (DUT) wordt geleverd door een operator terwijl de testbank draait. Meestal betekent dit dat u commando's moet invoeren in de simulatorconsole om de TU Delft van een stimulans te voorzien.

Terwijl je altijd een zelfcontrolerende testbank moet maken, kan een interactieve testbench een mooie aanvulling zijn. Het is gemakkelijker om ad-hoc testen uit te voeren met een interactieve testbench bij de hand, dan om de code van de zelfcontrolerende testbench te wijzigen.

Vaak kom je in het lab problemen tegen die je in de testbank wilt uitproberen. Met een interactieve testbank kan het net zo eenvoudig zijn als het typen van de invoervolgorde die is waargenomen om het ongewenste gedrag in de simulator te repliceren.

Tcl interactie met VHDL

De meeste VHDL-simulators gebruiken Tcl als hun consoletaal. De simulators hebben een aantal leverancierspecifieke commando's, maar het goede nieuws is dat ze kunnen worden behandeld als elk ander Tcl-commando. U kunt Tcl gebruiken voor het maken van complexe, meestal draagbare scripts voor het beheren en ondersteunen van uw VHDL-testbanken.

VHDL-signalen wijzigen van Tcl

Om te communiceren met VHDL, moeten we de opdracht vinden voor het wijzigen van een signaalwaarde. In ModelSim is dit het commando "force". Zoals gespecificeerd in het referentiedocument voor de opdracht, is de samenvatting voor de opdracht:

force {<object_name> <value> [[@]<time_info>][, <value> [@]<time_info>]...

[-deposit | -drive | -freeze] [-cancel [@]<time_info>] [-repeat [@]<time_info>] De schakelaar die u wilt gebruiken, is de vlag "-deposit". Hierdoor verandert de waarde van het VHDL-signaal onmiddellijk, maar kan een andere VHDL- of Tcl-driver dit op een later tijdstip in iets anders veranderen.

Door de opties die we niet gebruiken te negeren, ziet de vereenvoudigde samenvatting er als volgt uit:

force -deposit <signal_name> <value>

De VHDL-trigger

Nu we weten hoe we VHDL-signalen van Tcl moeten besturen, moeten we een soort ontvangerproces creëren in onze VHDL-testbench. De onderstaande code toont een minimaal voorbeeld van zo'n testbank.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity interactive is

end interactive;

architecture sim of interactive is

-- Controlled by Tcl

signal trigger : std_logic := '0';

begin

process is

begin

wait until trigger = '1';

report "Triggered!";

end process;

end architecture;

Het proces wordt geactiveerd wanneer de trigger signaal verandert van iets naar '1' . Het zal "Triggered!" naar de console wanneer dit gebeurt, waardoor we het concept van het besturen van VHDL-processen van Tcl kunnen testen.

Ik deed alleen dat is de ModelSim-console. De gegeven commando's, evenals de uitvoer, kunnen worden bekeken in het onderstaande transcript.

VSIM 1> run 10 ns; VSIM 2> force -deposit /trigger '1' VSIM 3> run 0 ns; # ** Note: Triggered! # Time: 10 ns Iteration: 0 Instance: /interactive VSIM 4> force -deposit /trigger '0' VSIM 5> run 10 ns;

Ik heb de testbank 10 nanoseconden gedraaid na het starten van de simulatie.

Toen forceerde ik de trigger signaal naar '1' . Op de volgende regel wacht ik 0 nanoseconden. Het doel hiervan is om een deltacyclus te creëren. Ik wil dat het proces wordt geactiveerd, maar ik wil niet dat er simulatietijd verstrijkt.

Ten slotte forceer ik de trigger signaal terug naar '0' voordat u verder gaat met de testbank.

We kunnen zien dat het VHDL-proces wakker werd na de regel "run 0 ns" en "Triggered!" naar de console.

VHDL-signaalwaarden lezen in tcl

Als u signaalwaarden in ModelSim wilt lezen, kunt u de opdracht 'onderzoeken' gebruiken. We kunnen bijvoorbeeld de waarde van de trigger . lezen signaal met dit commando in de ModelSim-console:

VSIM 6> examine /trigger # 0

U zou de waarde aan een Tcl-variabele willen toewijzen wanneer u "examine" in een script gebruikt. Laten we dit proberen in de ModelSim-console:

VSIM 7> set triggerVal [examine /trigger] # 0

Dan kunnen we bijvoorbeeld de variabele uitprinten door het “puts” Tcl commando te gebruiken:

VSIM 8> puts "triggerVal: $triggerVal" # triggerVal: 0

De simulator stoppen na elke test

De eenvoudigste manier om de test lang genoeg uit te voeren zodat de TU Delft kan reageren, is door de simulator gewoon voor een vaste tijdwaarde uit te voeren. Als de DUT bijvoorbeeld zou reageren na twee klokcycli, en de klokperiode is 10 nanoseconden, zouden we het commando "run 20 ns" in ons Tcl-script gebruiken.

Als de TU Delft geen vaste reactietijd heeft, kan een VHDL-bewering worden gebruikt om de simulatie te stoppen en de controle over te dragen aan een Tcl-callback-functie. In ModelSim zou dit betekenen dat u een breekpunt van uw Tcl-script instelt met behulp van de opdracht "when":

when [[-fast] [-id <id#>] [-label <label>] {<when_condition_expression>} {<command>}] Je zou ook een "onBreak" callback-functie in Tcl moeten definiëren die wordt uitgevoerd wanneer het breekpunt wordt bereikt. De functie "onBreak" wordt gespecificeerd in de referentie van de ModelSim-opdracht.

De nadelen van Tcl-gestuurd testen

Er zijn nadelen aan het gebruik van testbanken die sterk afhankelijk zijn van Tcl-scripts. De meest voor de hand liggende zijn de problemen met snelheid en draagbaarheid.

Tcl-gestuurde testbanken werken door de simulator meerdere keren te starten en te stoppen om te communiceren met de VHDL-code. Het starten en stoppen van de simulatie om tussendoor een Tcl-functie uit te voeren, kost meer tijd dan het continu draaien van een VHDL-testbench. Hoewel Tcl een geïnterpreteerde taal is, wordt VHDL in de simulator gecompileerd en werkt het veel sneller dan Tcl.

Hoewel Tcl overdraagbaar is naar andere simulators, zijn de simulatorspecifieke opdrachten die u moet gebruiken, dat niet. Zelfs als u de equivalente opdrachten in de andere simulator vindt, kunnen ze anders werken. Simulatorleveranciers bedenken hun eigen set regels voor de opdrachten die ze ondersteunen. Daarom moet een Tcl-aangedreven testbank als minder draagbaar worden beschouwd dan een pure VHDL-testbank.

Nieuwe VHDL- en FPGA-cursus

* Ik ben een nieuwe VHDL- en FPGA-cursus aan het maken die uitgebreid in testbanken zal duiken. Je leert hoe je vanaf het begin een FPGA-ontwerp maakt. Na het voltooien van de cursus weet u hoe u zelfcontrolerende testbanken kunt maken en hoe u de code kunt hergebruiken om een interactieve testbank te maken.

* Bijgewerkt op 12 oktober 2020: Ik heb de cursus afgerond. Klik op de afbeelding hieronder voor meer informatie.

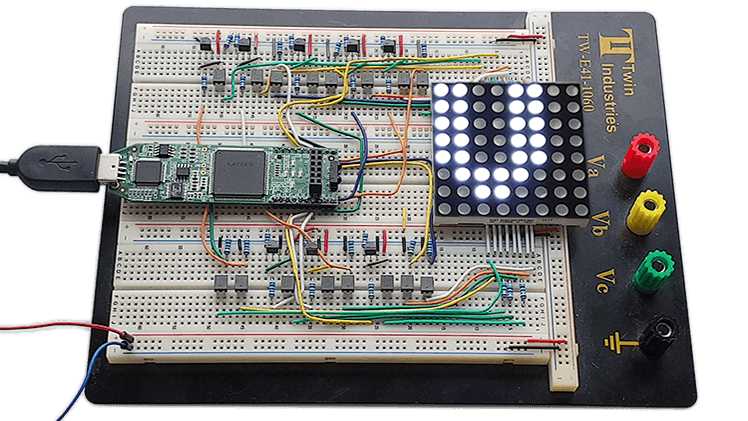

Het product dat we gaan maken is een dot matrix LED-controllermodule. We zullen het Lattice iCEstick-ontwikkelbord van $ 49 gebruiken. Uiteindelijk zullen we het ontwerp implementeren op een breadboard. U kunt typen op het toetsenbord van uw computer en de tekens verschijnen op het dot-matrix LED-scherm dat wordt bestuurd door de FPGA.

Lees hier meer over de Dot Matrix VHDL- en FPGA-cursus!

Opent:

Te bepalen .

VHDL

- Zelfstudie - Inleiding tot VHDL

- Voorbeelden van VHDL-conversies

- Procedureverklaring - VHDL-voorbeeld

- Records - VHDL-voorbeeld

- Ondertekend versus niet-ondertekend in VHDL

- Variabelen - VHDL-voorbeeld

- C# met behulp van

- Een lijst met strings maken in VHDL

- Hoe maak je een zelfcontrolerende testbank aan

- Interactieve laserprojector met Zigbee-sensoren

- Een frees als draaibank gebruiken