Een geklokt proces maken in VHDL

De overgrote meerderheid van VHDL-ontwerpen gebruikt geklokte logica , ook bekend als synchrone logica of sequentiële logica . Een geklokt proces wordt alleen geactiveerd door een hoofdkloksignaal, niet wanneer een van de andere ingangssignalen verandert.

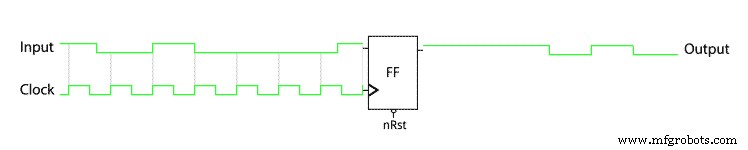

De basisbouwsteen van geklokte logica is een component genaamd de flip-flop . Er zijn verschillende varianten van, en in deze tutorial gaan we ons concentreren op de positieve-edge-getriggerde flip-flop met negatieve reset:

De flip-flop is een sample-and-hold-circuit, wat betekent dat het de waarde van de ingang naar de uitgang kopieert wanneer de stijgende flank van het kloksignaal arriveert. De uitgang wordt dan stabiel gehouden op de gesamplede waarde tot de volgende stijgende flank van de klok, of totdat het resetsignaal wordt gepulseerd.

Deze blogpost maakt deel uit van de serie Basic VHDL Tutorials.

Alle geklokte processen worden gelijktijdig geactiveerd en zullen hun invoer in één keer lezen. Tegelijkertijd zullen ze de resultaten van de laatste iteratie uitvoeren. Het kloksignaal creëert effectief tijdstappen in de gegevensstroom. Dit maakt het voor de ontwerper beheersbaar om complexe, diepe logica te creëren. Hij of zij kan de acties van het algoritme opsplitsen in gebeurtenissen die plaatsvinden op de klokcycli.

Flip-flops of arrays van flip-flops worden soms registers genoemd , het is hetzelfde.

De gevoeligheidslijst voor geklokte processen bevat meestal alleen het kloksignaal. Dit komt omdat een geklokt proces alleen wordt geactiveerd door een flank op het kloksignaal, de andere ingangssignalen zorgen ervoor dat het helemaal niet wordt geactiveerd.

Dit is een sjabloon voor het maken van een geklokt proces met synchrone reset:process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

<reset all output signals here>

else

<main logic here>

end if;

end if;

end process;

Oefening

In deze video-tutorial leren we hoe we een geklokt proces in VHDL kunnen maken:

De definitieve code voor flip-flop testbench :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_ClockedProcessTb is

end entity;

architecture sim of T17_ClockedProcessTb is

constant ClockFrequency : integer := 100e6; -- 100 MHz

constant ClockPeriod : time := 1000 ms / ClockFrequency;

signal Clk : std_logic := '1';

signal nRst : std_logic := '0';

signal Input : std_logic := '0';

signal Output : std_logic;

begin

-- The Device Under Test (DUT)

i_FlipFlop : entity work.T17_FlipFlop(rtl)

port map(

Clk => Clk,

nRst => nRst,

Input => Input,

Output => Output);

-- Process for generating the clock

Clk <= not Clk after ClockPeriod / 2;

-- Testbench sequence

process is

begin

-- Take the DUT out of reset

nRst <= '1';

wait for 20 ns;

Input <= '1';

wait for 22 ns;

Input <= '0';

wait for 6 ns;

Input <= '1';

wait for 20 ns;

-- Reset the DUT

nRst <= '0';

wait;

end process;

end architecture;

De laatste code voor de flip-flop module :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_FlipFlop is

port(

Clk : in std_logic;

nRst : in std_logic; -- Negative reset

Input : in std_logic;

Output : out std_logic);

end entity;

architecture rtl of T17_FlipFlop is

begin

-- Flip-flop with synchronized reset

process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

Output <= '0';

else

Output <= Input;

end if;

end if;

end process;

end architecture;

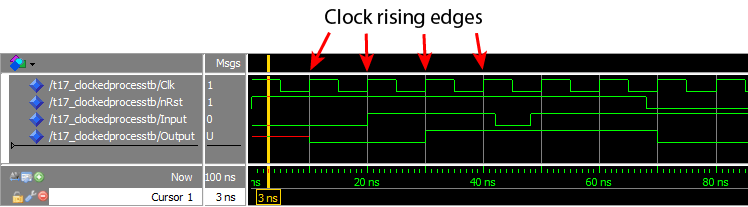

Het golfvormvenster in ModelSim nadat we op run hebben gedrukt en ingezoomd op de tijdlijn:

Analyse

We kunnen aan de golfvorm zien dat het uitgangssignaal alleen wordt bijgewerkt bij elke stijgende flank van het kloksignaal. Het ingangssignaal wordt alleen gesampled wanneer het kloksignaal verandert van '0' naar '1'. De negatieve dip van het ingangssignaal vanaf ongeveer 45 ns gaat volledig verloren. Het wordt niet naar de uitvoer gekopieerd omdat het tussen twee stijgende flanken van de klok ligt en daarom wordt het genegeerd.

Deze animatie illustreert hoe de uitgang reageert op de veranderende ingangs- en kloksignalen:

De verticale lijnen geven aan hoe het ingangssignaal zich verhoudt tot de stijgende flanken van de klok.

Besteed speciale aandacht aan de ene positieve puls op het ingangssignaal vanaf 20 ns. Het is synchroon met de klok en precies één klokperiode lang. De uitgang reageert niet onmiddellijk, maar wordt met één klokperiode vertraagd.

Toen ik VHDL leerde, vond ik dit bijzonder moeilijk te begrijpen. De stijgende flank van de klok loopt synchroon met de stijgende flank van de ingang, dus hoe kan de flip-flop de ene of de andere waarde kiezen?

De simulator gebruikt tijdstappen om gebeurtenissen op een voorspelbare manier te modelleren, en signalen verspreiden zich in nultijd. Omdat de flip-flop de invoer in exact dezelfde tijdstap leest als de uitvoer, ziet hij de oude waarde van de invoer en kopieert deze naar de uitvoer.

Lees hier meer over VHDL-tijdstappen:Delta-cycli uitgelegd

Ik moet aan dit antwoord toevoegen dat dit niet echt . is hoe het werkt. In de fysieke wereld heeft een signaal tijd nodig om zich voort te planten, we weten niet precies wanneer het op de flip-flop aankomt. Deze propagatievertragingen worden voor ons automatisch ingeschat door het softwareproces (plaats en route) dat de VHDL-code omzet in een netlijst.

In werkelijkheid moet de ingang enkele nanoseconden stabiel worden gehouden voor en na de stijgende klokflank:

Deze kritieke tijdsperioden staan bekend als instel- en houdtijd. Gelukkig hoef je hier normaal gesproken geen rekening mee te houden. Als je puur met geklokte logica werkt, worden deze problemen opgelost door de software die de VHDL-code in een netlijst verandert.

Afhaalmaaltijden

- Geklokte processen met gesynchroniseerde reset hebben alleen het kloksignaal op de gevoeligheidslijst

- De

if rising_edge(Clk)zorgt ervoor dat het proces alleen ontwaakt op stijgende flanken van de klok - In een synchroon ontwerp gebeuren er alleen dingen op de actieve klokrand

Doe de Basic VHDL Quiz – deel 3 »

of

Ga naar de volgende tutorial »

VHDL

- Een lijst met strings maken in VHDL

- Hoe maak je een Tcl-gestuurde testbench voor een VHDL-codeslotmodule?

- Simulatie stoppen in een VHDL-testbench

- Een PWM-controller maken in VHDL

- Hoe willekeurige getallen te genereren in VHDL

- Hoe maak je een ringbuffer FIFO in VHDL

- Hoe maak je een zelfcontrolerende testbank aan

- Een gekoppelde lijst maken in VHDL

- Een procedure gebruiken in een proces in VHDL

- Een onzuivere functie gebruiken in VHDL

- Een functie gebruiken in VHDL