Hoe Port Map-instantiatie te gebruiken in VHDL

Een module is een op zichzelf staande eenheid van VHDL-code. Modules communiceren met de buitenwereld via de entiteit . Havenkaart is het deel van de module-instantiatie waar u aangeeft op welke lokale signalen de in- en uitgangen van de module moeten worden aangesloten.

In eerdere tutorials in deze serie hebben we al onze code in het hoofd VHDL-bestand geschreven, maar normaal gesproken zouden we dat niet doen. We creëren logica met het doel deze te gebruiken in een FPGA- of ASIC-ontwerp, niet voor de simulator.

Een VHDL-module die is gemaakt om in een simulator te draaien, heeft meestal geen ingangs- of uitgangssignalen. Het staat geheel op zichzelf. Daarom is de entiteit van onze ontwerpen leeg geweest. Er is niets tussen de entity tag en de end entity; tag.

Deze blogpost maakt deel uit van de serie Basic VHDL Tutorials.

Een module zonder ingangs- of uitgangssignalen kan niet in een echt ontwerp worden gebruikt. Het enige doel is om ons in staat te stellen VHDL-code in een simulator uit te voeren. Daarom wordt het een testbank genoemd . Om een module met ingangs- en uitgangssignalen te simuleren, moeten we instantiëren het in een testbank.

Modules en testbanken komen vaak in paren voor en worden in verschillende bestanden opgeslagen. Een veelgebruikt naamgevingsschema is om de testbench de modulenaam te noemen met "Tb" toegevoegd, en om de architectuur "sim" te noemen. Als de module “MyModule” heet, zal de testbench “MyModuleTb” heten. Bijgevolg worden de bestandsnamen "MyModuleTb.vhd" en "MyModule.vhd".

Met behulp van de testbench-code kunnen we verifiëren dat de module correct werkt in een simulatieomgeving. De module die wordt getest, wordt gewoonlijk het apparaat dat wordt getest . genoemd (DUT).

Modules kunnen ook binnen andere modules worden geïnstantieerd. Door de code in modules te partitioneren, kan deze meerdere keren worden geïnstantieerd. U kunt meerdere exemplaren van een module binnen hetzelfde ontwerp maken en deze kan in veel ontwerpen opnieuw worden gebruikt.

De syntaxis voor een entiteit met een poort in VHDL is:entity <entity_name> is

port(

<entity_signal_name> : in|out|inout <signal_type>;

...

);

end entity;

De syntaxis voor het instantiëren van een dergelijke module in een ander VHDL-bestand is:<label> : entity <library_name>.<entity_name>(<architecture_name>) port map(

<entity_signal_name> => <local_signal_name>,

...

);

De <label> kan elke naam zijn, en het zal verschijnen in het hiërarchievenster in ModelSim. De <library_name> voor een module is ingesteld in de simulator, niet in de VHDL-code. Standaard is elke module gecompileerd in de work bibliotheek. De <entity_name> en <architecture_name> moet overeenkomen met de module waarvan we een instantie maken. Ten slotte moet elk van de entiteitssignalen worden toegewezen aan een lokale signaalnaam.

Er zijn andere manieren om een module in VHDL te instantiëren, maar dit is de basissyntaxis voor expliciete instantiëring.

Oefening

In deze video-tutorial leren we hoe we een module in VHDL kunnen maken en instantiëren:

De definitieve code voor de MUX testbench :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_PortMapTb is

end entity;

architecture sim of T15_PortMapTb is

signal Sig1 : unsigned(7 downto 0) := x"AA";

signal Sig2 : unsigned(7 downto 0) := x"BB";

signal Sig3 : unsigned(7 downto 0) := x"CC";

signal Sig4 : unsigned(7 downto 0) := x"DD";

signal Sel : unsigned(1 downto 0) := (others => '0');

signal Output : unsigned(7 downto 0);

begin

-- An instance of T15_Mux with architecture rtl

i_Mux1 : entity work.T15_Mux(rtl) port map(

Sel => Sel,

Sig1 => Sig1,

Sig2 => Sig2,

Sig3 => Sig3,

Sig4 => Sig4,

Output => Output);

-- Testbench process

process is

begin

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= Sel + 1;

wait for 10 ns;

Sel <= "UU";

wait;

end process;

end architecture;

De definitieve code voor de MUX module :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T15_Mux is

port(

-- Inputs

Sig1 : in unsigned(7 downto 0);

Sig2 : in unsigned(7 downto 0);

Sig3 : in unsigned(7 downto 0);

Sig4 : in unsigned(7 downto 0);

Sel : in unsigned(1 downto 0);

-- Outputs

Output : out unsigned(7 downto 0));

end entity;

architecture rtl of T15_Mux is

begin

process(Sel, Sig1, Sig2, Sig3, Sig4) is

begin

case Sel is

when "00" =>

Output <= Sig1;

when "01" =>

Output <= Sig2;

when "10" =>

Output <= Sig3;

when "11" =>

Output <= Sig4;

when others => -- 'U', 'X', '-', etc.

Output <= (others => 'X');

end case;

end process;

end architecture;

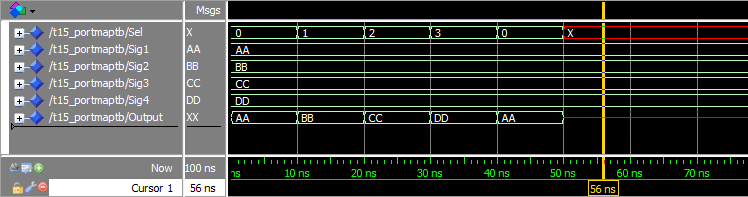

Het golfvormvenster in ModelSim nadat we op run hebben gedrukt en ingezoomd op de tijdlijn:

Analyse

Zoals we aan de golfvorm kunnen zien, werkt de multiplexer (MUX) module zoals verwacht. De golfvorm is identiek aan die van de vorige tutorial die we hebben gemaakt zonder modules te gebruiken.

Nu is er een duidelijke scheiding tussen de ontwerpmodule en de testbank. De module die de MUX bevat, is wat we in een ontwerp willen gebruiken, en het enige doel van de testbank is om ons in staat te stellen deze in een simulator te draaien. Er is een proces in de testbench dat gebruikmaakt van wait verklaringen voor het creëren van kunstmatige vertragingen in de simulatie. De ontwerpmodule heeft geen notie van tijd, hij reageert alleen op externe prikkels.

We noemden de architectuur van de testbench sim , voor simulatie. De architectuur van de ontwerpmodule heette rtl , wat staat voor register-overdrachtsniveau. Dit zijn slechts naamgevingsconventies. Als je een bestand met zo'n naam ziet, weet je meteen of het een testbench of een ontwerpmodule is. Verschillende bedrijven kunnen verschillende naamgevingsconventies hebben.

Afhaalmaaltijden

- Ingangs- en uitgangssignalen worden gespecificeerd in de entiteit van een module

- Een module zonder in/uit-signalen heet een testbench , en het kan alleen in een simulator worden gebruikt

- Een module met in/uit-signalen kan meestal niet direct in een simulator worden uitgevoerd

Ga naar de volgende tutorial »

VHDL

- Hoe gebruiken we molybdeen?

- Een lijst met strings maken in VHDL

- Hoe maak je een Tcl-gestuurde testbench voor een VHDL-codeslotmodule?

- Simulatie stoppen in een VHDL-testbench

- Een PWM-controller maken in VHDL

- Hoe willekeurige getallen te genereren in VHDL

- Een procedure gebruiken in een proces in VHDL

- Een onzuivere functie gebruiken in VHDL

- Een functie gebruiken in VHDL

- Een eindige-toestandsmachine maken in VHDL

- Hoe een snijmolen te gebruiken