Ik ergerde me een beetje aan de eigenaardigheden van de AXI-interface toen ik voor het eerst logica moest maken om een AXI-module te koppelen. In plaats van de reguliere bezet/geldig, vol/geldig of leeg/geldig stuursignalen, gebruikt de AXI-interface twee stuursignalen genaamd gereed en geldig. Mi

Een handige manier om blok-RAM met beginwaarden te vullen, is door binaire of hexadecimale letterlijke waarden uit een ASCII-bestand te lezen. Dit is ook een goede manier om een ROM (read-only memory) in VHDL te maken. RAM en ROM zijn immers hetzelfde in FPGAs, ROM is een RAM waarvan je alleen lee

Het lezen van signaalwaarden uit een bestand is een alternatieve manier om stimuli te genereren voor het apparaat dat wordt getest (DUT). De volgorde en timing van de testbank zijn hard gecodeerd in een stimulusbestand dat regel voor regel door de VHDL-testbank wordt gelezen. Hierdoor kunt u eenvoud

Het converteren van het afbeeldingsbestand naar een bitmap-indeling zorgt voor de gemakkelijkste manier om een afbeelding te lezen met VHDL. Ondersteuning voor het BMP-rasterafbeeldingsbestandsformaat is ingebouwd in het Microsoft Windows-besturingssysteem. Dat maakt BMP een geschikt beeldformaat

Deze video is een inleidende presentatie over FPGA en programmeerbare logica-technologie. Ik hield deze lezing van 45 minuten op een evenement georganiseerd door 7 Peaks Software in Bangkok, Thailand, op 19 november 2019. Hoogtepunten uit de presentatie zijn: 05:07 Wie gebruikt FPGAs? 09:06 Wat i

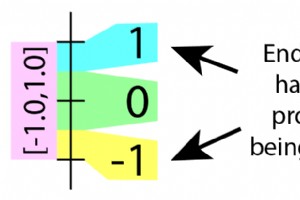

VHDL heeft een ingebouwde pseudo-willekeurige generator, maar deze kan alleen drijvende-kommagetallen tussen 0 en 1 genereren. Gelukkig kunt u hieruit elk ander willekeurig gegevensformaat afleiden dat u nodig heeft. Lees dit artikel verder om erachter te komen hoe u real . kunt maken of integer waa

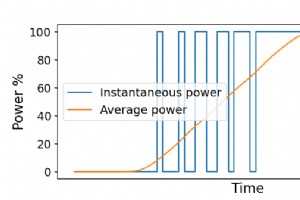

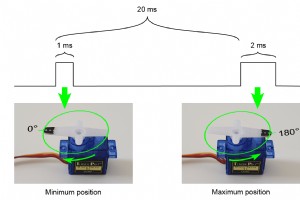

Pulsbreedtemodulatie (PWM) is een efficiënte manier om analoge elektronica te besturen vanaf puur digitale FPGA-pinnen. In plaats van te proberen de analoge spanning te regelen, schakelt PWM snel de voedingsstroom op vol vermogen naar het analoge apparaat in en uit. Deze methode geeft ons nauwkeurig

Ik heb gemerkt dat veel van de gadgets die ik de afgelopen jaren heb gekocht, zijn verschoven van LED-knippering naar led-ademhaling. De meeste elektronische gadgets bevatten een status-LED waarvan het gedrag indicaties geeft van wat er in het apparaat gebeurt. Op mijn elektrische tandenborstel kni

Hoe stop je de VHDL-simulator als de simulatie is voltooid? Er zijn verschillende manieren om dat te doen. In dit artikel zullen we de meest voorkomende manieren onderzoeken om een succesvolle testbench-run te beëindigen. De hier gepresenteerde VHDL-code is universeel en zou in elke geschikte VHD

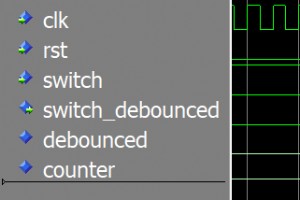

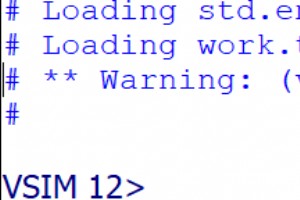

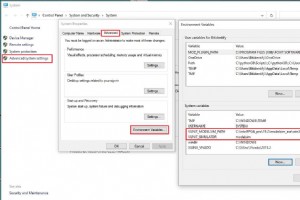

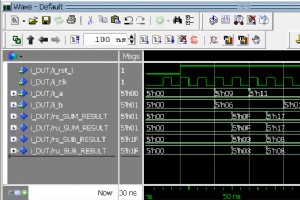

De meeste VHDL-simulators gebruiken de Tool Command Language (Tcl) als hun scripttaal. Wanneer u een opdracht typt in de console van de simulator, gebruikt u Tcl. Bovendien kunt u met Tcl scripts maken die in de simulator worden uitgevoerd en met uw VHDL-code communiceren. In dit artikel zullen we

Radiogestuurde (RC) modelservos zijn kleine actuatoren die doorgaans worden gebruikt in vliegtuigjes, autos en boten voor hobbyisten. Ze stellen de machinist in staat het voertuig op afstand te besturen via een radioverbinding. Omdat RC-modellen al heel lang bestaan, is de de-facto standaardinterfac

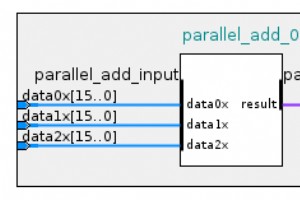

De Genereer-instructie in VHDL kan automatisch een codeblok dupliceren naar sluitingen met identieke signalen, processen en instanties. Het is een for-lus voor de architectuurregio die geketende processen of module-instanties kan maken. In tegenstelling tot een reguliere for-lus, die alleen in ee

Tekstreeksen in VHDL zijn over het algemeen beperkt tot tekenreeksen met een vaste lengte. Dat is logisch omdat VHDL hardware beschrijft, en strings van generieke lengte vereisen dynamisch geheugen. Om een reeks tekenreeksen te definiëren, moet u tijdens het compileren ruimte toewijzen voor het h

Deze tutorial behandelt het gebruik van de Integrated Logic Analyzer (ILA) en Virtuele invoer/uitvoer (VIO) cores voor het debuggen en bewaken van uw VHDL-ontwerp in de Xilinx Vivado IDE. In veel gevallen moeten ontwerpers verificatie op de chip uitvoeren. Dat wil zeggen, toegang krijgen tot het ge

Bij het ontwerpen van VHDL voor veiligheidskritieke FPGA-toepassingen, is het niet voldoende om testbench te schrijven naar beste vermogen. Je moet bewijzen dat de module werkt zoals bedoeld en zonder ongewenste neveneffecten. Formele verificatietechnieken kunnen u helpen een vereiste aan een test

VUnit is een van de meest populaire open-source VHDL-verificatieframeworks die vandaag beschikbaar zijn. Het combineert een Python-testsuite-runner met een speciale VHDL-bibliotheek om uw testbanken te automatiseren. Om u deze gratis VUnit-zelfstudie te geven, schakelt VHDLwhiz Ahmadmunthar Zaklo

Heb je ooit een VHDL-simulatie willen uitvoeren met een Quartus IP-kern via het VUnit-verificatieraamwerk? Dat was wat FPGA-ingenieur Konstantinos Paraskevopoulos in gedachten had, maar hij kon er geen geschikte tutorial voor vinden. Gelukkig gebruikte hij zijn talent om erachter te komen hoe en wa

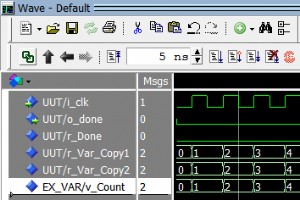

Variabelen in VHDL werken op dezelfde manier als variabelen in C. Hun waarde is geldig op de exacte locatie in de code waar de variabele is gewijzigd. Daarom, als een signaal de waarde van de variabele voor . gebruikt de toewijzing, zal deze de oude variabele waarde hebben. Als een signaal de waarde

Alle digitale ontwerpers moeten begrijpen hoe wiskunde werkt in een FPGA of ASIC. De eerste stap daarvoor is begrijpen hoe ondertekende en niet-ondertekende signaaltypen werken. Ondertekende en niet-ondertekende typen bestaan in de numeric_std pakket, dat deel uitmaakt van de ieee-bibliotheek. Opg

De Record-constructie in VHDL kan worden gebruikt om uw code te vereenvoudigen. Records zijn vergelijkbaar met structuren in C . Records worden meestal gebruikt om een nieuw VHDL-type te definiëren. Dit nieuwe type bevat elke groep signalen die de gebruiker wenst. Meestal wordt dit gebruikt om int

VHDL

Top ideeënlijst voor elektrische miniprojecten

Hoe een signaal verschilt van een variabele in VHDL

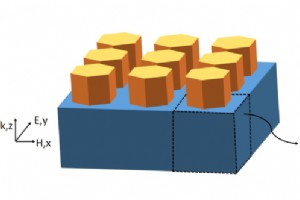

De atoomherschikking van op GaN gebaseerde meerdere kwantumbronnen in H2/NH3 gemengd gas voor het verbeteren van structurele en optische eigenschappen

Egyptische klanten verwelkomen in onze fabriek:ervaar de 2060 ATC CNC-router