Simulatie stoppen in een VHDL-testbench

Hoe stop je de VHDL-simulator als de simulatie is voltooid? Er zijn verschillende manieren om dat te doen. In dit artikel zullen we de meest voorkomende manieren onderzoeken om een succesvolle testbench-run te beëindigen.

De hier gepresenteerde VHDL-code is universeel en zou in elke geschikte VHDL-simulator moeten werken. Voor de methoden waarbij Tcl betrokken is, zal ik de opdrachten voor de ModelSim- en Vivado-simulators opsommen.

Je kunt een voorbeeldproject downloaden met de vier verschillende testbanken uit dit artikel als je ModelSim hebt geïnstalleerd. Voer uw e-mailadres in het onderstaande formulier in om het zip-bestand te ontvangen!

Gebruik afwerking procedure

De VHDL finish procedure is mijn favoriete manier om een VHDL-testbank te stoppen die zonder fouten wordt voltooid. Je moet "finish" importeren uit het STD.ENV-pakket en je moet de testbench compileren in VHDL-2008 of nieuwer om het te gebruiken.

De onderstaande code beëindigt de simulatie wanneer we de laatste regel van het testbench-sequencerproces bereiken.

use std.env.finish; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'finish'"; finish; end process;

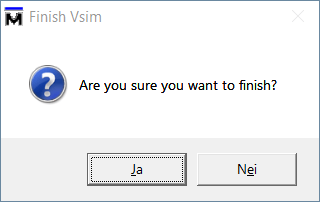

Merk op dat voltooien sluit de simulatie standaard af. Als u ModelSim in de GUI-versie gebruikt, verschijnt er een pop-up met de tekst "Weet u zeker dat u wilt voltooien?". Als u op Ja klikt, wordt ModelSim afgesloten.

Dat is waarschijnlijk niet wat je wilt. Gelukkig kunnen we dit gedrag voorkomen door de optie "-onfinish stop" toe te voegen aan de vsim-opdracht, zoals hieronder wordt weergegeven. Door dit te doen, wordt de afwerking procedure zal zich op dezelfde manier gedragen als de stop procedure die we in het volgende gedeelte van dit artikel zullen bespreken.

vsim -onfinish stop work.using_finish_tb

Een voordeel van het gebruik van finish is dat u het standaardgedrag kunt gebruiken bij simulatie in batchmodus. Als u scripts gebruikt om de simulatie te starten, wilt u de controle teruggeven aan het aanroepende script nadat de simulatie is voltooid.

Het onderstaande voorbeeld toont een testbank met de afwerking procedure gestart in ModelSim batch-modus in Linux. Nadat de testbench is voltooid, wordt de simulator afgesloten en bij de laatste regel zijn we terug in de Linux-shell.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_finish_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_finish_tb # vsim work.using_finish_tb # Start time: 22:58:31 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_finish_tb(sim) # run -all # ** Note: Calling 'finish' # Time: 1 ms Iteration: 0 Instance: /using_finish_tb # End time: 22:58:31 on Jun 21,2020, Elapsed time: 0:00:00 # Errors: 0, Warnings: 8 jonas@ubuntu:~/stop_tb$

De VHDL finish procedure is gedefinieerd in het standaard ENV-pakket. Zoals we aan de onderstaande code kunnen zien, komt deze in twee overbelaste smaken. Er is de versie zonder parameters, die ik altijd gebruik, en er is een andere die een status-integer als constante invoer neemt.

procedure FINISH (STATUS: INTEGER); procedure FINISH;

Je zou denken dat de status integer de exit-code wordt wanneer deze wordt aangeroepen vanuit een Linux-shell, maar dat is niet het geval, althans niet met ModelSim. Het probleem met het gebruik van deze statuscode is dat wat het doet afhangt van de simulator. De formulering in de VHDL-2008-standaard is:"de waarde van de STATUS-parameter kan worden gebruikt op een implementatie die is gedefinieerd door de hostsimulator ".

U kunt echter de waarde van de Linux-exitcode in ModelSim bepalen met behulp van het Tcl-commando exit -code <value> , maar dat is een ander verhaal.

De stop gebruiken procedure

De VHDL stop procedure zorgt ervoor dat de simulatie pauzeert. Dat kan handig zijn als u de signaalwaarden handmatig wilt onderzoeken of zelfs later wilt doorgaan met de simulatie. De simulator behandelt het als een breekpunt.

Het onderstaande voorbeeld laat zien hoe u de stop . importeert en gebruikt procedure.

use std.env.stop; ... SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; report "Calling 'stop'"; stop; end process;

Een probleem met het gebruik van stop in op scripts gebaseerde instellingen is dat het de simulatie niet afsluit. In plaats van controle terug te geven aan de beller, opent ModelSim een Tcl-opdrachtshell, waardoor het aanroepende script voor onbepaalde tijd blijft hangen.

De onderstaande lijst toont de uitvoer van het uitvoeren van de testbench die gebruikmaakt van de stop procedure in batchmodus. Nadat de simulatie stopt, zijn we nog steeds in ModelSim. Om uit de Tcl-shell te komen, zouden we "exit" moeten typen.

jonas@ubuntu:~/stop_tb$ vsim -c -do 'vsim work.using_stop_tb; run -all' Reading pref.tcl # 10.5b # vsim work.using_stop_tb # vsim work.using_stop_tb # Start time: 22:58:56 on Jun 21,2020 # Loading std.standard # Loading std.env(body) # Loading work.using_stop_tb(sim) # run -all # ** Note: Calling 'stop' # Time: 1 ms Iteration: 0 Instance: /using_stop_tb # Break in Process SEQUENCER_PROC at ~/stop_tb/src/using_stop_tb.vhd line 23 # Stopped at ~/stop_tb/src/using_stop_tb.vhd line 23 VSIM 3>

Net als de afwerking procedure, stop vereist VHDL-2008 of nieuwer. Zoals hieronder wordt weergegeven, bestaat er een overbelaste versie van de procedure. Er is een integer-statuswaarde nodig, maar het gedrag verschilt per simulator.

procedure STOP (STATUS: INTEGER); procedure STOP;

De bewering gebruiken zoekwoord

Een faalveilige en universele manier om een VHDL-testbench te stoppen, is door een beweringfout te creëren. Dat was de eerste manier waarop iemand me leerde om de simulatie te beëindigen toen ik VHDL leerde op de universiteit.

Er zijn geen extra importen nodig en het werkt in alle VHDL-versies. Zorg ervoor dat u het ernstniveau mislukking gebruikt , zoals weergegeven in het onderstaande voorbeeld.

SEQUENCER_PROC : process begin -- Replace this line with your testbench logic wait until stop_condition; assert false report "Test: OK" severity failure; end process;

En waarom haat ik deze manier om een succesvolle simulatie te stoppen?

Allereerst ziet het er vreemd en verwarrend uit om de afdruk van het bovenstaande voorbeeld te zien:

# ** Failure: Test: OK

Er staat dat het een "mislukking" is, maar de test is tegelijkertijd "OK". Dat komt omdat de beweren statement wordt verondersteld een foutconditie aan te geven en niet de succesvolle voltooiing van de simulatie.

Het andere vervelende probleem dat ik kan bedenken, is dat het moeilijk wordt om programmatisch te achterhalen of de simulatie succesvol was.

De meeste VHDL-professionals starten de simulaties op een bepaald moment vanuit een script, bijvoorbeeld als onderdeel van een groter regressietestschema. Als de testbench ook stopt bij een assertion failure terwijl er niets aan de hand is, kunnen we dat niet gebruiken als een marker om de gezondheid van de VHDL-module te bepalen.

Tcl gebruiken

De laatste methode om de simulatie te stoppen die ik ga behandelen, is om Tcl te gebruiken in combinatie met VHDL. In plaats van de testbench uit het VHDL-bestand te stoppen, stellen we een normaal VHDL-signaal in wanneer het tijd is om te stoppen. En vooraf configureren we de simulator om te luisteren naar een verandering op dit triggersignaal.

Lees ook:

Waarom je Tcl moet leren

Kijk naar het onderstaande voorbeeld, dat een signaal instelt met de naam stop_condition wanneer alle testgevallen zijn voltooid.

signal stop_condition : boolean;

begin

-- Replace this line with your DUT instantiation

stop_condition <= not stop_condition after 1 ms;

SEQUENCER_PROC : process

begin

-- Put your testbench logic here

-- Pause this process forever after all tests are done

wait;

end process;

U kunt elk testbench-proces dat zijn werk heeft gedaan in de slaapstand zetten met een enkele wacht statement voor het eindproces label. Dat voorkomt dat het opnieuw wordt opgestart. De Tcl-code voor het daadwerkelijk stoppen van de simulatie verschilt per simulator.

In ModelSim

Wat we willen is om de testbank te stoppen wanneer de stop_condition VHDL-signaal wordt waar . We kunnen dat doen door een callback in Tcl in te stellen voordat we de VHDL-testbench uitvoeren.

Volgens de ModelSim Command Reference Manual kunnen we dat bereiken door de Tcl when . te gebruiken opdracht. In de onderstaande Tcl-code registreren we zo'n callback, en dan starten we de simulator met run -all .

when {stop_condition} {

stop

echo "Test: OK"

}

run -all

Houd er rekening mee dat de code tussen de accolades niet wordt uitgevoerd totdat de callback plaatsvindt. Wanneer de VHDL-code de stop_condition changes verandert signaal naar true , zal de simulator pauzeren en de twee regels uitvoeren. In het voorbeeld stoppen we de simulatie en printen "Test:OK" naar de console. U kunt ook een Tcl exit hebben commando erin, dat de simulator zou afsluiten, net als de VHDL finish procedure.

# vsim # Start time: 22:31:11 on Jun 22,2020 # Loading std.standard # Loading work.using_tcl_tb(sim) # Test: OK # Simulation stop requested.

De bovenstaande lijst toont de uitvoer die naar de ModelSim-console is afgedrukt wanneer de Tcl / VHDL-testbench is voltooid. Als je het op je computer wilt proberen, gebruik dan het onderstaande formulier om het ModelSim-project met alle voorbeelden uit dit artikel te downloaden!

In Vivado

Volgens de Vivado Design Suite Tcl Command Reference Guide kunnen we een Tcl-callback registreren met de add_condition opdracht. De onderstaande code toont het Xilinx-equivalent voor de eerder besproken ModelSim-versie.

set sim_fileset sim_1

launch_simulation -simset [get_filesets $sim_fileset]

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

run all

De -notrace switch voorkomt dat de coderegels in de callback-functie naar de terminal worden herhaald terwijl ze worden uitgevoerd. Ik heb liever geen extra rommel in de console.

De onderstaande lijst toont een fragment uit de simulatie die wordt uitgevoerd in de Vivado-simulatorconsole.

launch_simulation: ...

add_condition -notrace stop_condition {

stop

puts "Test: OK"

}

condition8

run all

Test: OK

Laatste gedachten

Zoals je hebt gezien, zijn er veel manieren om een VHDL-simulatie te beëindigen. Echter, de enige die ik ooit gebruik is de VHDL-2008 afwerking procedure.

Alle simulatoren ondersteunen inmiddels VHDL-2008 en je hoeft de RTL-code in 2008 niet te compileren, alleen de testbench. De afwerking procedure is de meest draagbare methode en stelt u in staat de simulator te stoppen wanneer deze in de GUI-modus wordt uitgevoerd, of te stoppen wanneer deze in batchmodus wordt uitgevoerd. Precies het gedrag dat ik meestal wil.

Maar er zijn voordelen aan de Tcl-methoden die buiten het bestek van dit artikel vallen. Wanneer u de simulator in de Tcl-callback hebt gepauzeerd, kunt u veel meer doen dan alleen de simulator stoppen en afsluiten. U kunt VHDL-signalen onderzoeken en zelfs manipuleren met Tcl, terwijl u aan het terugbellen bent. Dat is verificatie met Tcl.

VHDL

- Een lijst met strings maken in VHDL

- Hoe maak je een Tcl-gestuurde testbench voor een VHDL-codeslotmodule?

- Een PWM-controller maken in VHDL

- Hoe willekeurige getallen te genereren in VHDL

- Interactieve testbank met Tcl

- Hoe maak je een zelfcontrolerende testbank aan

- Een gekoppelde lijst maken in VHDL

- Een procedure gebruiken in een proces in VHDL

- Een onzuivere functie gebruiken in VHDL

- Een functie gebruiken in VHDL

- Hoe u roest kunt stoppen