Wat is VHDL?

Kortom, VHDL is een computertaal die wordt gebruikt voor het ontwerpen van digitale schakelingen.

Ik gebruik de term "computertaal" om VHDL te onderscheiden van andere, meer gebruikelijke programmeertalen zoals Java of C++. Maar is VHDL een programmeertaal? Jazeker. Het is een programmeertaal die nutteloos is als het gaat om het maken van computerprogramma's!

VHDL is een gebeurtenisgestuurde, parallelle programmeertaal. Hoewel het niet geschikt is voor het maken van programma's die door een CPU op een computer kunnen worden uitgevoerd, is het geweldig voor het maken van de eigenlijke CPU. Het is een hardwarebeschrijvingstaal, wat betekent dat het kan worden gebruikt voor het ontwerpen van digitale logica.

Ga hier naar de serie Basic VHDL Tutorials!

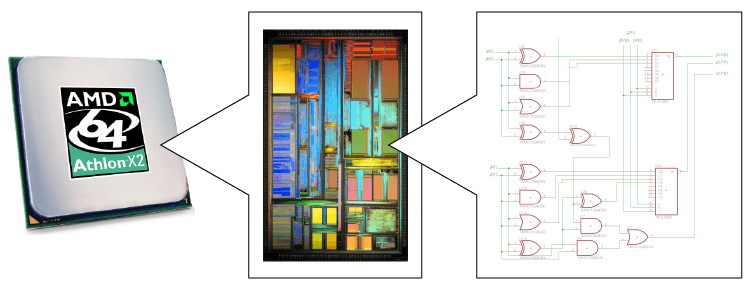

Beschouw de bovenstaande illustratie. Binnen de CPU-chip zijn er heel veel, voornamelijk digitale elektronische circuits (midden). Deze digitale schakelingen kunnen worden weergegeven aan de hand van een schematisch diagram (rechts). Bij het maken van een geïntegreerde circuitchip, zoals de CPU, moeten we beginnen met het maken van het logische schakelschema aan de rechterkant.

Het is een redelijke aanname dat dergelijke schakelschema's worden gemaakt in een soort schematische editor, maar dit is niet hoe het is gedaan. De circuits worden beschreven in een tekstuele taal zoals VHDL.

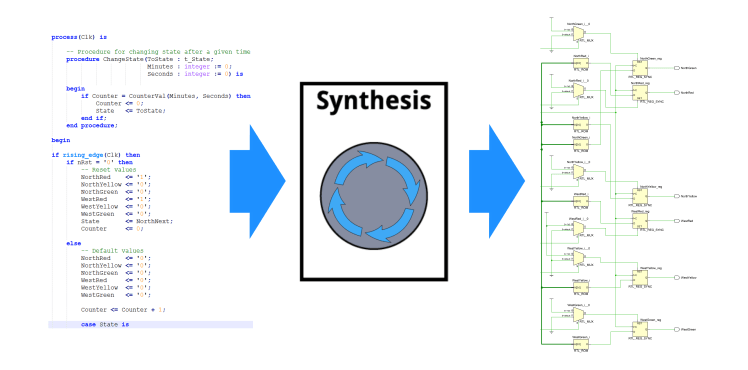

Synthese

In plaats van de exacte schakelingen in een schematische editor te tekenen, gebruiken we VHDL om het gewenste gedrag van de schakeling te beschrijven. De VHDL-code kan vervolgens worden omgezet in een exact schema in een proces dat synthese wordt genoemd . De synthesetool is een softwaretoepassing die de VHDL-code gebruikt en een mogelijke oplossing probeert te vinden voor het gedrag dat u hebt beschreven.

Als dit lukt, zal de output van de synthesizer een netlijst zijn die op zijn beurt kan worden bekeken in een schematische editor.

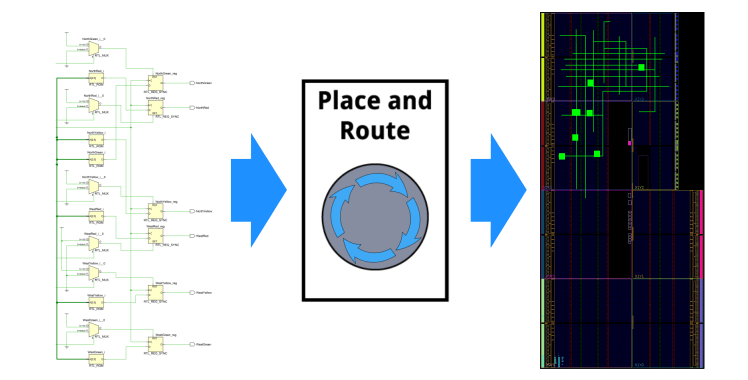

Plaats en route

Hoewel de netlijst een exacte logische beschrijving van het circuit geeft, zegt het niets over de fysieke implementatie. Om een nauwkeurige beschrijving van de fysieke lay-out af te leiden, wordt de netlijst door een proces geleid genaamd plaats en route , of afgekort PAR. De router zal proberen de elementen van de netlijst toe te wijzen aan fysieke componenten op het doelapparaat. Het moet ook draden tussen alle componenten leiden. Het is een gigantische puzzel die de router moet oplossen!

Als dit lukt, zal de uitvoer van PAR een ander soort netlijst zijn. Deze netlijst bevat informatie over plaatsing en routering en is specifiek voor het type doelapparaat. Als het doelapparaat een FPGA is, kan de gerouteerde netlijst worden omgezet in een programmeerbestand. Als het doelapparaat een ASIC is, wordt het iets ingewikkelder.

Dus, wat is VHDL?

Het is een soort programmeertaal die wordt gebruikt voor het maken van digitale logica voor geïntegreerde schakelingen.

Volg hier de basis-VHDL-tutorials>>

VHDL