Materiële innovatiesleutel tot 7nm en verder

Terwijl ons halfgeleideronderzoeksteam in Albany, NY CMOS-technologie blijft schalen naar toekomstige knooppunten - tot 10nm, 7nm en verder - blijft de weerstand van het transistorkanaal die de stroomstroom bepaalt en hoe we ermee verbinden, een steeds grotere rol spelen in de algehele prestaties van een chip. Dus om het concurrentievermogen van de prestaties van een bepaalde toekomstige halfgeleidertechnologie te waarborgen, is kanaalmateriaalinnovatie om de weerstand van transistorkanalen te verminderen een cruciaal studiegebied. Daarom onderzoeken we siliciumgermanium (SiGe) - elementen die nodig zijn om de voordelen op het gebied van stroomprestaties te bereiken die werden beschreven in de aankondiging van de 7nm-chip van vorig jaar.

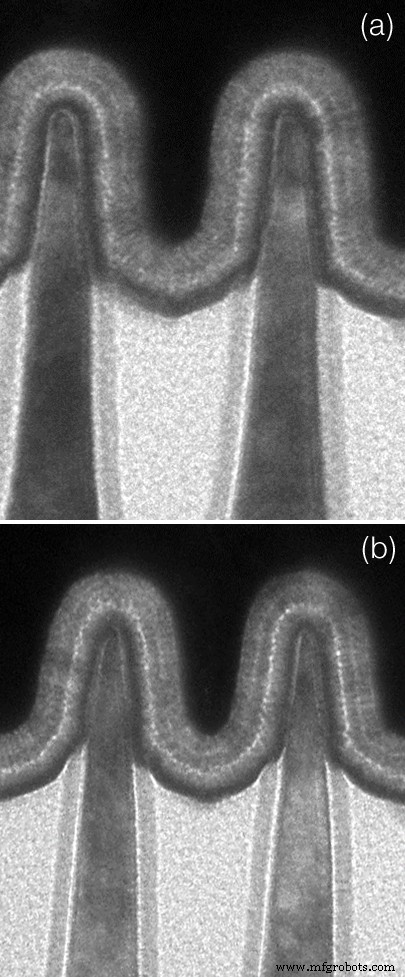

Symmetrisch Si FinFET (a) en SiGe FinFET (b) profielen op 10nm gemaakt door IBM Research bij SUNY Polytechnic's NanoTech Complex in Albany, NY. Dit illustreert dat SiGe Fin superieure elektrische eigenschappen kan bieden dan Si Fin.

De huidige 14nm node FinFET*-chips gebruiken alleen siliciumkanalen (silicium is niet stabiel buiten deze schaal). Als alternatief heeft SiGe-gebaseerde FinFET-technologie prestatieverbetering aangetoond met 10nm-technologiebasisregels (industrienormen), wat elegante oplossingen biedt voor een levensvatbare CMOS-technologieoptie. Een van die elegante SiGe FinFET-oplossingen is het toestaan van apparaten met een laag vermogen en hoge prestaties op dezelfde chip - zonder prestatie of variabiliteit op het ene type apparaat ten opzichte van het andere te verliezen.

De SiGe FinFET-technologie biedt ook superieure elektrische betrouwbaarheid in vergelijking met Si FinFET. En dit leidt tot een verbeterde prestatiestabiliteit op chipniveau dan Si FinFET gedurende de levensduur van de chip. Dit betekent dat de identieke procesintegratiestroom geschikt is voor zowel supercomputerontwerpen als mobiele ontwerpen.

SiGe verlegt de grenzen van chipscaling door de manier te veranderen waarop stroom door het kanaal van een transistor gaat. Het blijkt dat door grotere germaniumatomen toe te voegen aan een kristal gemaakt van kleinere siliciumatomen, het kristal een roostermismatch ontwikkelt, waardoor spanning in het transistorkanaal ontstaat. Deze spanning maakt het mogelijk om bij lagere spanningen meer stroom door het kanaal te verplaatsen. Dus door SiGe als kanaalmateriaal te gebruiken, kunnen we een routekaart naar kleinere dimensies in kaart brengen met behoud van een balans tussen kracht en prestaties.

SiGe voor de toekomstige nodes:de uitdagingen van het produceren van 10nm- en 7nm-chips oplossen

Retentie van spanning gedurende de gehele integratiestroom, samen met defectcontrole, zijn twee van de grootste technische uitdagingen voor het produceren van SiGe FinFET op 10nm-knooppunten en lager. Transistorkanalen zouden spanning kunnen verliezen tijdens de thermische gloeiprocessen die doteermiddelen activeren en de integriteit van de transistor stabiliseren; of tijdens de bron-/afvoeruitsparingsprocessen die de uniforme overgang vormen van de bovenkant van de vin naar de onderkant van de vin; of zelfs de vinpatronen in specifieke ontwerpen waarvoor vinnen met een korte lengte nodig zijn.

Defectcontrole is ook van cruciaal belang bij de massaproductie van een CMOS-technologie. Met de roostermismatch tussen een SiGe-kanaal en het siliciumwafelsubstraat, is het een uitdaging om het vereiste fabricagefoutniveau over de hele wafer te handhaven. Maar met ons geavanceerde epitaxiale (kristal)groeibeheer, innovatieve Fin-module-procesintegratie en source/drain-engineering hebben we oplossingen ontwikkeld om de spanning in het kanaal tijdens de gehele integratiestroom te garanderen, terwijl we ook een lage defectiviteit behouden in onze 10nm- en 7nm-test knooppunten.

Met deze uitgebreide SiGe FinFET-technologie haalbaarheidsstudie op 10nm technologie grondregels, werken we nu samen met chipontwerpers en chipmakers om SiGe FinFET-technologie massaal te produceren. Ik verwacht dat onze SiGe FinFET-technologie de silicium FinFET zal vervangen in de volgende generatie CMOS-technologieknooppunten voor computergebruik, van supercomputers tot mobiele apparaten. Ze kunnen ook worden gebruikt in 'meer dan Moore'-toepassingen in de cloud en cognitieve computing, waar een lage stroomvoorziening en een laag stroomverbruik zeer wenselijk zijn, zoals toepassingen in de cloud en cognitieve computing.

Verder lezen

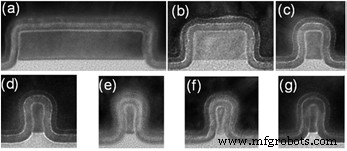

Dwarsdoorsneden van Fin en gate-stack voor Fin-breedte variërend van 87 nm (a) tot 3 nm (g) voor hogere Ge-inhoud voor SiGe Fin.

Op het IEEE-symposium van dit jaar over VLSI-technologie (very-large-scale integratie) presenteerden onze teams een aantal nieuwe apparaat-, materiaal- en integratie-innovaties gericht op het gebruik van SiGe met 10nm-grondregels, en ook als een weg voorwaarts om de schaalvergroting op te lossen. en prestatie-uitdagingen van het 7nm-testknooppunt dat we vorig jaar hebben gefabriceerd.

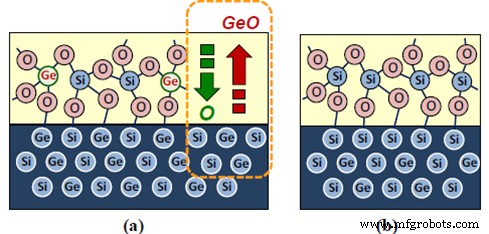

Onze presentaties hadden betrekking op kritische technische kenmerken en fundamentele procesinnovatie voor de beheersing van defecten; innovaties in gate-stack en grenslaag geschikt voor SiGe FIN; evenals geavanceerde contacttechnieken op het SiGe FinFET-platform, gerapporteerd in onderzoekspaper T2.2 op de VLSI-conferentie. Het onderzoekspaper T4.3 presenteerde het inventieve selectieve opruimingsproces van germaniumoxide om een robuuste grenslaag voor SiGe-kanalen te bouwen.

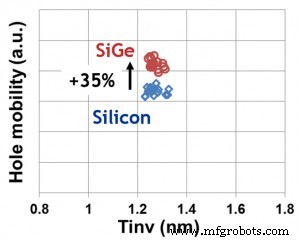

Duidelijke mobiliteit voordeel van SiGe Fin boven Si Fin, wat leidt tot prestatieverbetering op chipniveau.

Ons onderzoek onder leiding van Dr. Pouya Hashemi dat zich richt op de uitbreidbaarheid van SiGe FinFET-technologie voor toekomstige nodes met hogere prestaties, werd ook gepresenteerd op VLSI. In de T9.3-onderzoekspaper rapporteerden we de haalbaarheid van het bereiken van hogere prestaties met een hoger Ge-gehalte en een kleinere Fin-breedte en verdere gate-stackschaling. Deelnemers aan het VLSI Symposium kunnen deze technische papers vinden op de VLSI-website. Je kunt ook lid worden van hun Linkedin-groep voor meer informatie.

T2.2:FINFET-technologie met SiGe-kanaal met hoge mobiliteit voor 10nm en meer

T4.3:Selectieve GeOx - Opruimen van grensvlaklaag op Si1-x Gex Kanaal voor hoge mobiliteit Si/Si1-x Gex CMOS-toepassing

T9.3:Vervanging High-K/Metal-Gate High-Ge-Content gespannen SiGe FinFET's met hoge gatmobiliteit en uitstekende SS en betrouwbaarheid bij agressieve EOT ~7Å en verkleinde afmetingen tot sub-4nm vinbreedtes

T7.2:Ti en NiPt/Ti Liner Silicide-contacten voor geavanceerde technologieën

Schema van het inventieve selectieve GeOx-scavenging-proces (a) en de GeOx-vrije grenslaag (b) met SiGe-kanaal.

*-FinFET verwijst naar een transistorarchitectuur die het transistorkanaal verhoogt zodat het op vinnen lijkt)

Dechao Guo is onderzoeksmedewerker, meester-uitvinder en manager van Advanced Device Design &Integration bij IBM Research.

Nanomaterialen

- Naar Cloud Infinity en verder

- IBM bij SPIE:zeven verbeteringen voor meer dan 7nm-chips

- IoT Beyond PoC:een mentaliteitsverandering

- Digital Twin Technology:Beyond Rocket Science

- Machinevisie is de sleutel tot Industrie 4.0 en IoT

- Missouri Technology Corporation lanceert landelijk initiatief voor ondernemerschap en innovatie

- Hoe IoT en industriële automatisering innovatie stimuleren

- Samenwerking is essentieel voor Europa's geavanceerde productie- en technologiebedrijven (AMT)

- AMRC stimuleert innovatie in technologie en circulaire economie

- ABB Robotics:Technology Innovation and Robotics R&D

- Industrie 4.0:5G versnelt slimme fabrieksinnovatie