Het belang van betrouwbaarheidsverificatie in AI/ML-processors

Met de toepassing van kunstmatige intelligentie en machine learning in een breed scala aan toepassingen, is de betrouwbaarheidsverificatie van AI/ML-processors van cruciaal belang, aangezien storingen grote gevolgen kunnen hebben voor de validiteit en legitimiteit van AI/ML-technologie.

De afgelopen jaren is het aantal bedrijven dat kunstmatige intelligentie (AI) en machine learning (ML) inzet in een breed scala aan toepassingen snel gegroeid. Studies tonen zelfs aan dat 2019 een recordjaar was voor bedrijven die AI en ML adopteerden, en dat deze bedrijven deze twee functies als de meest noodzakelijke beschouwen om hun bedrijfsstrategieën en -doelen te bereiken. Deze groeiende acceptatie is voornamelijk te danken aan de verbetering van de algoritmen, verbeteringen in het hardwareontwerp en de toename van het gegevensvolume dat wordt gecreëerd door de digitalisering van informatie.

Om de groei van AI/ML te ondersteunen en te ondersteunen, moeten bedrijven echter aan de markt blijven bewijzen dat de resultaten die ze behalen met AI/ML-technologieën betrouwbaar zijn. Dat vertrouwen begint bij het ontwerp en de verificatie van de geïntegreerde schakelingen (IC's) die ten grondslag liggen aan AI/ML-functionaliteit.

Classificatie van AI en ML

AI-verwerking kan grofweg worden ingedeeld in datacenter/cloud-gebaseerd of ingebed, afhankelijk van of het wordt uitgevoerd op een cloud/datacenter-site, of aan de kant van de eindgebruiker (door een speciale AI-chip of een AI-coprocessor-engine in te bouwen met een system-on-chip (SOC) in apparaten of aan de rand). Edge verwijst in deze context naar een lokale server of een machine die dichter bij het apparaat staat dan een datacenter of cloud.

In termen van de doeltoepassing kan een edge-apparaat worden geclassificeerd in training (ML) of inferentie. Historisch gezien werd het trainingsgedeelte op de cloudsite uitgevoerd, waarbij het inferentiegedeelte in de cloud of op het edge-apparaat werd afgehandeld. Met de ontwikkeling van nieuwe high-performance edge computing-oplossingen zijn we getuige van een paradigmaverschuiving, aangezien steeds meer trainingsactiviteiten worden overgedragen aan de edge-kant.

AI/ML-chipontwerp

AI/ML-chips in edge computing-oplossingen of ingebed in lokale apparaten zijn ontworpen voor gebruik in specifieke omgevingen, zoals ondernemingen, auto's, industrie, gezondheidszorg, Internet of Things (IoT), enz. Sommige van deze toepassingen zijn bedrijfskritisch, wat betekent dat elke mislukking kan rampzalige gevolgen hebben in de echte wereld. Denk bijvoorbeeld aan geavanceerde rijhulpsystemen (ADAS) die in auto's worden gebruikt. Als een ADAS-processor meer dan een bepaalde latentie ervaart tijdens het lezen van gegevens van de sensor en het trekken van een gevolgtrekking, kan dit een botsing veroorzaken.

De IC's die worden gebruikt in AI/ML-toepassingen worden gekenmerkt door grote rekeneenheden voor parallelle verwerking, hoge vermogensdissipatie en complexe schakelingen die maximale prestaties kunnen leveren binnen een strikt stroombudget. Terwijl sommige bedrijven traditionele centrale verwerkingseenheden (CPU's) gebruiken voor AI-gerelateerde taken, beweren sommige branche-experts dat het gebruik van CPU's niet erg efficiënt is vanwege de gedistribueerde aard van geavanceerde AI-algoritmen. Deze algoritmen zijn geschikt voor parallelle computeroplossingen, zoals die van grafische verwerkingseenheden (GPU's). Vanwege hun herconfigureerbare karakter hebben veldprogrammeerbare poortarrays (FPGA's) ook belangstelling gewekt voor gebruik als versnellers voor AI-chips.

ASIC's in AI/ML-toepassingen

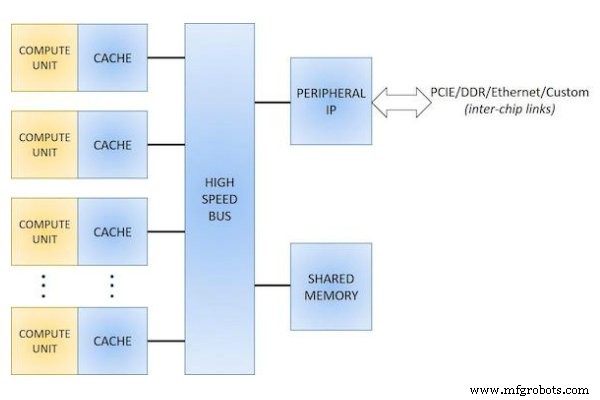

Over het algemeen is er een groeiende consensus dat de lastige problemen van AI en ML zich niet lenen voor een one-size-fits-all ontwerpoplossing. Om dit probleem aan te pakken, ontwikkelen veel bedrijven hun eigen applicatiespecifieke IC's (ASIC's), die ze optimaliseren in combinatie met de softwarestack om de beste waarde te leveren voor een bepaalde AI/ML-toepassing (Figuur 1).

Figuur 1. Blokschema voor een ASIC AI-chipontwerp.

Deze bedrijven claimen verschillende voordelen van het gebruik van deze ASIC's, zoals betere prestaties, meer bewerkingen per cyclus, een eenvoudiger en meer deterministisch ontwerp in vergelijking met een CPU of GPU, ruimtebesparing (door uitsluiting van complexe constructies en mechanismen die worden gebruikt in een CPU), lager stroomverbruik en snellere ontwikkeltijd.

Heterogene computers

Er is ook een toename in het gebruik van heterogene computersystemen:systemen die een combinatie van verschillende typen rekenkern gebruiken in een poging om het beste van verschillende mogelijkheden te combineren. In een systeem dat een combinatie van een CPU en een GPU gebruikt, kan heterogeen computergebruik bijvoorbeeld voordelig zijn door de parallelle taken naar de GPU te verplaatsen, terwijl de CPU taken afhandelt zoals procesbesturing, die van nature serieel is.

Een gemeenschappelijk aspect tussen verschillende klassen AI-processors is dat ze zijn geoptimaliseerd voor hoge prestaties en lage latentie, en vaak multipliers van tera-bewerkingen per seconde (TOPS) prestaties bieden. Om een voorsprong te krijgen in deze zeer competitieve markt, is energie-efficiëntie (gemeten aan de hand van prestaties per watt) net zo belangrijk geworden als de onbewerkte doorvoer. Energie-efficiëntie wordt vaak bereikt door een combinatie van een of meer ontwerptechnieken te gebruiken, zoals stroom- en klokgating, dynamische spannings- en frequentieschaling, multi-Vt-ontwerpen, enz.

Het is van cruciaal belang om te zorgen voor het betrouwbare ontwerp en de verificatie van deze complexe IC's, aangezien circuitstoringen in deze chips grote gevolgen kunnen hebben voor de validiteit van de technologie en de legitimiteit van de resultaten die ze opleveren.

AI/ML IC-betrouwbaarheidsverificatie

Betrouwbaarheidsverificatie is een enorme uitdaging in AI/ML-chips, vanwege de omvang en complexiteit van deze ontwerpen, met transistoraantallen in de orde van miljoenen - soms zelfs miljarden. De TESLA P100 GPU van NVIDIA heeft bijvoorbeeld een verbluffend aantal transistors van 15,3 miljard, terwijl Intel's Loihi IC 128 neuromorfe kernen en 3 X-86-kernen bevat, met 2,07 miljard transistors. En omdat de betrouwbaarheidsvereisten voor elke gebruiksomgeving anders zijn, moeten ontwerpers de toepasselijke reeks vereisten begrijpen en ervoor zorgen dat hieraan wordt voldaan door hun ontwerpen te testen aan de hand van goed gedefinieerde specificaties voor betrouwbaarheidsvereisten.

Ontwerp Betrouwbaarheid Verificatie Methoden

Traditioneel gebruikten ontwerpers verschillende methoden om de betrouwbaarheid van het ontwerp te garanderen, waaronder handmatige inspectie en simulatietechnieken, waarbij ze voornamelijk vertrouwden op de expertise en ervaring van hun ontwerpteam. Handmatige inspectie is echter geen haalbare aanpak voor deze grote en complexe AI/ML-chips, omdat het tijdrovend en vatbaar is voor menselijke fouten, en vrijwel onmogelijk om voldoende dekking te bieden. Traditionele SPICE-achtige simulatiebenaderingen zijn ook niet praktisch voor deze IC's, vanwege hun gebrek aan schaalbaarheid voor grote ontwerpen.

Om capaciteits- en runtimeproblemen op te lossen, partitioneren veel ontwerpteams handmatig een ontwerp en verifiëren ze verschillende blokken voor intellectueel eigendom (IP) onafhankelijk van elkaar door middel van simulatie of traditionele tools. Er zijn echter veel interacties tussen verschillende IP-blokken in een ontwerp (bijvoorbeeld tussen verschillende rekenkernen en de bus of link of geheugen met hoge bandbreedte), en de interacties tussen interfaces worden vaak over het hoofd gezien tijdens een handmatig partitioneringsproces. Traditionele IC-verificatietools worstelen met extreem lange runtimes om deze complexe ontwerpen te verifiëren, waarbij het vaak dagen duurt om grote ontwerpen te verifiëren en de time-to-market mogelijk vertraging oploopt.

De tekortkomingen in elk van deze processen benadrukken de behoefte aan een uitgebreide geautomatiseerde elektronische ontwerpautomatisering (EDA)-oplossing die kan profiteren van de rekenkracht van meerdere CPU's en apparaten tegelijk. Met geautomatiseerde, gekwalificeerde betrouwbaarheidsverificatie kunnen productontwerp- en verificatieteams sneller convergeren op het gebied van betrouwbaarheidsverificatie en oplossingen, waardoor hun totale doorlooptijd (TAT) van dagen naar uren wordt verkort.

Het Calibre PERC-betrouwbaarheidsplatform

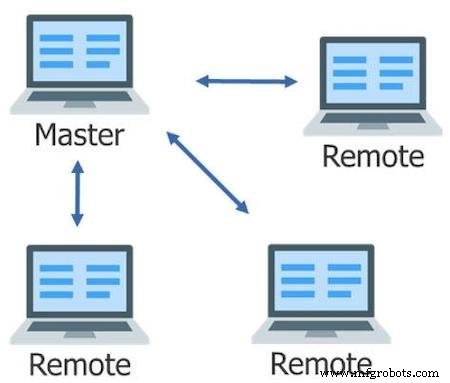

In de afgelopen jaren is er een nieuwe klasse van IC-betrouwbaarheidsverificatietools ontstaan die deze procesproblemen oplossen. Tools zoals het Calibre™ PERC™-betrouwbaarheidsplatform maken gebruik van een uitgebreide reeks functies en functionaliteit om snelle, gieterij-gekwalificeerde betrouwbaarheidsverificatie te leveren. Het Caliber PERC-betrouwbaarheidsplatform maakt bijvoorbeeld gebruik van de multi-threaded (MT) en multi-threaded flexibele (MTflex) schaling van het Calibre-platform, die taken verdeelt over meerdere CPU's en/of externe machines om een snelle, efficiënte uitvoering van verificatieprocessen te bieden. op grote en complexe chips zoals AI/ML IC's (Figuur 2).

Figuur 2. Multi-threaded, flexibele schaalverdeling verdeelt taken over meerdere afstandsbedieningen voor een snellere algehele uitvoering.

Naast deze elementaire maar essentiële mechanica, biedt het Calibre PERC-betrouwbaarheidsplatform innovatieve verwerking die zowel netlijst- als lay-outinformatie uit een ontwerp combineert om snel en nauwkeurig een breed scala aan potentiële betrouwbaarheidsproblemen te evalueren. Door ontwerpers in staat te stellen de gevoeligheid van een ontwerp voor prestaties en operationele storingen efficiënt en vol vertrouwen te verminderen, helpt deze benadering van geavanceerde betrouwbaarheidsverificatie de aanhoudende groei en acceptatie van vertrouwde AI/ML-technologie te ondersteunen.

Betrouwbaarheid op transistorniveau

De meeste ML/AI-ontwerpen gebruiken meerdere vermogensdomeinen voor verschillende doeleinden, zoals het bieden van een schone, ruisvrije voeding voor analoge IP, waardoor de mogelijkheid wordt geboden om de stroom naar een bepaald gebied van een chip te poorten of uit te schakelen, spanningen onafhankelijk omhoog of omlaag voor geselecteerde IP's, of voldoen aan hoge stroomvereisten met behulp van meerdere spanningsregelaars. Intel's Skylake-processor bevat bijvoorbeeld negen primaire vermogensdomeinen.

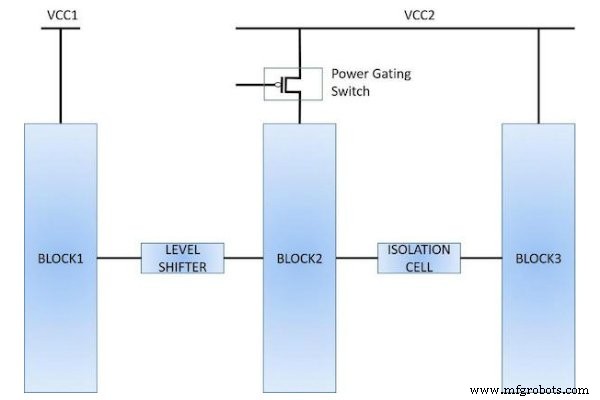

Het implementeren van een ontwerp met meerdere vermogensdomeinen vereist het gebruik van speciale circuitelementen, zoals spanningsregelaars, kop- en voettekstschakelaars, niveauverschuivers, isolatiecellen en statusretentiecellen. Deze elementen vormen een unieke reeks uitdagingen voor betrouwbaarheidsverificatie. Ontwerpers moeten bijvoorbeeld controleren of de juiste niveauverschuiver of isolatiecellen worden gebruikt bij elke domeininterface en dat ze correct zijn aangesloten (Afbeelding 3).

Figuur 3. Het gebruik van speciale elementen (zoals niveauverschuivers, isolatiecellen en vermogensschakelaars) in een ontwerp met laag vermogen vereist gespecialiseerde verificatietechnieken.

Ze moeten er ook voor zorgen dat ze de juiste soorten apparaten gebruiken op verschillende vermogensdomeinen, zoals dikoxide-apparaten voor hoogspanningsvoeding. Het verifiëren van deze voorwaarden vereist zeer specifieke kennis en processen.

De Unified Power Format-techniek

Het unified power format (UPF) is een veelgebruikte techniek die ontwerpers in staat stelt om een consistente beschrijving van de intentie van het vermogen te gebruiken tijdens het ontwerpproces. Traditionele op UPF gebaseerde verificatiestromen worden echter gebruikt om IP's op logisch of poortniveau te valideren, maar ze missen de mogelijkheid om de uiteindelijke implementaties op transistorniveau te valideren, met name de bron- en bulkverbindingen.

Het Caliber PERC-betrouwbaarheidsplatform kan het UPF-bestand lezen voor een ontwerp en UPF-informatie gebruiken om verschillende analyses op transistorniveau uit te voeren, zoals het identificeren van ontbrekende of onjuist aangesloten niveauverschuivers, elektrische overbelasting (EOS)-omstandigheden, drijvende putten en nog veel meer . Door het Calibre PERC-betrouwbaarheidsplatform te gebruiken in combinatie met de UPF-gegevens, kunnen ontwerpers apparaatinteracties programmatisch evalueren om herhaalbare en deterministische betrouwbaarheidsverificatie te bieden.

Levenslange betrouwbaarheid van AI/ML-chips

Operationele veiligheid is een cruciaal aspect voor de meeste AI/ML-chips, die naar verwachting gedurende hun ontworpen levensduur zonder storingen of storingen zullen werken. Sommige problemen met de elektrische betrouwbaarheid, zoals bias-temperatuurinstabiliteit (BTI) en EOS, manifesteren zich mogelijk niet als onmiddellijke storingen, maar kunnen in de loop van de tijd snelle degradatie en veroudering veroorzaken als ze niet vóór de productie worden gecorrigeerd. Betrouwbaarheidsverificatie kan helpen zorgen voor een robuuste werking over een langere periode door te controleren op verschillende problemen, zoals point-to-point-weerstand, positieve en negatieve BTI, stroomdichtheid en elektromigratie (EM), die allemaal kunnen leiden tot prestatievermindering of catastrofale storingen.

Overweeg het geval waarin een hoogspanningsdomeinapparaat een apparaat met dunne oxide aanstuurt dat niet geschikt is om de hoogspanning aan te kunnen. Tijdens het ontwerp slaagt de ontwerper er niet in om een shifter van hoog en laag niveau in te voegen. Hoewel deze toestand in eerste instantie niet noodzakelijkerwijs van invloed is op de functionaliteit, zal het na verloop van tijd het dunne-oxide-apparaat belasten, wat uiteindelijk tot storingen kan leiden. De werkelijke uitvaltijd is afhankelijk van de spanningswaarde, tijd waarin de voeding AAN versus UIT staat en de procesparameters.

EM (de migratie van atomen in een geleider als gevolg van elektrische stroom) is een ander belangrijk probleem dat van invloed is op de robuustheid op lange termijn van verbindingen die worden gebruikt in AI/ML IC's. Deze migratie veroorzaakt holtes en heuvels op draden. De holtes veroorzaken een aanzienlijke toename van de weerstand, terwijl de heuvels kortsluiting kunnen veroorzaken, die beide leiden tot circuitstoringen. Het EM-effect is afhankelijk van veel factoren, zoals de lengte en breedte van de metalen lijn, het materiaal van de verbinding, de bedrijfstemperatuur, unidirectionele vs. bidirectionele stromen, enz.

Gieterijen bieden ontwerpbedrijven EM-limieten voor de maximale stroom die de draden aankunnen, op basis van de verwachte gebruiksomstandigheden voor het product. De EM-limieten voor een IC die in een mobiele telefoon wordt gebruikt, zouden bijvoorbeeld aanzienlijk lager zijn dan voor een IC die in een industriële omgeving wordt gebruikt. Sommige bedrijven hebben toegewijde teams die actief samenwerken met de gieterij om de juiste specificaties te definiëren, teststructuren te creëren en productkwalificatie voor EM-tolerantie uit te voeren. Het is duidelijk dat het moeilijker is om deze limieten te definiëren voor een product dat in meerdere omgevingen kan worden gebruikt, dus ontwerpen ontwerpers deze chips meestal voor de slechtste bedrijfsomstandigheden. In alle gevallen is het cruciaal om het ontwerp te toetsen aan de door de gieterij gedefinieerde EM-limieten en te valideren dat het ontwerp bestand is tegen EM-effecten.

Als de verschillende betrouwbaarheidsproblemen tijdens de pre-siliciumverificatiefase niet worden opgemerkt en gecorrigeerd, kan dit leiden tot een breed scala aan effecten, waaronder meerdere tape-out-spins, vertragingen bij het op de markt brengen van het product, verlies van klantenvertrouwen, significante negatieve marktreacties, terugroepacties van producten en zelfs catastrofale gevolgen, zoals lichamelijk letsel of overlijden. Door schendingen van de betrouwbaarheid te identificeren en op te lossen voordat tape-out optreedt, wordt de kans op circuitstoringen of storingen geminimaliseerd die kostbaar kunnen blijken te zijn.

Analyse en beheer van AI/ML-betrouwbaarheid is cruciaal

Het recente succes van en uitbreiding van AI/ML-functionaliteit is grotendeels gebaseerd op de vooruitgang in de halfgeleidertechnologie. Terwijl deze nieuwe ontwerpen worden ontwikkeld, moet de hardware-ontwerpgemeenschap zich bewust zijn van de noodzaak om de betrouwbaarheidsaspecten van een ontwerp te analyseren en te beheren, zoals de doelomgeving, bedrijfsomstandigheden, betrouwbaarheidscriteria, enz. Krachtige EDA-hulpmiddelen voor betrouwbaarheidsverificatie die zijn ontworpen om de specifieke betrouwbaarheidsproblemen en vereisten van deze grote, complexe chips kunnen ontwerphuizen helpen ervoor te zorgen dat hun producten gedurende hun ontworpen levensduur presteren zoals bedoeld. Dat vertaalt zich op zijn beurt in vertrouwen in de resultaten die zijn behaald door het gebruik van AI/ML-toepassingen in de bredere markten, wat het voortdurende gebruik en de uitbreiding ervan ondersteunt.

Industrieartikelen zijn een vorm van inhoud waarmee branchepartners nuttig nieuws, berichten en technologie kunnen delen met lezers van All About Circuits op een manier waarop redactionele inhoud niet goed geschikt is. Alle brancheartikelen zijn onderworpen aan strikte redactionele richtlijnen met de bedoeling de lezers nuttig nieuws, technische expertise of verhalen te bieden. De standpunten en meningen in brancheartikelen zijn die van de partner en niet noodzakelijk die van All About Circuits of zijn schrijvers.

Internet of Things-technologie

- Het belang van elektrische veiligheid

- Wat is de rol van de betrouwbaarheidsingenieur?

- De nr. 1 sleutel tot betrouwbaarheidssucces

- Het belang van kerncompetenties

- De niet-technische kant van betrouwbaarheid

- Het belang van trends in de betrouwbaarheid van elektromotoren

- Het belang van routinematig onderhoud van apparatuur

- Het belang van snelle bewerking in de productie

- Het belang van analyse van hoofdoorzaken

- Het belang van noodplanning

- Het belang van water