Hoe processors betrouwbaar te maken

Moderne geïntegreerde schakelingen (IC's) bieden de reken- en systeemcontrolemogelijkheden om enorme hoeveelheden gegevens te verwerken, in realtime veiligheidskritieke beslissingen te nemen en gevoelige gegevens te beschermen. Het helemaal opnieuw ontwerpen van een applicatiespecifieke geïntegreerde schakeling (ASIC) of field-programmable gate array (FPGA) system-on-chip (SoC) zou onbetaalbaar en tijdrovend zijn. Veel kritieke functies worden geïmplementeerd met behulp van intellectuele eigendommen (IP's) van derden. Processorcores zijn bijvoorbeeld afkomstig van gespecialiseerde organisaties en bieden een flexibele, software-programmeerbare functie via hun instructiesetarchitectuur (ISA), die de interface tussen hardware en software definieert. Open-source processorarchitecturen bieden de mogelijkheid voor dieper onderzoek en rigoureuze beveiligingsgarantie in systemen die al worden geconfronteerd met een vloeiende bedreigingsomgeving. Dit artikel beschrijft een benadering voor het bieden van beveiligingsgaranties voor IP en SoC's op basis van de RISC-V open-source ISA.

RISC-V is uitgevonden aan de Universiteit van Californië en wordt beheerd door de non-profit RISC-V Foundation. Het is de eerste open-source ISA die een echt levensvatbare industriële keuze wordt voor een breed scala aan toepassingen.

RISC-V is een open-source ISA die is uitgevonden aan de Universiteit van Californië en wordt beheerd door de RISC-V Foundation, een non-profitorganisatie met meer dan 300 leden, opgericht in 2015. RISC-V is de eerste open-source ISA die een echt levensvatbare industriële keuze voor een breed scala aan toepassingen. Het ecosysteem van tools, software en expertise is robuust en groeit gestaag. Veel individuen en organisaties hebben al open-source hardware-IP's gedoneerd om de RISC-V ISA te implementeren. De OpenHW Group streeft er bijvoorbeeld naar om het langverwachte vooruitzicht van open-source hardware – met name processorkernen – voor high-volume chips te realiseren.

De opkomst van RISC-V heeft vele redenen. RISC-V is vanaf de grond opgebouwd met aangepaste uitbreidbaarheid in het achterhoofd en maakt een nieuw niveau van hardware-optimalisatie voor specifieke workloads mogelijk. De wet van Moore vertraagt en maatwerk is cruciaal om het niveau van prestatieverbeteringen in stand te houden dat technologische vooruitgang in het fabricageproces van halfgeleiders niet langer kan bieden. Bovendien is de RISC-V-architectuur vrij van licentiekosten en royalty's, waardoor meer bedrijven innovatieve, betaalbare producten kunnen ontwikkelen. Er gebeurt veel op het gebied van bijvoorbeeld IoT en wearables met artificial intelligence-mogelijkheden.

SoC-integrators gebruiken vaak open-source of RISC-V-processor-IP's van derden. Deze ontwerpen en de bijbehorende toolchains kunnen worden aangevuld met aangepaste instructies. Een verificatieomgeving van hoge kwaliteit die wordt geleverd met het IP-adres en aanvullende tests op systeemniveau kunnen enig vertrouwen geven dat het IP geen kritieke bugs bevat. Helaas is dit voor veel toepassingen niet genoeg en zijn er andere ernstige risico's waarmee rekening moet worden gehouden.

Kwetsbaarheden en Trojaanse paarden

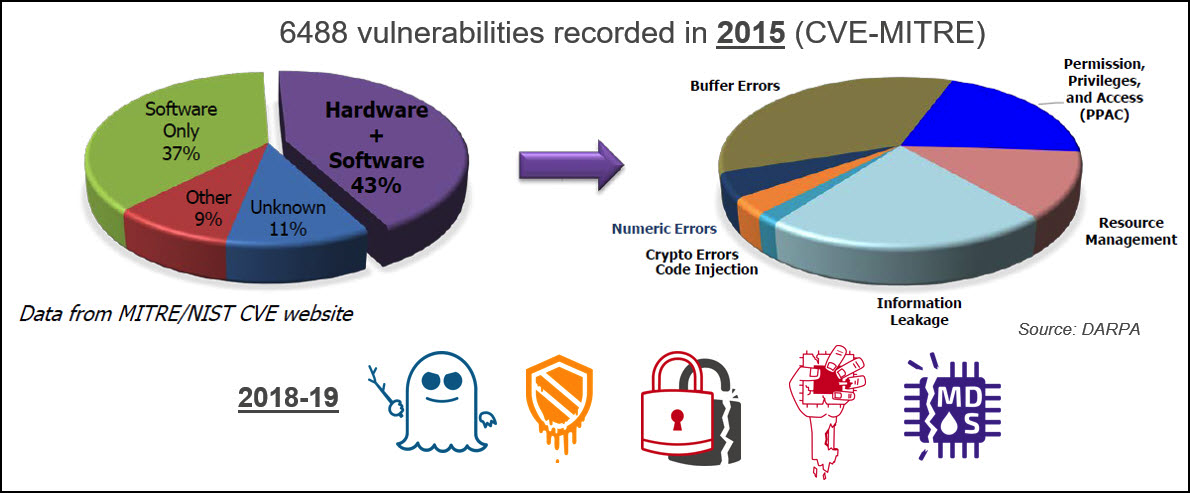

Traditioneel werden beveiligingsproblemen in elektronische systemen in verband gebracht met systeem- en softwareproblemen. Meer recentelijk zijn hardware-IP's, met name processors, ook een centraal punt van zorg geworden (zie figuur 1). Processorimplementaties maken gebruik van op pijplijnen gebaseerde micro-architecturen en bevatten vaak functies voor prestatie- en stroomoptimalisatie. Complexiteit vergroot het risico dat niet alleen functionele bugs worden gemist, maar ook beveiligingsproblemen. De beveiligingsonderzoekers die begin 2018 de Meltdown- en Spectre-aanvallen ontdekten, hebben aangetoond dat prestatie-optimalisatiefuncties in processors op onbedoelde manieren kunnen worden gebruikt voor snode doeleinden. Sindsdien zijn er veel meer kwetsbaarheden ontdekt in zowel high-end als low-end processors. Zijkanalen en tijdelijke uitvoeringsaanvallen kunnen beveiligde enclaves binnendringen en kwaadwillende toepassingen toestaan vertrouwelijke gegevens te lekken of zelfs de controle over het systeem over te nemen. En in tegenstelling tot software kunnen hardwareproblemen niet eenvoudig worden gerepareerd met draadloze updates. Het oplossen van een hardwareprobleem via software veroorzaakt vaak ernstige prestatievermindering.

De RISC-V-architectuur heeft veel functies die de implementatie van veilige embedded systemen ondersteunen. De privilegespecificatie definieert bijvoorbeeld vier privilegemodi (machine, supervisor, hypervisor en gebruiker). Aangepaste instructies en ISA-extensies die worden geratificeerd, zoals de Cryptographic-extensie, bieden extra beveiligingsmogelijkheden. Ontwerpers kunnen meerdere veilige enclaves implementeren om applicaties te isoleren en het lekken van gevoelige gegevens te voorkomen. Micro-architecturale functies van RTL kunnen echter nog steeds leiden tot beveiligingsproblemen. Deze risico's kunnen niet volledig op ISA-niveau worden aangepakt. Een nieuwe benadering die momenteel wordt onderzocht, is het gebruik van een augmented ISA (aISA) om aspecten van instructie-uitvoering op micro-architecturaal niveau te definiëren en bijvoorbeeld de status van buffers of registers te controleren die niet zichtbaar zijn op ISA-niveau. Functionele bugs van RTL kunnen nog steeds al deze beveiligingsfuncties in gevaar brengen.

Een minder waarschijnlijk risico, maar met een veel hogere ernst, is de aanwezigheid van kwaadaardige logica of hardware-trojans in de RISC-V-kern. Een hardware Trojaans paard is een logische functie die opzettelijk is ontworpen om onopvallend te zijn, die in zeer zeldzame omstandigheden wordt geactiveerd die alleen bekend zijn bij de aanvaller. Een specifieke reeks gegevens en controlegebeurtenissen die niet zouden plaatsvinden terwijl het systeem in de beoogde use-cases werkt, activeert de Trojaanse logica, die op zijn beurt een schadelijke lading levert, bijvoorbeeld een geheim lekt of het systeemgedrag kritisch corrumpeert. SoC-integraties die open-source of RISC-V-kernen van derden gebruiken, kunnen dit risico niet langer negeren.

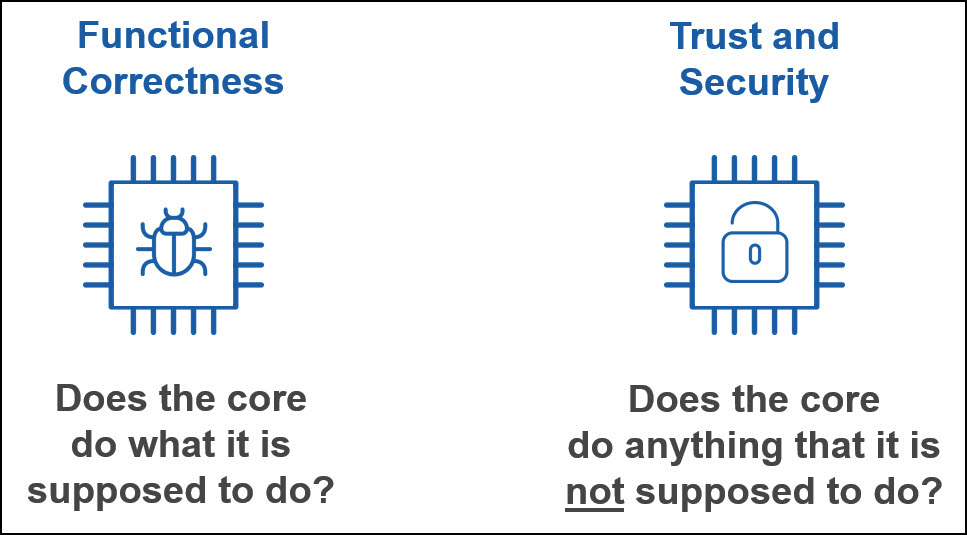

Ervoor zorgen dat een processor doet wat hij moet doen, is moeilijk, maar ervoor zorgen dat hij niets doet wat hij niet zou moeten doen, is een nog grotere uitdaging die nog grotendeels niet is aangepakt. Veiligheidskritieke systemen en systemen waarbij de bescherming van gegevensprivacy van het grootste belang is, hebben efficiënte, hoogwaardige oplossingen nodig die het risico van beveiligingsproblemen en Trojaanse paarden aanpakken.

Figuur 1:De CVE-MITRE-database registreerde 6488 kwetsbaarheden in 2015, waarvan 43% kan worden geclassificeerd als software-ondersteunde hardwarekwetsbaarheden. In 2018 en 2019 hebben onderzoekers talloze kwetsbaarheden in processors ontdekt en gerapporteerd, waaronder Meltdown en Spectre, Foreshadow, ZombieLoad en RIDL en Fallout. (Bron:DARPA en OneSpin)

Smart Hardware Assurance

Het verzekeren van het vertrouwen en de veiligheid van RISC-V IP's vereist innovatieve en efficiënte technische oplossingen die complementair zijn aan functionele correctheidsbenaderingen, voornamelijk gericht op de beoogde IP-gebruikscasussen (zie figuur 2). IP-providers zijn verantwoordelijk voor het toepassen van de modernste processen voor vertrouwens- en beveiligingsverificatie, terwijl IP-integrators toegang moeten hebben tot onafhankelijke assurance-oplossingen die snel en zonder diepgaande kennis van de IP-implementatiedetails kunnen worden ingezet.

Formele methoden kunnen hardwarefuncties uitputtend analyseren en het bewijs leveren dat de IP of SoC precies overeenkomt met een verwacht gedrag dat vaak wordt vastgelegd in SystemVerilog-beweringen. Formele verificatie van hardware met behulp van commerciële modelcontroles is de afgelopen tien jaar wijdverbreid toegepast. Doorgaans hebben IP-providers en SoC-integrators formele verificatie-experts in hun gelederen, die proberen het risico van ontbrekende functionele bugs tot een minimum te beperken. Hoewel bepaalde goed gedefinieerde formele verificatietaken kunnen worden geautomatiseerd via Apps In het algemeen zijn aanzienlijke technische inspanningen nodig om het verwachte gedrag van de IP in beweringen vast te leggen. Verder is er geen garantie dat er voldoende beweringen zijn geschreven. Niet-gedocumenteerde functies of onbedoelde hiaten in de reeks beweringen kunnen leiden tot niet-geverifieerde IP-functionaliteit.

Het open-source karakter van RISC-V maakt de ontwikkeling van voorverpakte, onafhankelijke assurance-oplossingen mogelijk. De RISC-V Integrity Verification-oplossing van OneSpin kan bijvoorbeeld worden toegepast op een breed scala aan micro-architecturen. Het bevat modellen van de RISC-V ISA en geprivilegieerde ISA die uitbreidbaar zijn en geschikt zijn voor aangepaste instructies. Een cruciaal aspect van deze oplossing is dat deze is gebaseerd op het GapFreeVerification™-proces van OneSpin, dat een rigoureus bewijs levert dat de reeks beweringen die de RISC-V ISA modelleren, compleet en vrij van hiaten is. Dit aspect is van het grootste belang wanneer de detectie van hardware-trojans of ongedocumenteerde logica een cruciaal doel is. De oplossing stelt SoC-integrators met beperkte expertise op het gebied van RISC-V en de RTL-implementatie die onder de loep wordt genomen, in staat om vertrouwen te krijgen in de kwaliteit en betrouwbaarheid van de IP. IP-ontwikkelaars kunnen het gebruiken om zwakke punten in de beveiliging en functionele bugs te detecteren voordat ze worden vrijgegeven.

Figuur 2:Verificatie van functionele correctheid geeft vertrouwen dat een processorimplementatie zich gedraagt zoals gespecificeerd en voldoet aan de eisen van eindgebruikers. Vertrouwens- en beveiligingsverificatie daarentegen geeft het vertrouwen dat de processor geen ongedocumenteerde functies, onvoorziene zijkanalen, hardware-trojans of andere kwetsbaarheden heeft die door kwaadwillende actoren kunnen worden uitgebuit. (Bron:OneSpin)

Werkt het?

Het in de vorige paragraaf beschreven RISC-V-proces voor integriteitsborging is met succes toegepast op meerdere RTL-ontwerpen. Edaptive Computing, een bedrijf dat innovatieve oplossingen integreert om systemen van systemen en processen snel te optimaliseren, verzekeren en automatiseren voor een verscheidenheid aan klanten van het Amerikaanse ministerie van Defensie en de commerciële sector, heeft het proces bijvoorbeeld toegepast op de RocketCore. De RocketCore is een open-source, in silicium bewezen 64-bit RISC-V-kern met een 39-bit virtueel geheugensysteem. Het heeft een vijftraps, single-issue, in-order pijplijn met out-of-order voltooiing voor lange latentie instructies zoals deling. Het bevat de geavanceerde functies van vertakkingsvoorspelling en het opnieuw afspelen van instructies.

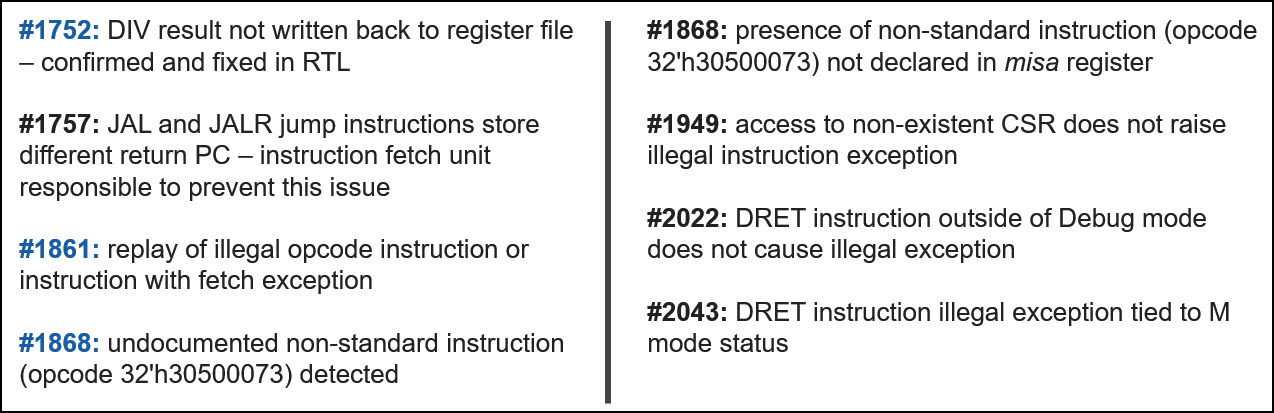

De RISC-V Integrity Verification Solution werd toegepast op het ontwerp met alle instructies, privilegeniveaus, interrupts en uitzonderingsmechanisme, en er werden 8 problemen gedetecteerd (zie Fig. 3). Aanvullende informatie over 3 van hen wordt hieronder vermeld.

Divisie hoekkast :een diepe bug in de hoek die verband houdt met het buiten de juiste volgorde voltooien van de divisie-instructie. Dit probleem kan ertoe hebben geleid dat een softwareprogramma dat de delingsbewerking gebruikt, onjuiste resultaten berekent en tot wangedrag van het systeem heeft geleid. Het probleem doet zich alleen voor onder een combinatie van zeldzame omstandigheden, en dat is de reden waarom eerdere verificatie-inspanningen het over het hoofd hadden gezien.

Herhaling van illegale instructie :dit is geen bug in de hoek. Het herhalen van een illegale instructie kan verwerkingscycli verspillen, maar als dit alleen in zeldzame situaties gebeurt, is de prestatie-impact te verwaarlozen. Er zijn echter andere aspecten waarmee rekening moet worden gehouden. Het opnieuw afspelen van instructies kan onnodige geheugenverzoeken veroorzaken. Deze verzoeken kunnen bijwerkingen hebben die kunnen worden gebruikt bij zijkanaalaanvallen. Als gevolg hiervan moet dit gedrag ofwel worden geëlimineerd of duidelijk worden begrepen en gedocumenteerd.

Ongedocumenteerde instructie :een ongedocumenteerde, niet-standaard instructie genaamd CEASE die de kern stopt, is gedetecteerd. In feite kon de RISC-V RocketCore iets doen wat niet de bedoeling was. Niet-gedocumenteerde, verborgen functies zijn niet acceptabel wanneer vertrouwen en veiligheid een punt van zorg zijn, zelfs als ze betrekking hebben op use-cases die niet relevant worden geacht voor de eindtoepassing.

De RocketCore-casestudy wordt in detail gepresenteerd in de GOMACTech 2019-paper met de titel Complete Formal Verification of RISC-V Processor IPs for Trojan-Free Trusted ICs. Ga voor een exemplaar naar onepin.com/resources/white-papers.

Figuur 3:Lijst met problemen die zijn gedetecteerd door OneSpin's RISC-V Integrity Verification Solutions en gerapporteerd in het GitHub RocketCore-project. (Bron:OneSpin)

Wat nu?

Het RISC-V-borgingsproces dat in dit artikel wordt gepresenteerd, detecteert scenario's die de beveiliging kunnen beïnvloeden en onthult systematisch ongedocumenteerde functies en hardware-trojans die het gedrag van de processor beïnvloeden, ongeacht hoe zeldzaam en onopvallend ze ook zijn. Zijkanalen worden echter niet systematisch opgespoord. Een uitgebreide detectie van alle potentiële zijkanalen vereist een speciale oplossing met de juiste technologie. Er zijn al prototypes die deze uitdaging aangaan. Ga voor meer informatie naar onepin.com/resources/technical-articles en lees het EE Times-artikel Side-Channel Attacks on Embedded Processors.

Processorcores zijn cruciale IP's binnen embedded systemen. Een typische SoC integreert echter veel andere IP's die ook hardware-trojans kunnen bevatten. In tegenstelling tot RISC-V-cores zijn onafhankelijke oplossingen voor vertrouwensgarantie mogelijk niet direct beschikbaar. In dit geval zou het waardevol zijn om een geautomatiseerd, moeiteloos vertrouwensbeoordelingsproces te hebben dat van toepassing is op elke IP. Een proces dat geen vertrouwd IP-model bevat, kan de afwezigheid van een Trojaans paard niet garanderen. Het is echter mogelijk om ongebruikelijke en verdachte codepatronen en bekende Trojaanse handtekeningen te identificeren, en zwakke punten die in latere ontwikkelingsstadia voor snode doeleinden kunnen worden misbruikt. Een paper over dit onderwerp getiteld An Automated Pre-Silicon IP Trustworthiness Assessment for Hardware Assurance , geschreven door AEROSPACE Corporation en OneSpin-ingenieurs, zal worden gepresenteerd op de GOMACTech 2020-conferentie.

Ingebed

- Hoe u het meeste uit uw gegevens haalt

- Een gids voor het versnellen van applicaties met precies de juiste RISC-V aangepaste instructies

- Hoe maak je een Arduino+Raspberry Pi-robotplatform

- Hoe u op conditie gebaseerd onderhoud effectiever kunt maken

- Hoe maak je glasvezel

- Hoe u supply chain-gegevens betrouwbaar maakt

- Hoe maak je een Cutaway-animatie in Solidworks

- Hoe maak je een prototype?

- Een hydraulische slang vervangen

- Hoe u een uitgebreid veiligheidsprogramma kunt laten werken

- Hoe maak je een metalen klauwplaat