Een gids voor het versnellen van applicaties met precies de juiste RISC-V aangepaste instructies

De open instructieset-architectuur (ISA) van RISC-V maakt een brede flexibiliteit bij de implementatie mogelijk en biedt optionele functies die nieuwe benaderingen mogelijk maken voor het oplossen van compromissen tussen hardware en software. Op basis van een modulaire opbouw kunnen een aantal standaard uitbreidingen en opties worden gebruikt om de basisprocessor als uitgangspunt te configureren. Maar de echte waarde ligt eigenlijk in de kansen die RISC-V ontwikkelaars biedt om nieuwe uitbreidingen, instructies en configuraties te creëren die op unieke wijze voldoen aan de behoeften van hun innovatieve toepassingsideeën.

De software-uitdaging voor vaste ISA's

Van oudsher zijn ISA's het intellectuele eigendom (IP) van commerciële organisaties die ofwel microprocessors of microcontrollers wilden verkopen, of die hun ontwerpen in licentie wilden geven voor gebruik door anderen. Ingebedde ontwikkelaars worden overgelaten om benchmarkingsoftware uit te voeren om te bepalen welke oplossing het beste is geoptimaliseerd voor hun toepassingsbehoeften. Vanwege de kosten van het ontwikkelen van een onafhankelijke ISA met al het noodzakelijke ecosysteem, vertrouwden halfgeleiderleveranciers steeds meer op de standaard vaste ISA's die worden aangeboden door de reguliere IP-providers, vertrouwend op de wet van Moore en geïntegreerde randapparatuur om differentiatie te leveren, zoals ultra-low power , aan hun klanten.

De uitdaging hier is dat de instructies die worden gebruikt om code uit te voeren niet kunnen worden gewijzigd. Daarom kunnen efficiëntieverbeteringen die mogelijk worden behaald door bijvoorbeeld een geoptimaliseerde instructie voor een versleutelingsalgoritme niet worden gerealiseerd. Dit kan betekenen dat de applicatie van de ontwikkelaar te traag is, mogelijk te veel stroom verbruikt of regelmatig een harde realtime deadline mist in een regelkring. Zelfs met de beste wil van de wereld zijn dit factoren die een uitdaging vormen om louter met verbeteringen in de halfgeleiderfabricage of proceskrimp op te lossen.

De RISC-V ISA begon als een project aan de University of California, Berkeley en wordt nu onderhouden door de RISC-V International Association, een non-profitgroep met meer dan 300 leden. Deze dragen bij aan de ISA-specificaties, softwaretools, zoals simulatoren en compilers, en de rest van het ecosysteem dat nodig is om een dergelijke onderneming te ondersteunen. Of het al dan niet zinvol is om te gebruiken, hangt af van het feit of een van de twee factoren kan worden benut:het is gratis in termen van licentie, of de vrijheid die het biedt.

Omdat het open en vrij beschikbaar is, biedt het een basisverwerkingsplatform dat gemakkelijk kan worden gebruikt door zowel de academische wereld voor onderwijs en onderzoek als voor commerciële toepassingen. Een open ISA ondersteunt ook een aantal bedrijfsmodellen voor ontwikkelaars die halfgeleider-IP willen sourcen, van de commerciële IP-provider tot open source-projecten en schone, zelfgebouwde ontwerpen. Commerciële organisaties vinden dit ook aantrekkelijk en gebruiken het in FPGA's, SoC's of zelfs de kern van een microcontroller of standaard productaanbod.

Dankzij de vrijheid die het biedt, kan de academische wereld nieuwe benaderingen onderzoeken om computeruitdagingen aan te pakken, door alles te implementeren van nieuwe instructies en andere versnellers, multi-core en veel-core heterogene ontwerpen plus verschillende microarchitectuur-opties. Veel van deze opties zijn ook aantrekkelijk voor startups en bedrijven die complexe uitdagingen willen aanpakken, zoals low-power artificial intelligence (AI)-chipsets die aan de rand werken, door aangepaste instructies toe te voegen die zijn afgestemd op de vereisten van de eindtoepassing.

Aangezien het ecosysteem is opgezet met ingebouwde RISC-V-flexibiliteit, moet elke standaardconfiguratie of aangepaste extensie in staat zijn om de tools en software binnen het ISA-conforme raamwerk te benutten.

De flexibiliteit van de open RISC-V ISA begrijpen

Dankzij de toegankelijkheid van de RISC-V ISA en bijbehorende tools is het eenvoudig om een onderzoeksproject op te starten om de geschiktheid ervan voor gebruik in een specifieke toepassing te beoordelen. Met simulatietools kan een standaard basis-ISA worden uitgeprobeerd om de out-of-the-box-prestaties te bepalen. Een goed startpunt zou bijvoorbeeld een 32-bits RISC-V-configuratie zijn met integer "I" en vermenigvuldigen "M" extensies (waarnaar kan worden verwezen als RV32IM) die ondersteuning bieden voor een basis 32-bit integer instructieset; er zijn meer opties beschikbaar, maar dit is voldoende voor dit voorbeeld. Dit wordt vervolgens geïnstantieerd samen met een gesimuleerd geheugen inclusief toegangsvertragingen en wachtstatussen.

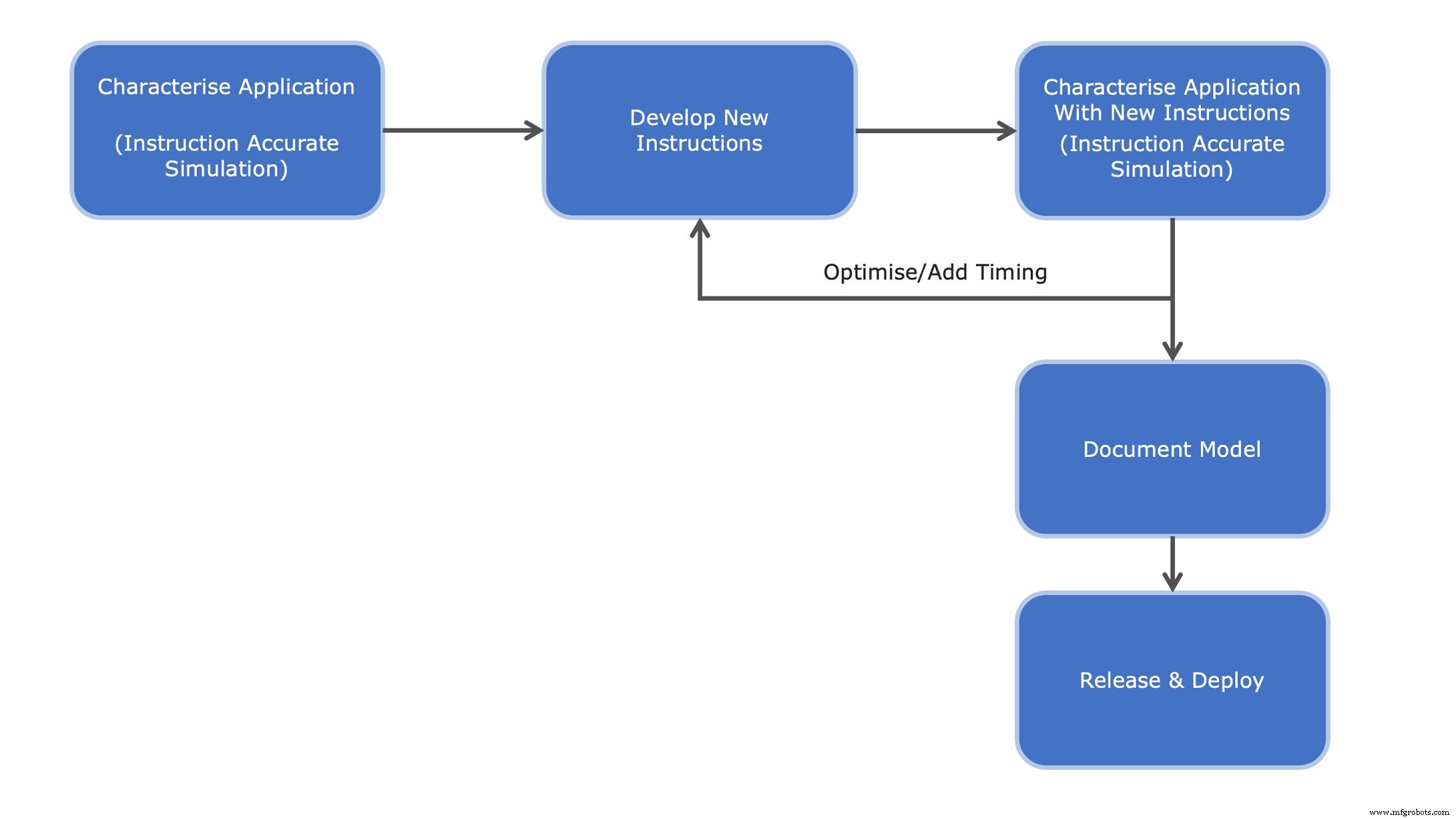

Een applicatie die is geschreven in C/C++ kan vervolgens worden gecompileerd met behulp van standaard tool chains. Dit kan op bare metal draaien of als onderdeel van een (realtime) besturingssysteem (RTOS/OS). De resulterende binaire code wordt vervolgens uitgevoerd met behulp van tools zoals een instructiesetsimulator (ISS) waarmee het gekozen basisprocessormodel kan worden geïntegreerd en gesimuleerd (figuur 1). Deze omgeving biedt ook standaard invoer-/uitvoerfunctionaliteit en toegang tot het hostbestandssysteem. Standaard tools voor een geïntegreerde ontwikkelomgeving (IDE), zoals Eclipse, kunnen vervolgens worden gebruikt om de uitvoering van code te regelen, via de GNU-debugger GDB.

Van hieruit worden via een proces van profilering en analyse instructiekandidaten geïdentificeerd, ontworpen en gemodelleerd. Door de originele applicatiecode als functioneel basismodel te gebruiken, kan de resulterende verbetering snel worden getest, geverifieerd en de prestaties worden vergeleken. Deze snelle iteratie van profilering en analyse zorgt voor een snelle selectie en optimalisatie van instructies die de moeite waard zijn om te implementeren. De documentatie kan vanuit het model worden gegenereerd en vormt de basis van een functiespecificatie voor het register-transfer logic (RTL) ontwerp en een geoptimaliseerd model.

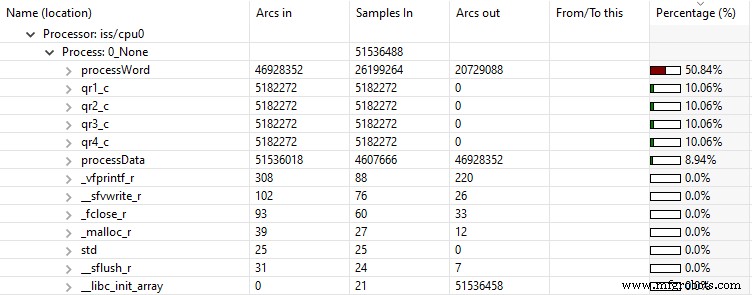

Een versleutelingsalgoritme zoals ChaCha20 kan bijvoorbeeld cruciaal zijn voor een bepaalde toepassing. Beschikbare broncode kan worden gecompileerd voor een "vanille" RV32IM-basis, uitgevoerd en vervolgens geanalyseerd met geschatte instructiecyclustiming met behulp van basisblokprofilering om te bepalen hoeveel tijd in welke secties van code is doorgebracht. De kern van het ChaCha20-algoritme maakt intensief gebruik van XOR- en rotatie-instructies die bekend staan als kwartrondes (figuur 2). De resultaten van blokprofilering laten meteen zien dat het grootste deel van de uitvoeringstijd aan deze functies wordt besteed.

Grafische visualisatie van deze hotspots kan ook worden gegenereerd met behulp van een tool voor verificatie, analyse en profilering (VAP). In plaats van een tekstuele output te leveren, wordt de uitvoeringstijd geleverd als een boom met opvouwbare statistieken, waardoor hotspots met een hoog percentage uitgevoerde instructies beter zichtbaar worden. Dit is te zien in figuur 3 waar de functie processWord() implementeert het ChaCha20-algoritme, waarbij op zijn beurt de vier qrx_c . worden aangeroepen functies om de vereiste kwartronde-functies te implementeren.

Door de door de compiler gegenereerde assembler-code te bekijken en/of door basisblokprofilering uit te voeren, is het dan mogelijk om te bepalen welke instructies en instructiecombinaties zijn gebruikt om het algoritme te implementeren. Vanaf hier is de volgende stap om te bepalen welke aangepaste instructies, binnen de grenzen van de specificaties van de ISA, de uitvoeringssnelheid mogelijk zouden kunnen verhogen.

Bepalen van de potentiële verbetering die RISC-V zou kunnen opleveren

Het ChaCha20-algoritme maakt intensief gebruik van een XOR in combinatie met een links-rotatie van 7, 8, 12 en 16 bits. Met behulp van de beschikbare instructies van de RV32IM-basisspecificatie blijkt dat dit een XOR-instructie vereist, gevolgd door een shift-left-instructie. Dit betekent dat er potentieel is om deze twee stappen te optimaliseren in vier speciale instructies die een XOR implementeren samen met 7, 8, 12 of 16 bits linksom draaien.

Omdat het een load-store-architectuur is, moeten alle aangepaste instructies ervan uitgaan dat de te manipuleren gegevens zich al in een van de 32-bits registers van deze RISC-V bevinden. Dit bepaalt onmiddellijk dat een R-type (register) instructie nodig zal zijn die kan worden gevonden in custom-1 decodeer ruimte (figuur 4).

De ISA geeft een duidelijke structuur voor dergelijke instructies. Door deze regels te volgen, kunnen we snel bepalen hoe we onze nieuwe instructies moeten coderen. De onderste 7-bits worden gedefinieerd als de opcode, waaraan een waarde is toegewezen die het markeert als een aangepaste instructie in de custom-1 decodeer ruimte. Dit is in tegenstelling tot de OP of OP-IMM opcodes die respectievelijk worden gebruikt voor de bestaande XOR- en shift-left-instructies.

De ISA geeft een duidelijke structuur voor dergelijke instructies. Door deze regels te volgen, kunnen we snel bepalen hoe we onze nieuwe instructies moeten coderen. De onderste 7-bits worden gedefinieerd als de opcode, waaraan een waarde is toegewezen die het markeert als een aangepaste instructie in de custom-1 decodeer ruimte. Dit is in tegenstelling tot de OP of OP-IMM opcodes die respectievelijk worden gebruikt voor de bestaande XOR- en shift-left-instructies.

In de ISA-definitie zijn drie vooraf gedefinieerde bitblokken gereserveerd voor het voorschrijven van de twee bronregisters en het bestemmingsregister voor het resultaat. Dit laat een blok met bits achter dat bekend staat als funct3 . Deze drie bits geven ons ruimte om acht mogelijke instructies te coderen, waarvan er vier in dit voorbeeld zullen worden gebruikt.

Zonder de gedetailleerde hardware-implementatie van de RTL voor deze instructies te vereisen, is het mogelijk om ze in de ISS-omgeving te simuleren om te zien of ze enig nut hebben voor de uitdaging die wordt aangegaan. De vier nieuwe instructies zijn gemodelleerd met behulp van de open virtual platforms (OVP) VMI application programming interface (API). Dit stelt de ontwikkelaar in staat om snel het ontwerp van de instructies te herhalen die het optimale gewenste resultaat opleveren op basis van de nieuwe instructies voor de doeltoepassing. Pas als dit is bereikt, is het nodig om middelen in te zetten voor een RTL-implementatie.

Voor een eerste functionele evaluatie van de instructies zijn er twee mogelijke benaderingen. De eerste is om de originele C/C++-versie van het algoritme aan te roepen en de nieuwe instructies aan deze functie te binden (figuur 5a). De tweede is om ze te implementeren als VMI morph-instructies die hetzelfde gedrag creëren (figuur 5b). Dit heeft het voordeel dat het efficiënter is en is de aanbevolen aanpak.

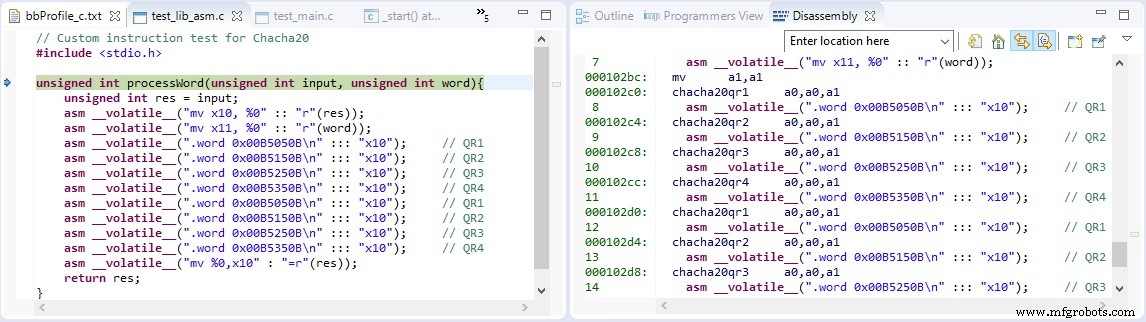

Het bestaan van nieuwe instructies betekent natuurlijk niet dat een compiler er meteen gebruik van kan maken. Daarom moet de originele C/C++-toepassing herschreven worden met inline assembler en gecrosscompileerd om gebruik te kunnen maken van de nieuwe instructies. Omdat het profileren en analyseren van kandidaat-instructies een iteratieve taak kan zijn, biedt de intrinsieke benadering de meest efficiënte manier om de oorspronkelijke C-toepassing aan te passen aan de nieuwe aangepaste instructies.

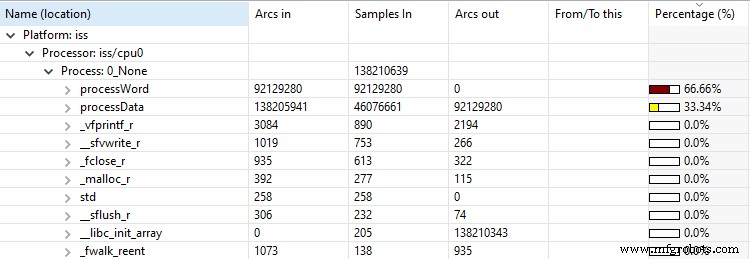

De RISC-V-basisimplementatie die in de simulator is geladen, moet ook op de hoogte worden gebracht van de nieuwe instructies om ervan te kunnen profiteren. Dit wordt bereikt door ze in het model op te nemen voordat de simulatie opnieuw wordt uitgevoerd. In dit specifieke voorbeeld betekent het herhalen van de profilering dat er in totaal minder tijd wordt besteed aan het uitvoeren van het algoritme (figuur 6). De Imperas VAP-profileringstool laat zien dat de processWord() functie, met behulp van de speciale inline-instructies, is nu goed voor 66% van de algehele uitvoering van het algoritme, maar de algehele uitvoeringstijd voor het algoritme wordt sterk verminderd (figuur 6b).

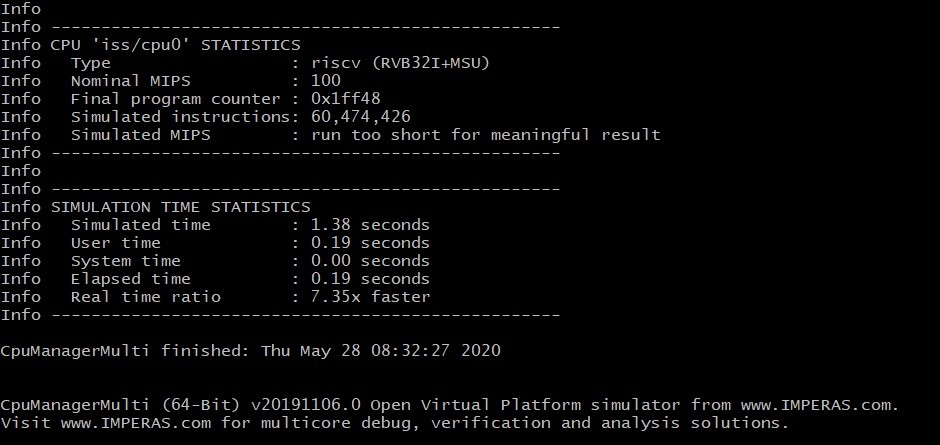

Resultaten met originele C-implementatie

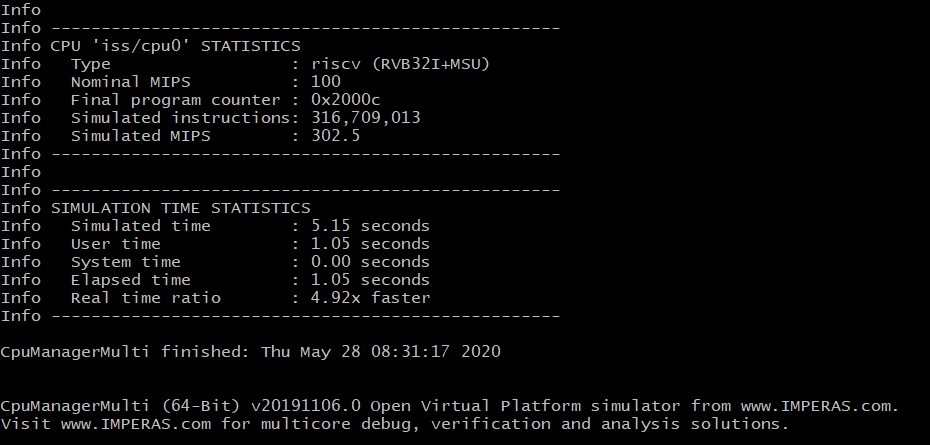

Info Gesimuleerde instructies:316.709.013

Info Gesimuleerde tijd :5,15 seconden

Resultaten met aangepaste instructies

Info Gesimuleerde instructies:60.474.426

Info Gesimuleerde tijd :1,38 seconden

Nadat de juiste functionaliteit is bepaald, wordt het model verder verfijnd door de uitvoeringstijd voor elke instructie in processorcycli aan te geven. Verdere simulatierondes kunnen vervolgens worden gebruikt om eventuele prestatieverbeteringen te bepalen, zelfs rekening houdend met wachtstatussen die verband houden met geheugentoegangen die kunnen optreden bij een eventuele hardware-implementatie.

Dankzij de nauwe integratie met gemeenschappelijke open source IDE's en GDB-tools, kan volledige debugging van de oplossing worden uitgevoerd in combinatie met het geoptimaliseerde RISC-V-ontwerp voordat het ontwerp wordt vastgelegd in een hardware-implementatie (afbeelding 7).

Van simulatie naar implementatie

Nu de mogelijke prestatieverbetering is bepaald, is de volgende stap het implementeren van de vier nieuwe instructies in RTL. Dankzij het uitgevoerde voorwerk wordt dit de functionele specificatie die de eisen definieert en kan ook worden gebruikt als onderdeel van het RTL-verificatietestplan als gouden referentiemodel. Hoewel het gebruik van intrinsieke functies in de C-toepassing de profilering en analyse van aangepaste instructies heeft geholpen, kan deze benadering ook worden gebruikt voor toekomstige ontwikkeling van productiecode of kan worden overwogen voor mogelijke verbeteringen in de toolketen van compilers.

De andere resterende essentiële taak, documentatie, is ook een eenvoudig proces. Alle snelle processormodellen van open virtuele platforms (OVP) bevatten documentatie die kan worden uitgebreid om de functionaliteit van wijzigingen en aanpassingen te dekken. Door het gegeven sjabloon te volgen, kunnen de nieuwe instructies worden gedeclareerd en beschreven, zodat de ontwikkelaarsgemeenschap hun mogelijkheden kan ontdekken en er gebruik van kan maken. De documentatie wordt vervolgens omgezet in een TeX-bestand waaruit een PDF kan worden gegenereerd (figuur 8).

Samenvatting

Met de vrijheden van de open ISA van RISC-V kunnen gebruikers, naast de standaardopties en functies die in de specificatie zijn gedefinieerd, verdere aangepaste uitbreidingen en instructies ontwikkelen. Op zijn eenvoudigst maakt het nieuwe en creatieve bedrijfsmodellen mogelijk, inclusief commerciële en open source-implementaties, plus een grotere vrijheid om functies met toegevoegde waarde te verkennen die verder gaan dan de reguliere traditionele benaderingen.

De echte waarde komt echter van het nemen van een volwaardige, gedocumenteerde en ondersteunde basiskern en deze aan te passen aan specifieke toepassingsbehoeften. Door zorgvuldige applicatie-analyse, profilering van code en simulatie kunnen aanzienlijke prestatieverbeteringen worden bereikt die niet konden worden gerealiseerd met vaste ISA's. Dit alles kan worden ontwikkeld en geprofileerd met echte applicatie-workloads voordat met de gedetailleerde hardware-implementatie wordt begonnen.

Ingebed

- Profilering van gedistribueerde applicaties met Perf

- Een korte handleiding voor 3D-printen met Binder Jetting

- Een gids voor 3D-printen met titanium

- Microchip:schaal ruimtetoepassingen met COTS-naar-straling-tolerante Core MCU's

- Renesas:RX72M MCU's met EtherCAT-ondersteuning voor industriële toepassingen

- Axiomtek:ingebed systeem met geïntegreerde laag 2 beheerde PoE-switch

- Opnieuw onderhandelen over kosten met bestaande leveranciers:een gids

- CNC-houtfrees - met verbluffende toepassingen

- Aan de slag met AI in verzekeringen:een inleidende gids

- 5 Real-World toepassingen van AI in de geneeskunde (met voorbeelden)

- Een gids voor aangepaste remschoenen en -blokken voor toepassingen op hogesnelheidstreinen