Robuust en Latch-Up-Immune LVTSCR-apparaat met een ingebouwde PMOSFET voor ESD-bescherming in een 28-nm CMOS-proces

Abstract

Laagspanningsgestuurde siliciumgestuurde gelijkrichter (LVTSCR) zal naar verwachting een elektrostatische ontlading (ESD) bescherming bieden voor een laagspannings-geïntegreerd circuit. Het is echter normaal gesproken kwetsbaar voor het latch-up-effect vanwege de extreem lage houdspanning. In dit artikel is een nieuwe LVTSCR ingebed met een extra p-type MOSFET genaamd EP-LVTSCR voorgesteld en geverifieerd in een 28-nm CMOS-technologie. Het voorgestelde apparaat heeft een lagere triggerspanning van ~ 6.2 V en een aanzienlijk hogere houdspanning van ~ 5.5 V met slechts 23% verslechtering van de storingsstroom onder de transmissielijnpulstest. Het is ook aangetoond dat de EP-LVTSCR werkt met een lagere inschakelweerstand van ~ 1.8 Ω en een betrouwbare lekstroom van ~ 1.8 nA gemeten bij 3,63 V, waardoor het geschikt is voor ESD-beveiliging in 2,5 V/3,3 V CMOS processen. Bovendien werden het activeringsmechanisme en de geleidingskenmerken van het voorgestelde apparaat onderzocht en gedemonstreerd met TCAD-simulatie.

Achtergrond

Met de continue miniaturisering van de kenmerken van halfgeleiderinrichtingen, is de schade veroorzaakt door elektrostatische ontlading (ESD) in de geïntegreerde schakelingen (IC) een ernstiger probleem geworden. Bovendien zijn de fabricagekosten van het ESD-beveiligingsapparaat sterk gestegen dankzij de geavanceerde procestechnologie [1]. Daarom zijn de ontwerpen van hoge oppervlakte-efficiëntie en robuustheid ESD-beveiligingsapparaten van grote waarde.

Er werd geverifieerd dat een siliciumgestuurde gelijkrichter (SCR) een hoge ESD-stroom ondersteunt met een kleine apparaatafmeting vanwege het sterk positieve feedbackeffect in zijn parasitaire bipolaire junctietransistors [2]. Maar de SCR heeft meestal een hoge triggerspanning (V t1 ) die de gate-oxide-doorslagspanning van de ingangstrap in CMOS-technologie op nanoschaal overschrijdt. De V . verkleinen t1 van SCR, werd de gewijzigde laterale SCR (MLSCR) gerapporteerd voor input-ESD-bescherming door zwaar gedoteerde n + in te voegen of p + gebieden over de grens van n-well en p-well [3, 4]. Maar de triggerspanning van de MLSCR is nog steeds groter dan de doorslagspanningen van uitgangstransistoren in de CMOS-uitgangsbuffer. Daarom kan het niet alleen een efficiënte output ESD-bescherming bieden.

Om de CMOS-uitgangsbuffer efficiënt te beschermen, is een low-voltage-triggered SCR (LVTSCR) voorgesteld door een kortkanaals NMOS (PMOS)-apparaat in de traditionele SCR te plaatsen om een veel lagere triggerspanning te realiseren [5,6,7] , wat gelijk is aan de snapback-triggerspanning van het geplaatste NMOS(PMOS)-apparaat. Echter, net als de traditionele SCR- en MLSCR-apparaten, heeft de LVTSCR ook te maken met de gevaren van latch-up vanwege de extreem lage houdspanning (Vh ) van ongeveer 2 V [8]. Een dergelijk vergrendelingseffect zal resulteren in een storing tijdens normaal bedrijf en een onophoudelijk hoge stroom om het IC [9] te vernietigen.

Er zijn verschillende mogelijke methoden om de V . te verbeteren u van de LVTSCR [10,11,12,13,14,15]. De meest gebruikelijke oplossing is om het basisgebied van de parasitaire bipolaire junctietransistoren (BJT) van de SCR uit te breiden om de injectie-efficiëntie van hun emitter-basisovergangen te verminderen [10]. Door deze oplossing te gebruiken, zal niet alleen het lay-outgebied van het apparaat toenemen, maar ook de inschakelweerstand (R aan ) ook, wat verder zal leiden tot een drastische verslechtering van de faalstroom (I t2 ). Vervolgens werd een geoptimaliseerde methode voorgesteld door een floating-n-well-regio in LVTSCR in te voegen met minder opoffering op I t2 [11], maar het werkt ook met een grote R aan leidt tot een exorbitante geleidingsspanning die de poortoxidedoorslagspanning overschrijdt tegen een kleine stroom, waardoor de effectieve ESD-beschermingsstroom wordt verminderd. De methode door de extra N-LDD/P-HALO-lagen in LVTSCR toe te voegen, kan ook de V verhogen u [12], terwijl dergelijke apparaten alleen compatibel zijn voor het specifieke proces en niet op grote schaal kunnen worden gebruikt in gewone CMOS-processen. Bovendien werd een gate-to-ground NMOS-getriggerde LVTSCR (GGSCR) gerapporteerd in [13], die de V verhoogt u door de afvoer van de ingebedde NMOS naar de anode te leiden, maar het kan ertoe leiden dat de ingebedde NMOS wordt beschadigd vóór de SCR-geleiding in een lage stroom. Onlangs hebben de samengestelde LVTSCR-structuren lage V t1 evenals hoge V u werden aangetoond in [14, 15]. Deze samengestelde structuren zijn ontworpen met een hoge complexiteit en gebiedsvereisten, waardoor hun toepassing in geavanceerde CMOS-technologie wordt beperkt gezien de ontwerpkosten. Daarom is een robuust, gebiedsefficiënt en tegen vergrendeling bestand tegen ESD-bescherming zeer wenselijk bij geavanceerde proces-ESD-bescherming.

In dit artikel wordt een nieuwe LVTSCR-structuur met een ingebouwde PMOS-transistor (EP-LVTSCR) voorgesteld voor voedingsspanningstoepassingen van 2,5 V/3,3 V. Het voorgestelde apparaat is vervaardigd in een 28-nm CMOS-proces en de elektrische eigenschappen ervan worden geverifieerd door de meting van de transmissielijnpuls (TLP). De natuurkundige mechanismen van het voorgestelde apparaat worden onderzocht door technologie-computer-aided design (TCAD)-simulaties. Als gevolg hiervan heeft de voorgestelde structuur een hogere houdspanning, een lagere triggerspanning met een lagere R aan , en slechts een lichte daling van I t2 zonder enige extra processtap.

Methoden

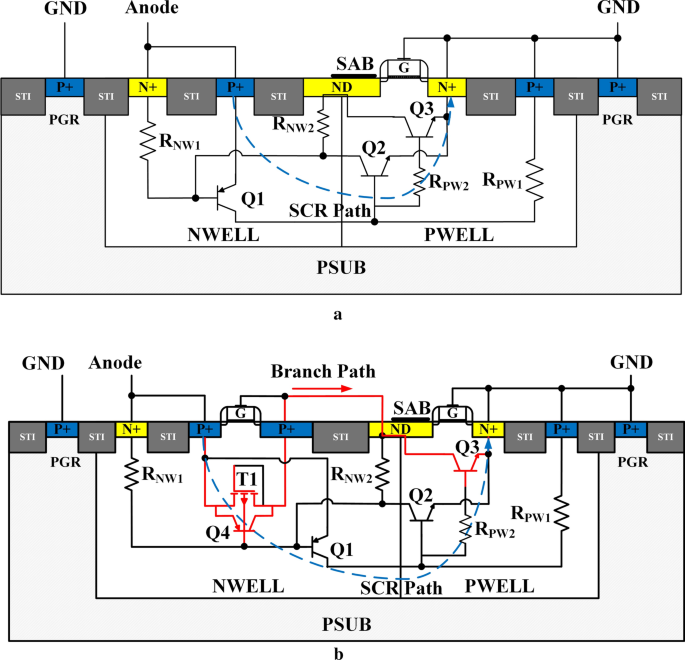

De conventionele LVTSCR en de voorgestelde EP-LVTSCR zijn in dit document bestudeerd. De schematische dwarsdoorsneden van de conventionele LVTSCR en EP-LVTSCR worden getoond in respectievelijk Fig. 1a, b, terwijl hun equivalente circuits worden weergegeven in de structuren met de parasitaire transistors en putweerstanden. In beide apparaten worden silicidebloklagen (SAB) bovenop het gedeeltelijke ND-gebied geplaatst, wat ballastweerstanden zal induceren door de vorming van silicidelagen te voorkomen [16, 17]. In conventionele LVTSCR wordt een NMOS-transistor in PWELL gestoken met zijn drain (ND) -instelling over NWELL en PWELL, terwijl de source en gate samen met aarde (GND) zijn verbonden, wat te zien is in figuur 1a. Tijdens ESD-stress zullen de parasitaire laterale pnp BJT (Q1) en de parasitaire laterale npn BJT's (Q2 en Q3) geleidelijk worden ingeschakeld. In een dergelijke toestand zijn de Q1- en Q2-transistoren gekoppeld om het SCR-geleidingspad te vormen dat de huidige ontlading zal overheersen, waarbij het SCR-geleidingspad wordt aangegeven door de stippellijn.

Dwarsdoorsnede van a de conventionele LVTSCR en b het voorgestelde EP-LVTSCR

Vergeleken met de conventionele LVTSCR heeft EP-LVTSCR een extra PMOS-transistor (T1) ingebed in de NWELL, aangezien de poort en afvoer zijn verbonden met ND met een metaal, zoals weergegeven in figuur 1b. Wanneer een ESD-puls wordt toegepast op de anode van de EP-LVTSCR, zal de spervoorspanning N+/NWELL/N+/PWELL/P+ diode eerst geleiden als de zapspanning hoger is dan de N+/PWELL doorslagspanning. Vervolgens zullen de gaten/elektronen die worden gegenereerd door het lawinevermenigvuldigingseffect naar de kathode/anode stromen, waardoor de stroomdichtheid in NWELL/PWELL toeneemt en de druppelpotentiaal over de NWELL/PWELL verder wordt verhoogd. Zodra de totale spanningsdaling op R NW1 en R NW2 , wat gelijk is aan de spanningsval tussen de source en gate (− V gs ) van T1 overschrijdt zijn drempelspanning (V de ) van ongeveer 0,9 V, wordt de T1 ingeschakeld. Vervolgens zullen de parasitaire laterale n-p-n-transistoren Q2 en Q3 worden getriggerd op basis van de geleiding van hun emitter-basisovergangen. Opgemerkt wordt dat het geleiden van T1 de R . zal verlagen aan over NWELL, en dus kunnen de Q2 en Q3 worden geactiveerd bij lagere spanningen. Naarmate de stroom blijft toenemen, neemt de spanningsval op R NW1 stijgt tot ongeveer 0,7 V en schakelt de Q1 en de parasitaire laterale p-n-p-transistor van de PMOS (Q4) in. Ten slotte wordt het SCR-pad ingeschakeld tegen het geleidende vertakkingspad.

Verschillende rapporten hebben aangetoond dat de houdspanning van SCR voornamelijk wordt bepaald door het potentiaalverschil over het NWELL/PWELL-depletiegebied V dep [18,19,20], wat omgekeerd evenredig is met de minderheidsdragers (elektronen/gaten) die in het uitputtingsgebied worden geïnjecteerd. Terwijl het vertakkingspad van EP-LVTSCR gaten/elektronen kan extraheren die in het uitputtingsgebied zijn geïnjecteerd uit het SCR-pad, waardoor de V wordt verhoogd u van EP-LVTSCR.

Om het fysica-mechanisme van EP-LVTSCR verder te demonstreren, is TCAD-simulatie uitgevoerd, waarbij de fysica-modellen zoals mobiliteit, recombinatie, thermodynamische en effectieve intrinsieke dichtheid werden geïntegreerd en de wiskundige methoden zoals extrapoleren, RelErrcontrol en gelijkstroom berekening werden gebruikt. De ESD-stroommodellering met 1,2 A-pulsen met een stijgtijd van 10 ns werd toegepast op respectievelijk de anoden van EP-LVTSCR en de conventionele LVTSCR, waarbij het substraat van de apparaten als het enige koellichaam werd beschouwd en de omgevingstemperatuur werd ingesteld op 300 K.

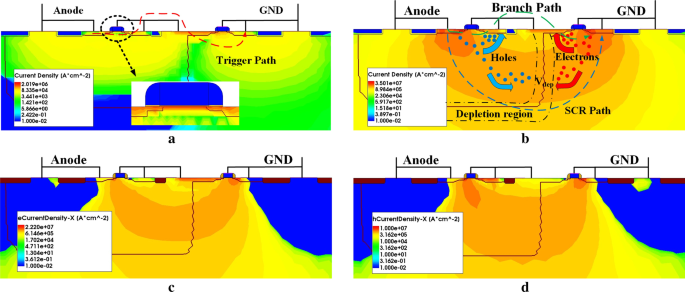

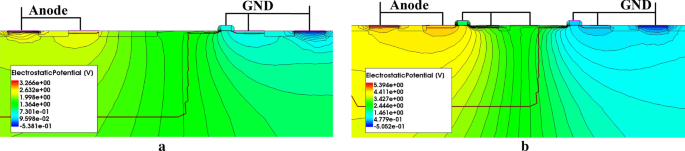

De gesimuleerde resultaten van de totale stroomdichtheidsverdelingen van EP-LVTSCR bij 500 ps en 5 ns worden respectievelijk getoond in Fig. 2a, b. Bij 500 ps concentreert de stroomdichtheidsverdeling zich op de T1- en de Q2-transistoren, wat aangeeft dat de serie T1/Q2 is ingeschakeld als een triggerpad zoals weergegeven in figuur 2a. Wanneer de tijd stijgt tot 5 ns, hebben zowel het SCR-pad als het vertakkingspad geleid, zoals te zien is in figuur 2b. Op dit moment wordt een deel van de gaten/elektronen gegenereerd door P+/N+ geëxtraheerd uit NWELL/PWELL om door het vertakkingspad te stromen, wat wordt geïllustreerd door de horizontale gaten en elektronenstroomdichtheid van de voorgestelde structuur getoond in Fig. 2c, d . Verder worden de elektrostatische potentiaalverdelingen van de conventionele LVTSCR en EP-LVTSCR bij 5 ns vergeleken in Fig. 3a, b. Het is duidelijk dat de potentiële piek binnen de EP-LVTSCR hoger is. Deze simulatieresultaten leveren direct bewijs voor de bovenstaande aanname dat de hogere houdspanning van EP-LVTSCR het gevolg is van het vertakkingspad aangegeven in figuur 1b.

TCAD-gesimuleerde a totale stroomdichtheidsverdeling bij t = 500 ps, b totale stroomdichtheidsverdeling bij 5 ns, c horizontale elektronenstroomdichtheidsverdeling bij 5 ns en d horizontale gaten stroomdichtheidsverdeling bij 5 ns van de voorgestelde EP-LVTSCR onder een 1.2A-TLP-spanning

TCAD-gesimuleerde elektrostatische potentiaalverdelingen van a het voorgestelde EP-LVTSCR en b de conventionele LVTSCR bij t = 5 ns onder een 1,2A-TLP-spanning

Resultaten en discussie

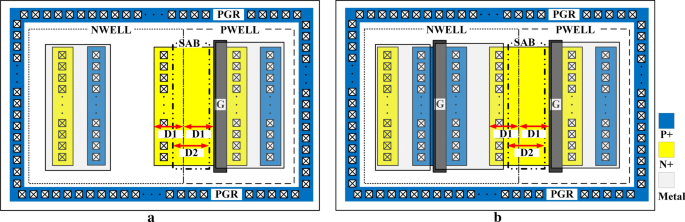

De conventionele LVTSCR en EP-LVTSCR zijn geïmplementeerd in een 28-nm 2,5 V/3,3 V logisch CMOS-proces met dezelfde breedte van 40 um, en hun lay-outtopologieën worden respectievelijk getoond in Fig. 4a, b. Om de parasitaire effecten geassocieerd met het substraat te vermijden, worden P-type beschermringen (PGR) gebruikt in beide structuren, en elke PGR is verbonden met GND [21]. De centrale as van ND is uitgelijnd met de NWELL/PWELL-junctie en de parameter D1 wordt gebruikt om de helft van de ND-lengte te beschrijven, terwijl D2 de lengte van het SAB-gebied is.

Lay-outtopologieën van a de conventionele LVTSCR en b het voorgestelde EP-LVTSCR

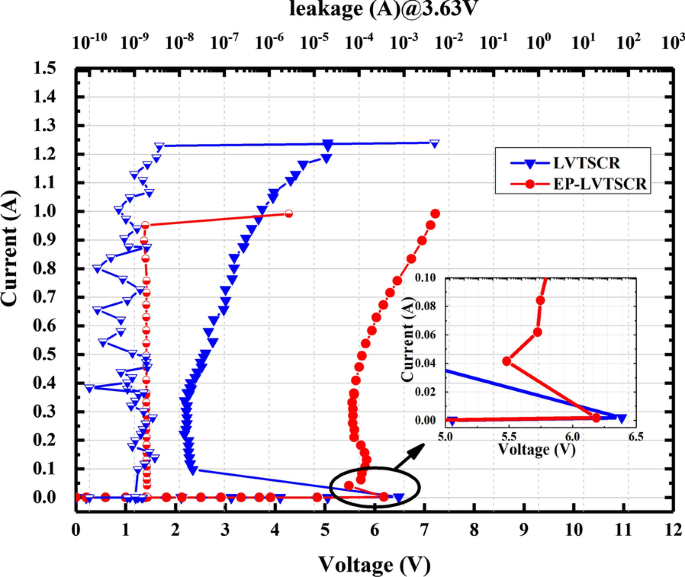

De ESD-kenmerken van de conventionele LVTSCR en EP-LVTSCR werden gemeten met behulp van Hanwa TED-T5000 TLP-tester met 10 ns stijgtijd en 100 ns pulsbreedte, en de lekstromen werden gemeten onder 3,63 V (1,1 * VDD) gelijkspanningsbias na elke TLP-stress. Gemeten TLP I–V en lekkagekenmerken van de EP-LVTSCR en LVTSCR worden getoond in Fig. 5. Blijkbaar heeft de EP-LVTSCR een hogere V u van 5,49 V vergeleken met de conventionele LVTSCR van 2,18 V. Hoewel de EP-LVTSCR een aanzienlijke verbetering heeft ten opzichte van de houdspanning, is de I t2 net afgenomen met ongeveer 0,29 A, wat profiteert van de assistent van het vertakkingsstroompad. Bovendien voert EP-LVTSCR ook een V . uit t1 afnemend van 6,49 tot 6,18 V. Voor 2,5 V of 3,3 V IO-pin in 28-nm CMOS-processen varieerde het ESD-ontwerpvenster van 3,63 tot 9,4 V met een veiligheidsmarge van 10%. Daarom kan de voorgestelde EP-LVTSCR worden gebruikt als een geldige ESD-beschermingsoplossing voor 2,5 V/3,3 V IO-poorten door het probleem van vastlopen in een traditionele LVTSCR-achtige structuur op te lossen.

Gemeten TLP I–V en lekstromen van EP-LVTSCR en de conventionele LVTSCR met hetzelfde matrijsoppervlak

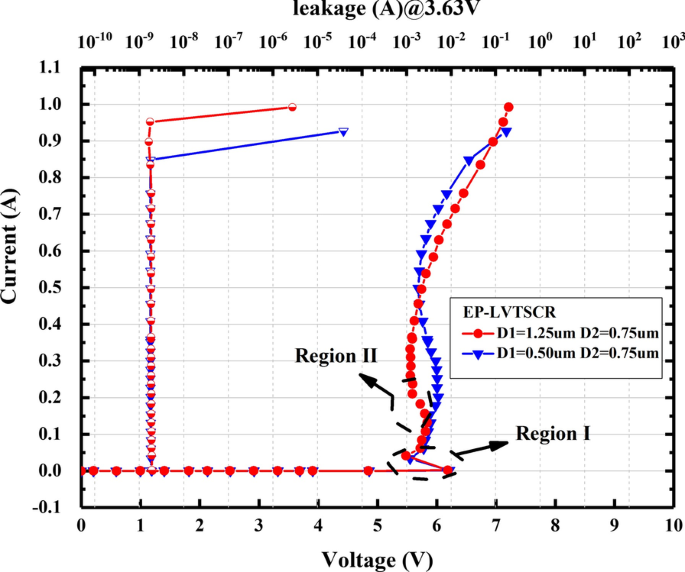

In dit artikel zijn de elektrische eigenschappen van de voorgestelde ESD-bescherming geoptimaliseerd door de ontwerpvariabelen D1 en D2 te wijzigen. Afbeelding 6 illustreert de TLP-meetresultaten van EP-LVTSCR's met twee verschillende D1. Opgemerkt wordt dat de I-V-curven van EP-LVTSCR's twee snapback-regio's vertonen vanwege de multi-triggering-effecten tijdens het inschakelen van de apparaten. Het eerste snapbackgebied I suggereert de geleiding van het triggerpad dat is aangegeven in figuur 2a, terwijl de tweede snapback van gebied II wordt veroorzaakt door het inschakelen van het SCR-pad. Wanneer D1 afneemt van 1,25 naar 0,5 um, wordt de I t2 neemt af met ongeveer 0,1 A en de houdstroom in de tweede snapback wordt verhoogd met ongeveer 0,17 A. Dit komt omdat de bronweerstanden R NW2 en R PW2 (Fig. 1) worden verminderd met de D1-vermindering, waardoor er meer stroom nodig is om de geleiding van SCR te activeren en in stand te houden.

Gemeten TLP I–V en lekstromen van EP-LVTSCR met twee verschillende D1

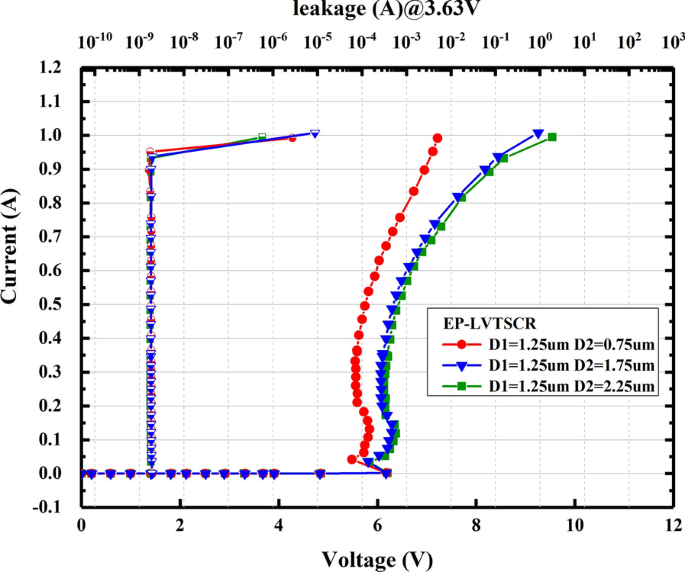

Afbeelding 7 toont de TLP I–V-resultaten van EP-LVTSCR met drie verschillende D2. Toen D2 toenam van 0,75 tot 2,25 µm, nam de ballastweerstand van ND geleidelijk toe, wat resulteerde in een toename van de weerstand van het vertakkingspad en verdere vergroting van R aan , die kan worden waargenomen door de hellingsvariaties van de IV-karakteristieken in Fig. 7. Als resultaat wordt de V u stijgt van 5,5 naar 5,8 V met de toename van D2 en zonder significante veranderingen in It2 .

Gemeten TLP I–V en lekstromen van EP-LVTSCR met drie verschillende D2

Conclusies

Een verbeterd ESD-apparaat genaamd EP-LVTSCR is ontworpen en gefabriceerd in een 28-nm CMOS-technologie. De mechanismen van de voorgestelde apparaten werden ook gedemonstreerd met TCAD-simulaties. Vergeleken met de conventionele LVTSCR heeft de voorgestelde EP-LVTSCR een lagere triggerspanning van 6,2 V en een aanzienlijk hogere houdspanning van 5,5 V vanwege het verbeterde triggermechanisme en het vertakkingsgeleidingseffect. Met zo'n hogere toename van V u , nam de faalstroom van de EP-LVTSCR slechts met ongeveer 20% af. Bovendien werkt de voorgestelde structuur met een lagere inschakelweerstand en een betrouwbare lekstroom van ongeveer 2 nA bij 3,63 V spanning, dus het is zeer geschikt voor het beschermen van 2,5 V/3,3 V I/O-pinnen. Bovendien wordt van de EP-LVTSCR's verwacht dat ze een ESD-bescherming bieden op 5 V-stroomcircuits met voordeel van hun instelbare houdspanningskarakteristieken.

Beschikbaarheid van gegevens en materialen

Alle gegevens die tijdens dit onderzoek zijn gegenereerd of geanalyseerd, zijn opgenomen in dit gepubliceerde artikel.

Afkortingen

- ESD:

-

Elektrostatische ontlading

- SCR:

-

Siliciumgestuurde gelijkrichter

- MLSCR:

-

Gewijzigde laterale SCR

- LVTSCR:

-

Laagspanning-getriggerde SCR

- CMOS:

-

Complementaire metaaloxide halfgeleider

- IC:

-

Geïntegreerde schakelingen

- V t1 :

-

Triggerspanning

- V u :

-

Houdspanning

- BJT:

-

Bipolaire junctietransistoren

- R aan :

-

Inschakelweerstand

- Ik t2 :

-

Storingsstroom

- TLP:

-

Transmissielijnpuls

- TCAD:

-

Technologie computerondersteund ontwerp

- SAB:

-

Silicide blok

- V de :

-

Drempelspanning

- DC:

-

Gelijkstroom

Nanomaterialen

- Een kort overzicht van IC-technologie voor microcontrollers en ingebedde systemen

- Maxim:dubbele IO-Link-transceiver met DC-DC-regelaar en overspanningsbeveiliging

- Ingesloten ontwerp met FPGA's:ontwikkelingsproces

- TRS-STAR:robuuste en ventilatorloze embedded systemen van avalu

- Dip-coating procestechniek en prestatie-optimalisatie voor drie-staten elektrochrome apparaten

- Een RRAM-geïntegreerde 4T SRAM met zelfremmende resistieve schakelbelasting door puur CMOS logisch proces

- Een nieuwe nanocone-clustermicrostructuur met antireflectie en superhydrofobe eigenschappen voor fotovoltaïsche apparaten

- Multifunctioneel apparaat met schakelbare functies voor absorptie en polarisatieconversie op Terahertz-bereik

- Atomic Layer-Deposited HfAlOx-Based RRAM met lage bedrijfsspanning voor computertoepassingen in het geheugen

- Automatisering en cyberbeveiliging:volledige bescherming voor klanten

- PCB-materialen en ontwerp voor hoogspanning