Multi-Layer SnSe Nanoflake Field-Effect Transistors met Au Ohmic-contacten met lage weerstand

Abstract

We rapporteren p-type tinmonoselenide (SnSe) eenkristallen, gekweekt in dubbel afgesloten kwartsampullen met behulp van een gemodificeerde Bridgman-techniek bij 920 ° C. Röntgenpoederdiffractie (XRD) en energiedispersieve röntgenspectroscopie (EDX) metingen bevestigen duidelijk dat het gegroeide SnSe bestaat uit monokristallijn SnSe. Elektrisch transport van meerlaagse SnSe-nanoflakes, die werden bereid door afschilfering van bulk-eenkristallen, werd uitgevoerd met behulp van back-gated veldeffecttransistor (FET) -structuren met Au- en Ti-contacten op SiO2 /Si-substraten, waaruit blijkt dat meerlagige SnSe-nanovlokken p-type halfgeleiderkenmerken vertonen vanwege de Sn-vacatures op de oppervlakken van SnSe-nanovlokken. Bovendien werd een sterk dragerscreeningseffect waargenomen in 70-90 nm dikke SnSe-nanoflake-FET's. Verder wordt het effect van de metalen contacten op meerlaagse SnSe-nanoflake-gebaseerde FET's ook besproken met twee verschillende metalen, zoals Ti/Au- en Au-contacten.

Achtergrond

Transiënte metaalchalcogeniden bieden een reeks optische bandgaps, waardoor deze materialen geschikt zijn voor gebruik in verschillende optische en opto-elektronische toepassingen [1]. Dunne films van deze materialen, waaronder PbTe, PbSe en Bi2 Se3 [2], hebben veel aandacht getrokken vanwege hun toekomstige gebruik in infrarood opto-elektronische apparaten, stralingsdetectoren, zonnecellen, geheugenapparaten en holografische opnameapparaten [3,4,5,6,7,8]. Tin mono en diseleniden (SnSe en SnSe2 ) stonden in de schijnwerpers van onderzoek vanwege hun hoge absorptiecoëfficiënten, wat gunstig is voor opto-elektronische toepassingen. Bovendien zijn deze materialen veelbelovend voor gebruik in thermo-elektrische toepassingen [9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24]. Tinmonoselenide (SnSe) is een p-type halfgeleider met een bandgap voor indirecte toegestane overgangen dicht bij ~0,9 eV en die voor direct toegestane overgangen dicht bij ~1,2 eV, terwijl tindiselenide (SnSe2 ) is een n-type halfgeleider [6]. De kristalstructuur van SnSe is orthorhombisch en de eenheidscelparameters zijn a = 11.496 Å, b = 4.151 Å, en c = 4.444; deze orthorhombische structuur transformeert in een tetragonale structuur bij hoge temperatuur die niettemin lager is dan het smeltpunt van SnSe2 [25].

Onlangs zijn op Sn gebaseerde binaire chalcogenide en dichalcogenide elektrische apparaten, waaronder veldeffecttransistoren (FET's) met een gemeenschappelijke achterpoort met een groot oppervlak, uitgebreid onderzocht. Er is met name veel vooruitgang geboekt bij het karakteriseren van op Sn dichalcogenide gebaseerde FET's [26, 27]. In 2016, Pei et al. rapporteerde een paar lagen SnSe2 FET, met een hoge aan/uit-verhouding van ~10 4 met een top afdeklaag van een polymeer elektrolyt [27]. Guo et al. rapporteerde ook een SnSe2 . met enkele lagen met hoge mobiliteit FET met een dikte van ~8,6 nm [28]. Uit eerdere werken werd bevestigd dat dunne SnSe-films met een lage dragerconcentratie een hoge mobiliteit en stroom aan/uit-verhouding van SnSe2 opleveren FET's. Ondanks deze inspanningen bij het gebruik van SnSe2 elektrische karakterisering van SnSe FET's, bereid door afschilfering van enkele kristallen, is echter niet gerapporteerd. Een gedetailleerde karakterisering van elektrisch transport in enkele en meerlaagse SnSe2 vlokken moeten worden uitgevoerd voor het beoordelen van de elektrische transporteigenschappen van tinchalcogeniden, zoals SnSe-nanoflakes, omdat wordt verwacht dat afzonderlijke SnSe-kristallen een hoge dragermobiliteit van ~7835 cm 2 vertonen /V s [29].

In dit werk hebben we enkelkristallijn SnSe gekarakteriseerd dat is gegroeid met behulp van een gemodificeerde Bridgman-methode. Elektrisch transport in meerlaagse SnSe-nanoflake-FET's bereid door afschilfering van bulk-eenkristallen werd voor het eerst gekarakteriseerd met behulp van back-gated FET-structuren op SiO2 /Si-substraten. Verder werd het effect van metalen contacten op meerlaagse SnSe-nanoflake-gebaseerde FET's ook bestudeerd voor twee verschillende soorten contacten (Ti/Au en Au) omdat de werkfunctie van het contactmetaal de geleiding van gatendragers door de Schottky-barrière aan de metal-SnSe nanoflake-interface.

Methoden

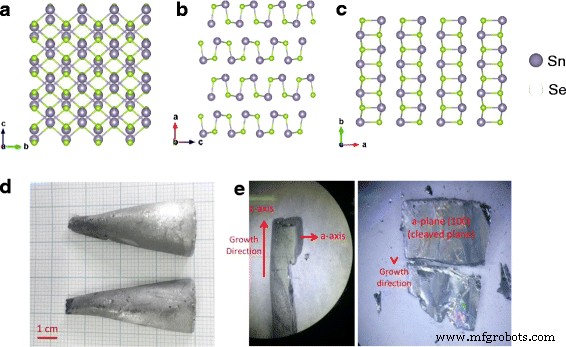

SnSe heeft een gelaagde orthorhombische kristalstructuur bij kamertemperatuur [24]. Afbeelding 1a–c toont de perspectiefaanzichten van de SnSe-kristalstructuur langs de a , b , en c axiale richtingen. Zoals weergegeven in figuur 1c, zijn SnSe-platen met een laag met twee atomen gegroefd, terwijl gemakkelijke splitsing in de kristallen plaatsvindt langs het (100) vlak (figuur 1b). Enkele SnSe-kristallen werden gekweekt met behulp van de gemodificeerde Bridgman-methode, zoals eerder beschreven [24, 30]. Stoichiometrische hoeveelheden Sn (99,999% shot, Alfa Aesar) en Se (99,999% poeder, Alfa Aesar) werden eerst gesmolten tot een staaf (~ 20 g) in een dubbel afgesloten kwartsampul. De grondstoffen werden langzaam verwarmd tot 500 ° C en bleven 10 uur staan, daarna nog 10 uur op 920 ° C gehouden voordat de oven werd uitgeschakeld. De verkregen staaf werd tot poeder vermalen en in een kegelvormige kwartsbuis gevuld, geëvacueerd en met een vlam afgesloten. Deze geladen kegelvormige kwartsbuis werd in een grotere kwartsbuis geplaatst. De buitenste buis werd gevuld met gasvormig Ar om explosie en oxidatie te voorkomen, en vervolgens vlamverzegeld. De geladen kwartsampul werd geplaatst op de plaats waar de temperatuurgradiënt het grootst was in de verticale buisoven. De verticale buisoven werd langzaam 20 uur verwarmd tot 970 ° C, 10 uur vastgehouden en vervolgens afgekoeld tot 830 ° C met een snelheid van 0,5 ° C / uur. De oven werd nog 24 uur op 830 °C gehouden en vervolgens afgekoeld tot 500 °C met een snelheid van 100 °C/u voordat de oven werd uitgeschakeld.

een –c Kristalstructuur van SnSe-kristallen langs a -, b -, en c -axiale richtingen. d Foto van een volwassen monokristallijn SnSe. e Foto's van gespleten SnSe-kristallen langs de a -as (100) vlak. Bovenaanzichten van het gespleten vlak (100) van het SnSe-eenkristal (rechter afbeelding in d )

Resultaten en discussie

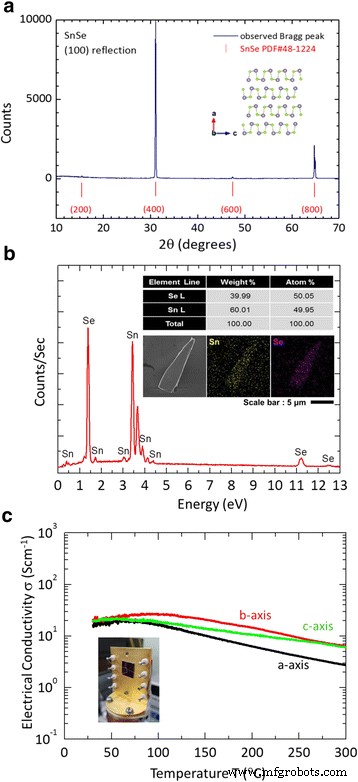

Een kegelvormig SnSe-kristal (diameter, 30 mm; lengte, 70 mm) werd verkregen en wordt getoond in Fig. 1d-e. Het verkregen kristal werd in twee stukken verdeeld vanwege een scheur die optrad tijdens de extractie van het kristal uit de kwartsampul (figuur 1d). De kwaliteit van de gegroeide SnSe-kristallen werd gecontroleerd met behulp van een poederröntgendiffractometer (XRD, New D8-Advance, Bruker-AXS, Duitsland) met Cu Kα (λ = 1.5406 ). Afbeelding 2a toont het XRD-patroon van het vermogensdiffractiebestand (PDF) 48–1224 voor orthorhombische SnSe, samen met het patroon voor de kristallografische a as, die loodrecht staat op het gespleten vlak (100) van het SnSe-kristal. Zoals getoond in Fig. 2a, suggereert het XRD-patroon van enkelkristallijn SnSe sterk een enkelfasig orthorhombisch kristal met een ruimtegroep Pnma [31], wat wijst op een sterke voorkeursoriëntatie met (h00) reflecties, wat goed overeenkomt met een eerder rapport [32]. Bovendien waren de overheersende pieken (400) en (800), bij 2θ = 31,081° en 64.818°, respectievelijk, zoals weergegeven in Fig. 2a [33]. Zoals weergegeven in figuur 2b, onthulde energiedispersieve röntgenspectroscopie (EDX) de Sn:Se-atoomverhouding van 1:1, wat de stoichiometrische verhouding van Sn en Se bevestigt (inzet van figuur 2b). Insets van Fig. 2b tonen ook een scanning elektronenmicroscopie (SEM) afbeelding en EDX-mapping van een SnSe nanoflake FET met een apparaatdikte van 90 nm. Dit resultaat komt goed overeen met eerdere rapporten [24, 33]. Bovendien werd de elektrische geleidbaarheid van enkelkristallijn SnSe (inzet van figuur 2b) gemeten voor temperaturen van 30-300 K, met behulp van de conventionele vierpuntsprobe-methode. Figuur 2c toont de temperatuurafhankelijke elektrische geleidbaarheid van SnSe-eenkristallen langs drie verschillende kristallografische richtingen, wat wijst op vergelijkbaar temperatuurafhankelijk gedrag en anisotropiegedrag als gevolg van verschillende gatenmobiliteiten in SnSe langs de verschillende axiale richtingen. Zoals weergegeven in Fig. 2c, is de elektrische geleidbaarheid langs de b - en c -as bij 300 K is vastgesteld op ~6.00 S cm −1 , wat ~2,2 keer groter is dan die voor de a -as (~ 2,7 S cm −1 ). Dit resultaat komt goed overeen met eerdere resultaten voor monokristallijn SnSe [24]. In figuur 2c wordt de temperatuurafhankelijke elektrische geleidbaarheid van enkelkristallijn SnSe getoond voor het halfgeleiderbereik (30-100 K) en voor het metallische bereik (> 100-300 K). Boven 100 K vertoonden de gegroeide SnSe-kristallen een metaaltransportgedrag, in overeenstemming met eerdere waarnemingen [24].

een XRD-patroon van SnSe-eenkristallen, met een duidelijke (h00) diffractie. b EDX-spectrum van de SnSe-eenkristallen. Inzet toont de gedetailleerde informatie over de atomaire verhouding van Sn en Se. Inzetstukken vertonen een SEM-afbeelding en EDX-mapping van een SnSe-nanoflake-FET met een apparaatdikte van 90 nm. c Temperatuurafhankelijke elektrische geleidbaarheid van de SnSe-eenkristallen, voor temperaturen van 30-300 K, gemeten met de vierpuntsprobe-methode

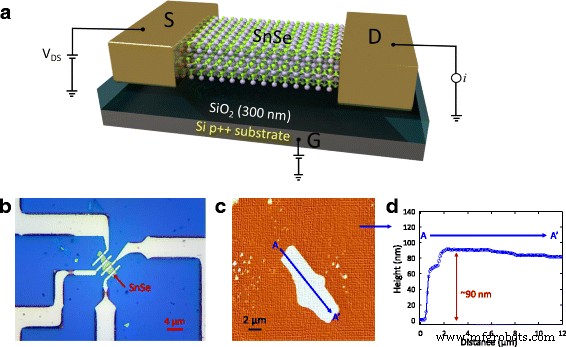

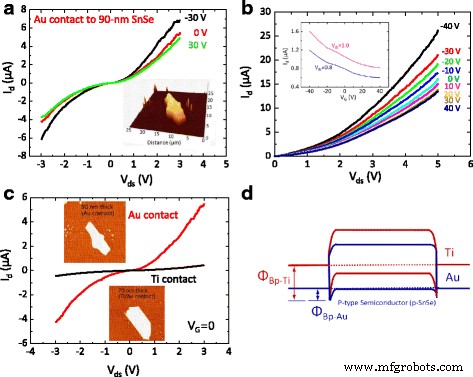

SnSe FET-apparaten werden als volgt gefabriceerd. Eerst werden SnSe-nanovlokken mechanisch geëxfolieerd op een 300 nm dikke SiO2 /p ++ Si-substraat van enkele SnSe-kristallen, gemakkelijk te splitsen in het (100) vlak met behulp van de bekende plakbandmethode (Fig. 1e) [26, 27, 34]. Metingen van elektrisch transport in als voorbereide individuele SnSe-nanoflakes-FET's werden uitgevoerd bij kamertemperatuur in de back-gated FET's-configuratie. Figuur 3a toont schematisch op SnSe nanoflake gebaseerde FET-apparaten met een achterpoort met een groot oppervlak. In deze studie werden twee SnSe-nanoflakes (70- en 90-nm dikke SnSe-nanoflakes) bereid op de SiO2 /Si-substraat. De SnSe-FET's werden vervaardigd met behulp van de standaard elektronenstraallithografiemethode gevolgd door twee soorten metallisatie, namelijk Au (dikte, 100 nm) en Ti/Au (dikte, 10/100 nm) werden beschouwd als ohmse contacten op SnSe-nanoflakes. Vóór het metallisatieproces werd gebufferd oxide-etsen (BOE) uitgevoerd om de polymeer- en oxideresten op de oppervlakken van de nanovlokken te verwijderen. Figuur 3b toont een optisch beeld van een SnSe-nanoflake-FET met een apparaatdikte van 90 nm. De dikten van de SnSe-nanovlokken werden gemeten met behulp van een atomaire krachtmicroscoop (AFM) bij kamertemperatuur (figuur 3c-d). Zoals getoond in Fig. 3b en inzet van Fig. 2b, had de gefabriceerde 90 nm dikke SnSe FET de kanaallengte (L ) van 5 μm en breedte (B ) van 4,71 μm, terwijl voor de 70 nm dikke SnSe FET L was 5 μm en W was 6 urn. Alle stroom-spanning (I -V ) kenmerken werden gemeten met behulp van een halfgeleiderparameteranalysator (HP 4155C, Agilent Technologies, VS) op een elektrisch afgeschermd sondestation bij kamertemperatuur. Afbeelding 4a toont de afvoerstroom (I d ) als functie van de poortspanning (V g ), voor de 90 nm dikke SnSe-nanoflake, voor de source-drain-spanningen (V ds ) van -30, 0 en 30 V, bij kamertemperatuur, wat wijst op een duidelijk p-type halfgeleidergedrag, dat voornamelijk wordt toegeschreven aan de Sn-vacatures, zoals eerder gerapporteerd [15, 16, 22, 24, 35,36,37 ,38,39]. Het resultaat in figuur 4a houdt in dat metallische AU met zijn hoge werkfunctie naar verwachting zwakke ohmse contacten vormt op SnSe-nanovlokken, wat wijst op een lagere Schottky-barrière voor de geleidingsband van SnSe-nanovlokken. Een meer gedetailleerde bespreking, voor werkfuncties van verschillende metalen, zal later worden gegeven. Afbeelding 4b toont I d vs. V ds voor verschillende V g , variërend van −40–40 V, in stappen van 10 V. Uit figuur 4b, de mobiliteit van de gaten (μ p ) is vastgesteld op ~2,7 cm 2 /V s, verkregen van μ p = t m [L ⁄ (WC os V ds)], waar t m is de trans-conductantie (=dI d /dV g = 2.89 × 10 − 8 A /V ), L is de lengte (~5,1 μm), W is de breedte (~4,75 μm), V ds is de drain-source spanning (~1 V) van de SnSe FET, en C os (=ε r ε 0 /d = 11.5 nF/cm 2 ) met ε r (de diëlektrische constante) van 3,9 en d (de dikte van de oxidelaag) van 300 nm is de capaciteit per oppervlakte-eenheid van de back-gated SnSe nanoflake FET. De geëvalueerde mobiliteit van de gaten van de mechanisch geëxfolieerde SnSe-nanoflake-FET's is veel kleiner dan die van dunne epitaxiale SnSe-films (~60 cm 2 /V s) bereid door gepulseerde laserdepositie op MgO-substraten met behulp van Se-rijke doelen [40]. De hier verkregen waarde is echter ~1,8 keer groter dan die verkregen voor monokristallijne SnSe-nanoplaten (~1,5 cm 2 /V s) [33]. Zo'n relatief lage gatenmobiliteit kan worden toegeschreven aan een sterke fononverstrooiing als gevolg van de Sn-vacatures op het SnSe-oppervlak [18, 36, 41, 42] en een relatief hoge Schottky-barrière op het Au-metaal-SnSe-nanoflake-interface.

een Schema van een mechanisch geëxfolieerde SnSe nanoflake FET op een SiO2 /p ++ Si substraat. b Optisch beeld van een gefabriceerde SnSe nanoflake FET die werd gebruikt voor metingen van elektrisch transport. c AFM-beeld van een SnSe-nanoflake op een SiO2 /Si-substraat. d AFM-hoogteprofiel van een SnSe-nanoflake, voor het schatten van de dikte van en het fabriceren van FET-apparaten

een Afvoerstroom (I d ) als functie van de aangelegde source-drain-spanning (V ds ), voor de poortspanningen (V g ) van -30, 0 en 30 V, voor een 90 nm dikke SnSe nanoflake FET, bij kamertemperatuur. b Ik d vs. V ds voor V g variërend van -40-40 V in stappen van 10 V, voor de 90 nm dikke SnSe nanoflake FET. De inzet laat Ik . zien d vs. V g voor V ds van 0,8 en 1,0 V, gemeten bij kamertemperatuur. c Ik d vs. V ds zonder vooringenomenheid V g (=0) voor Au- en Ti-contacten op een SnSe-nanoflake-FET. De inzet toont een AFM-gescande afbeelding van SnSe-nanovlokken. d Schema's van de energiebanddiagrammen van twee metalen, Au en Ti, op p-type SnSe-halfgeleiders

Bovendien hebben we een zwakke gate-afstemming van geleiding waargenomen in het uitputtingsgebied van de I d vs. V ds curve (Fig. 4c) en een lage stroom aan/uit-verhouding (~2 bij V ds van 1 V, inzetstukken van Fig. 4c) in de p-SnSe nanoflake FET met Au-metalen contacten. Een soortgelijk gedrag werd gerapporteerd voor andere tweedimensionale (2D) halfgeleidende materialen met een vergelijkbare dikte, waaronder SnS FET's (dikte, ~50-80 nm) [43], ~15,8-nm dikke SnSe-nanoplaten [33], ~80 -nm-dikke MoS2 [44] en ~84 nm dikke SnSe2 [26]. Dit gedrag kan worden verklaard door het eindige dragerafschermingslengte-effect vanwege het bestaan van een oppervlakkige geleidende oppervlaktelaag in FET-apparaten met een dikte groter dan de afschermlengte \( \left(\sqrt{\varepsilon {K}_B T}{e }^2 p\right) \), waarbij ε , K B , en p zijn respectievelijk de diëlektrische constante van de halfgeleider, de constante van Boltzmann en de dichtheid van de gatendrager [43].

Metalen contacten bepalen in belangrijke mate de kenmerken van 2D FET-apparaten [45]. Om het effect van de werkfuncties van metaal op SnSe te bepalen, beschouwden we Au (werkfunctie, ~ 5,1 eV) en Ti (werkfunctie, ~ 4,3 eV) als metalen contacten op SnSe-nanoflakes. Afbeelding 4c toont typische I d vs. V ds curven zonder poortmodulatie (V g = 0) voor SnSe nanoflake-FET's met Au- en Ti-contacten, wat wijst op een hogere algehele weerstand voor Ti (~ 15,4 MΩ) vergeleken met die voor Au (~ 0,56 MΩ). De Schottky-barrière op de metaal-SnSe-interface is dus hoger voor Ti (figuur 4c). Dit gedrag wordt altijd waargenomen op alle SnSe FET met Ti-contacten. Zoals weergegeven in figuur 4d, neemt de hoogte van de Schottky-barrière voor gaten toe naarmate de werkfunctie van het metaal afneemt. Zo kunnen metalen zoals Pd, Au en Pt, met grote werkfuncties, geschikt zijn als ohmse contacten op p-SnSe nanoflake FET's omdat voor deze metalen de hoogte van de Schottky-barrière voor injectie van gaten lager zal zijn. De contactweerstand moet worden gemeten voor extra metalen om hun geschiktheid als metalen contacten op SnSe-nanoflake te bepalen. Dit probleem wordt momenteel verholpen met behulp van de methode voor de lengte van de overdracht.

Conclusies

Samenvattend werden meerlagige SnSe-nanovlokken gekweekt, geëxfolieerd en gekarakteriseerd voor SnSe FET-kanalen met een back-gated FET-structuur op SiO2 /Si-substraten. Elektrische transportmetingen toonden aan dat meerlaagse SnSe-nanoflakes met Au-metaalcontacten p-type halfgeleiderkenmerken vertonen met een relatief lage Schottky-barrière en lage contactweerstand op geëxfolieerde SnSe nanoflake-FET's. Bovendien benadrukken we dat deze studie de eerste is die mechanisch geëxfolieerde SnSe-nanoflake-gebaseerde FET's rapporteert en we zijn ervan overtuigd dat onze SnSe-nanoflake-FET's veelbelovend zijn voor 2D-elektrische apparaten en voor toepassingen voor het oogsten van energie, inclusief toekomstige generatie van thermo-elektriciteit .

Nanomaterialen

- Transistors, junction field-effect (JFET)

- Transistors, Insulated-gate Field-effect (IGFET of MOSFET)

- Junction Field-effect Transistors

- Insulated-gate Field-effect Transistors (MOSFET)

- Inleiding tot Junction Field-effect Transistors (JFET)

- Inleiding tot veldeffecttransistoren met geïsoleerde poort

- Air spacers voor 10nm chips

- Een nanometersprong naar biljoenen transistors

- Onbewaakt leren met kunstmatige neuronen

- Effect van in situ gloeibehandeling op de mobiliteit en morfologie van op TIPS pentaceen gebaseerde organische veldeffecttransistoren

- Depositie in twee stappen van met Al-gedoteerde ZnO op p-GaN om ohmse contacten te vormen