Hybride architectuur versnelt AI, vision-workloads

Quadric, een startup in Silicon Valley, heeft een versneller gebouwd die is ontworpen om zowel AI als standaard computervisie-algoritme-workloads voor edge-apparaten zoals robots, fabrieksautomatisering en medische beeldvorming te versnellen. De hardware-architectuur van het bedrijf is een nieuwe hybride datastroom en Von Neumann-ontwerp dat workloads aankan, waaronder neurale netwerken, machine learning, computervisie, DSP en elementaire lineaire algebra-subprogramma's.

"Vanaf het begin waren we ons er terdege van bewust dat AI niet de enige applicatie is die nodig is voor on-device computing op edge-apparaten", vertelde Quadric's CEO Veerbhan Kheterpal aan EE Times . “De ontwikkelaars van deze producten hebben het volledige systeem nodig om klassieke high-performance computeralgoritmen te kunnen gebruiken, samen met AI. Dat zijn echt de volledige systeemvereisten.”

Kheterpal benadrukte dat de architectuur geen verzameling versnellers is voor individuele workloads. Het is eerder een uniforme architectuur met een dataparallelle instructieset die is ontworpen om verschillende workloads te versnellen, inclusief AI-inferentie.

"Waar AI de laatste tijd in beweging is, zijn er enkele interessante trends rond het vervangen van hele lagen door een snelle fouriertransformatie (FFT)", zegt Daniel Firu, Chief Product Officer van Quadric. Quadric positioneert zichzelf om dat soort werklasten te versnellen, daarbij verwijzend naar een recent artikel van Google waarin onderzoekers een transformatornetwerk versnelden door enkele lagen te vervangen door een FFT. Google verving de zelfaandachtssublaag van een transformer-encoder door een FFT om een netwerk te genereren dat een nauwkeurigheid van 92 procent behaalde op de BERT-benchmark; training was tot zeven keer sneller op GPU's of twee keer zo snel op Google TPU's.

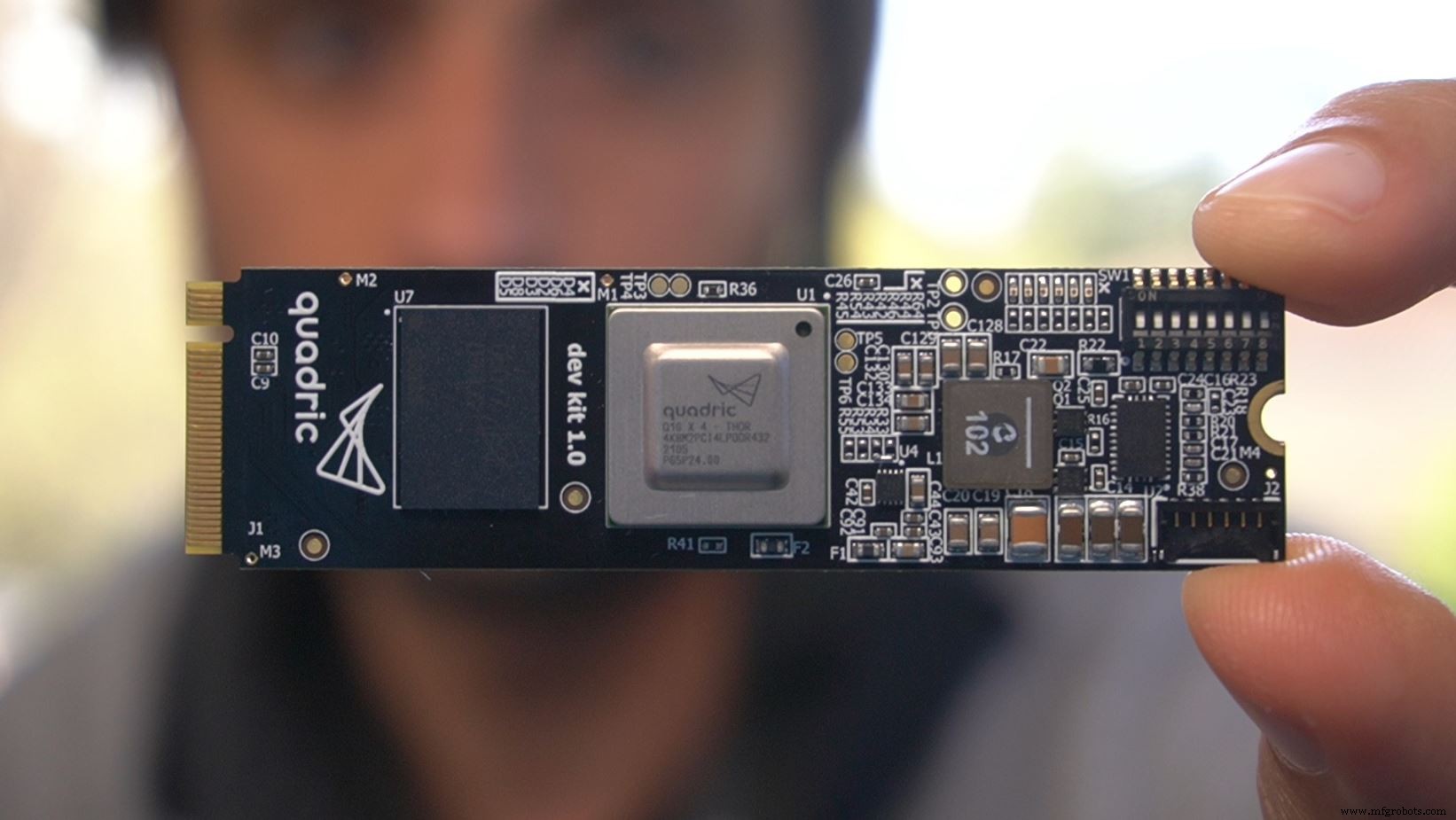

Quadric's developer kit, een M.2-kaart met de Q16-processor en 4 GB extern geheugen (Bron:Quadric)

Wijngaardrobots

De drie mede-oprichters van Quadric, Veerbhan Kheterpal, Daniel Firu en Nigel Drego, hebben eerder 21 opgericht, een bitcoin-mijnbedrijf dat werd verkocht aan Coinbase. Quadric, Burlingame, Californië, begon niet met het ontwerpen van chips. In plaats daarvan bouwde het oorspronkelijk landbouwrobots die de wijngaarden van Napa Valley op en neer konden lopen, naar de wijnstokken konden kijken en waarschuwingen konden sturen wanneer het irrigatielekken of ongedierte zag.

Veerbhan Kheterpal (Bron:Quadric)

"Toen we het aan het bouwen waren, realiseerden we ons dat het geen levensvatbaar product zou zijn dat uit de drone-toeleveringsketen zou worden gebouwd voor $ 5 tot $ 10.000", zei Kheterpal. "Het zou moeten worden gebouwd vanuit de toeleveringsketen van de tractor, die $ 50.000 kost, en grote pc's met GPU's erop moeten dragen, met tonnen camera's. Toen gingen we onder de motorkap van al die robotsoftware kijken en ontdekten wat de fundamentele oorzaak was van deze energiebehoefte bij platforms als Nvidia en Intel."

Het bedrijf draaide om het bouwen van een acceleratorchip - "de chip die we wensten dat we hadden", aldus Firu.

In 2017 werd een startfinancieringsronde gelanceerd, gevolgd door een Serie A-ronde die $ 13 miljoen opleverde van potentiële klanten, waaronder Quadric's hoofdinvesteerder, de Japanse automotive Tier-One Denso. De totale financiering van Quadric is $ 18 miljoen.

Turing voltooid

Quadric's maakt gebruik van een instructiegestuurde architectuur die elementen uit datastroomarchitecturen overneemt en combineert met elementen van een Von Neumann-machine. Het doel is om heterogene systemen in edge-apparaten te vervangen door iets minder complex. Als complete Turing-machines bieden Quadric Vortex-kernen een combinatie van versnelling met flexibiliteit, beweert het bedrijf. De architectuur is schaalbaar in termen van arrays van kernen en draagbaar tot geavanceerde (7- of 5-nm) procesknooppunten. Dit is geschikt voor edge-apparaattoepassingen met stroombudgetten tussen ongeveer honderden milliwatts tot 20W.

De eerste chip van het bedrijf, de Q16, is een reeks van 16 x 16 Vortex-kernen. Elke kern heeft de mogelijkheid om matrixvermenigvuldiging en AI-berekeningen uit te voeren, maar elke kern heeft ook een multifunctionele ALU, voor bewerkingen zoals AND, OR, reductie, shift en andere. Met software kunnen ontwikkelaars verschillende typen algoritmen uitdrukken, waaronder LSTM-activeringsfuncties en meer. If-Then-Else-instructies zijn beschikbaar in de hele array, waardoor ontwikkelaars kunnen profiteren van fijnmazige schaarste.

Elke core in de array heeft single-cycle toegang tot de aangrenzende cores, plus single-cycle toegang tot in-core geheugen van 4 Kb. On-chip geheugen is ook inbegrepen naast de array, waardoor cores lage latentie, deterministische toegang krijgen.

De kernen werken parallel op wat Quadric een "enkele instructie, meervoudige decodering"-manier noemt; elke kern krijgt bij elke cyclus dezelfde instructie. Maar op basis van dynamische gegevens tijdens runtime kan elke kern die instructie anders interpreteren. Hierdoor kunnen kernen, of groepen kernen, enigszins verschillende functies uitvoeren.

Ook inbegrepen is een speciale uitzendbus die de bandbreedte in de array optimaliseert en kan worden gebruikt om constanten, zoals neurale netwerkgewichten, in alle kernen tegelijk uit te zenden (Firu zei dat veel computervisie-algoritmen ook enige loop-invariante informatie hebben die kan worden in kaart gebracht op de bus).

Dynamische informatie komt de array binnen via statische, softwaregestuurde load-store-eenheden die deterministische kernel-runtimes mogelijk maken. Het apparaat maakt gelijktijdig laden en opslaan vanaf elke twee randen van een apparaat mogelijk, plus een speciale eigenschap van één rand die kan worden gebruikt om neurale netwerkgewichten te verzenden - gelijktijdig laden vanaf twee randen en opslaan vanaf een derde rand kan de runtime van de rekenuitvoering verkorten.

Daniel Firu (Bron:Quadric)

"Je kunt aan één kant laden en vervolgens vanaf een loodrechte kant opslaan", zei Firu. "Dat zorgt ervoor dat er op softwareniveau behoorlijk interessante dingen kunnen gebeuren. Je kunt met dit paradigma ook dingen gaan doen zoals het opnieuw toewijzen van gegevens en het roteren van afbeeldingen en dergelijke dingen."

Ondertussen bieden softwaregestuurde statische geheugens (geen cache) op de chip ruimte voor grote datastructuren. Quadric biedt API-toegang tot deze, zodat ontwikkelaars willekeurige datastructuren binnenin kunnen definiëren. In de Q16-chip zijn de geheugens 8 GB, genoeg om "twee of drie framebuffers bij HD erin te passen, of een heel neuraal netwerk van gewichten", zei Firu.

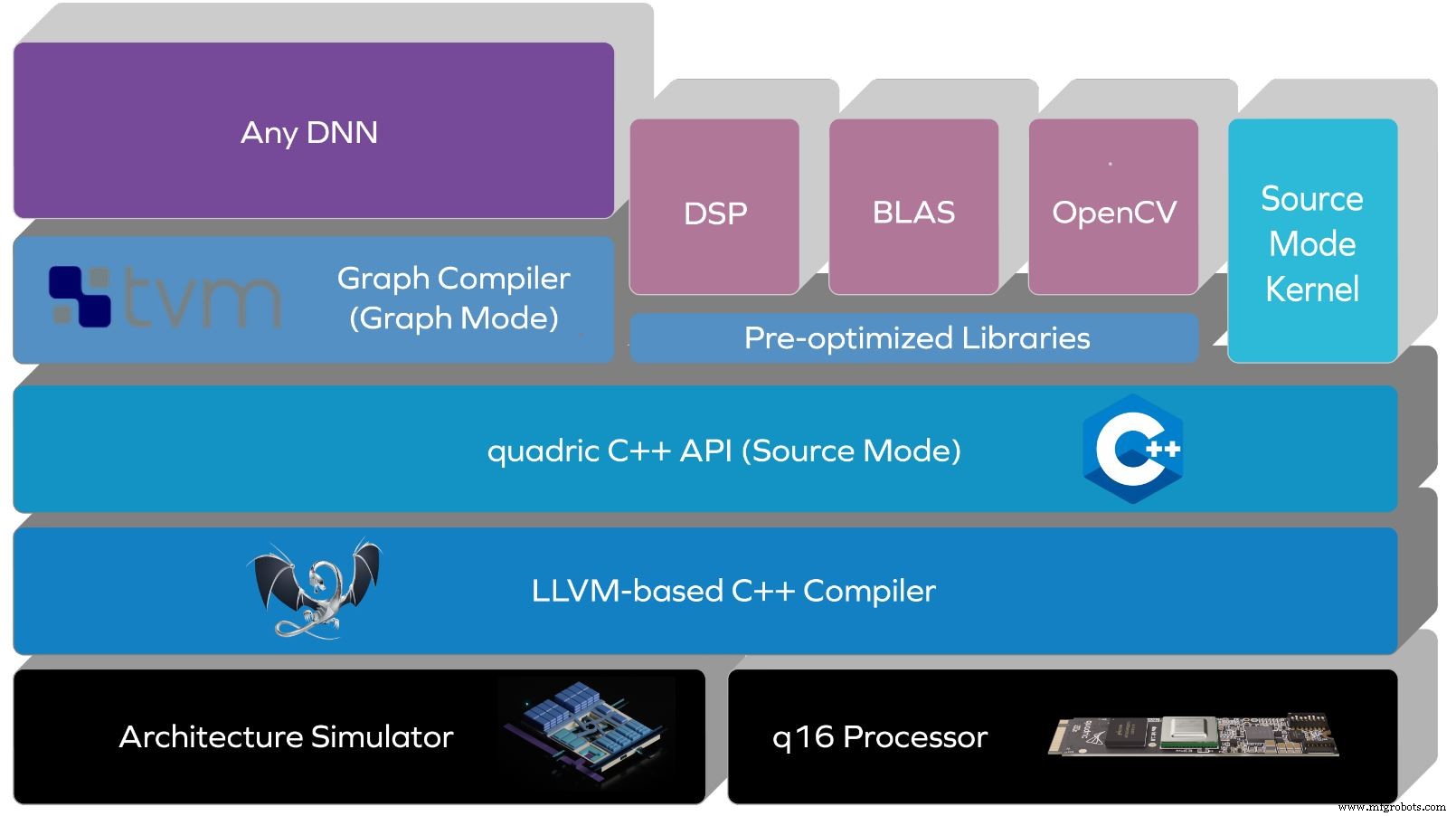

Softwarestack

Quadric bouwde zijn softwarestack vóór silicium. Klanten gebruiken het al een jaar met de architectuursimulator van het bedrijf of met FPGA's, zei Kheterpal. Quadric's stack abstraheert de architectuur en instructieset via een op LLVM gebaseerde compiler, met daarbovenop een C++ API.

De bronmodus ondersteunt verschillende dataparallelle algoritmen met C++-controle op bronniveau van de architectonische kenmerken van de processor. Naarmate neurale netwerken complexer worden, stelt de Bronmodus ontwikkelaars ook in staat om aangepaste bewerkingen uit te drukken.

Quadric's softwarestack (Bron:Quadric)

Een toekomstige update van de stack biedt een grafische modus zonder code, die TensorFlow- of ONNX-versies van neurale netwerken ondersteunt. Dat omvat een op TVM gebaseerde deep neural network (DNN) compiler die automatisch code genereert.

"We combineren de kracht van no-code met de flexibiliteit om uw eigen aangepaste code te hebben en deze op interessante manieren te combineren om uw toepassing te realiseren", aldus Kheterpal. “De meeste platforms bieden alleen een AI-specifieke architectuur met een soort DNN-compiler – maar hoe zit het met maatwerk? Hoe zit het met een DNN die niet wordt ondersteund? Hoe zit het met operators die niet worden ondersteund? We hebben die beperkingen niet omdat dit een complete Turing-kern is, de kernen kunnen elke bewerking uitvoeren. De flexibiliteit van de code geeft ontwikkelaars de mogelijkheid om elk algoritme te schrijven dat ze willen.”

Chip-roadmap

De Q16-chip van Quadric, met 256 Vortex-kernen in een 16 x 16-array in 16 nm silicium, biedt 4 INT8 DNN TOPS. Het kan ResNet-50 uitvoeren met 200 gevolgtrekkingen per seconde (voor INT8-parameters met een beeldformaat van 224 x 224), met een gemiddeld verbruik van 2 W.

De roadmap van Quadric omvat een tweede generatie van de architectuur, plus een tape-out van een Q32-chip (een array van 1.000 cores), "waarschijnlijk in 7 nm", zei Firu. Hoewel de Q16 strikt een versneller is (hij zou naast een systeemhostprocessor zitten), kan de Q32 in ontwikkeling ook Arm- of RISC-V-kernen bevatten om als host te fungeren.

Een ontwikkelaarskit in M.2-formaat, met een Q16-processor en 4 GB extern geheugen dat rechtstreeks is toegewezen aan de universele geheugenruimte van de Q16, is nu beschikbaar.

>> Dit artikel is oorspronkelijk gepubliceerd op onze zustersite, EE Tijden.

Verwante inhoud:

- Hardwareversnellers dienen voor AI-toepassingen

- Als een DSP een hardwareversneller verslaat

- Een gids voor het versnellen van applicaties met precies de juiste RISC-V aangepaste instructies

- De prestatie van de inferentiechip bouwt voort op een geoptimaliseerd ontwerp van het geheugensubsysteem

- Nieuwe AI-versnellingsmodules verbeteren edge-prestaties

- Edge AI daagt geheugentechnologie uit

Abonneer u voor meer Embedded op de wekelijkse e-mailnieuwsbrief van Embedded.

Ingebed

- Hybride cloudomgevingen:een gids voor de beste applicaties, workloads en strategieën

- AI-chiparchitectuur richt zich op grafiekverwerking

- Draadloze MCU met dual-core architectuur

- Gespecialiseerde processors versnellen eindpunt AI-workloads

- Referentieontwerp ondersteunt geheugenintensieve AI-workloads

- Slim sensorbord versnelt edge AI-ontwikkeling

- Slimme camera biedt kant-en-klare edge machine vision edge AI

- IBM presenteert een hybride blockchain-architectuur voor Internet of Things

- Omrons TM Cobot versnelt integratie en programmering

- Hyperspectrale visie. Wat is het?

- Wat is architectuurontwerp?