Processor-in-memory chip versnelt AI-berekeningen

Imec en GlobalFoundries hebben een processor-in-memory-chip gedemonstreerd die een energie-efficiëntie tot 2900 TOPS/W kan bereiken, ongeveer twee ordes van grootte boven de huidige commerciële processor-in-memory-chips. De chip maakt gebruik van een gevestigd idee, analoog computergebruik, geïmplementeerd in SRAM in de 22nm volledig uitgeputte silicium-op-isolator (FD-SOI) procestechnologie van GlobalFoundries. Imec's analoge in-memory compute (AiMC) zal beschikbaar zijn voor GlobalFoundries-klanten als een functie die kan worden geïmplementeerd op het 22FDX-platform van het bedrijf.

Imec's AnIA-testchip, hier gemonteerd op de PCB die wordt gebruikt voor meting en karakterisering, kan tot 2900 TOPS/W halen (Afbeelding:Imec)

Analoge berekening

Analoge compute, of processor-in-memory, is een gevestigde techniek die al wordt gebruikt in commerciële AI-versnellerchips van startups Mythic, Syntiant, Gyrfalcon en anderen.

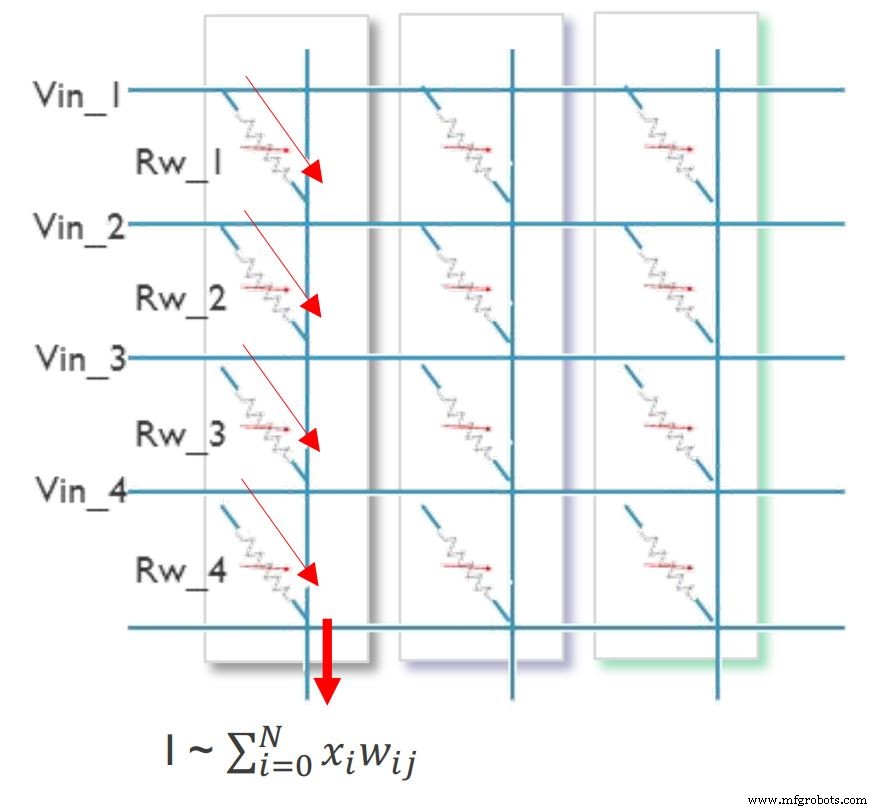

Aangezien een neuraal netwerkmodel tientallen of honderden miljoenen gewichten kan hebben, is het inefficiënt om gegevens heen en weer te sturen tussen het geheugen en de processor. Analog computing maakt gebruik van een geheugenarray om de gewichten op te slaan en ook om multi-accumulate (MAC)-bewerkingen uit te voeren, dus er is geen overdracht van geheugen naar processor nodig. Elk memristorelement (misschien een ReRAM-cel) heeft zijn geleiding geprogrammeerd op een analoog niveau dat evenredig is aan het vereiste gewicht.

Door een spanning toe te passen die evenredig is aan de ingangsactivering (via digitaal-naar-analoog conversie - aan de linkerkant van het onderstaande diagram) betekent dat de stroom door elk element evenredig is met het product van de activering en het gewicht. De stroom door elke verticale bitlijn (verticale lijnen in het onderstaande diagram) is de som van deze activeringsgewichtproducten, die door een analoog-naar-digitaalomzetter kunnen worden gevoerd. Deze som van de activatiegewichtsproducten is van cruciaal belang voor de berekening van neurale netwerkalgoritmen.

Analoog computergebruik gebruikt een reeks memristorcellen om matrixvectorvermenigvuldiging te berekenen zonder gegevens tussen geheugen en processor te hoeven verzenden (Afbeelding:Imec)

“In de praktijk zijn er naast ReRAM veel opties mogelijk — we kunnen MRAM, Flash, DRAM gebruiken… het doel van dit programma is om te begrijpen wat het beste is voor de applicatie en om de opties voor elk applicatiedomein te optimaliseren”, legt Diederik Verkest uit, programma directeur voor machine learning bij imec.

Testchip

Imec heeft een testchip gebouwd, Analog Inference Accelerator (AnIA) genaamd, gebaseerd op het 22nm FD-SOI-proces van GlobalFoundries. AnIA's 512k array van SRAM-cellen plus digitale infrastructuur inclusief 1024 DAC's en 512 ADC's neemt 4 mm 2 in beslag . Het kan ongeveer een half miljoen uitvoeren

Ioannis Papistas (Afbeelding:Imec)

berekeningen per bewerkingscyclus op basis van 6-bits (plustekenbit) ingangsactiveringen, ternaire gewichten (-1, 0, +1) en 6-bits uitgangen.

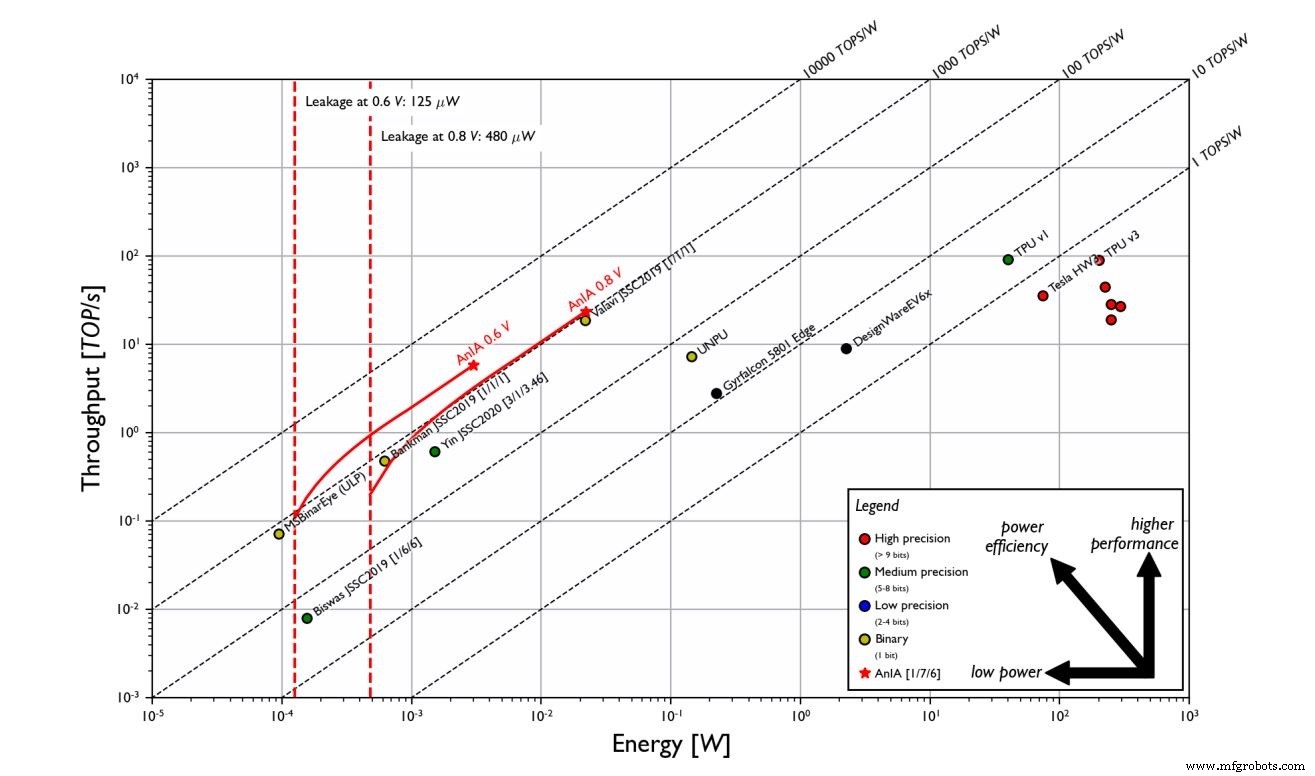

"We zijn in staat om de uitvoer van matrixvectorvermenigvuldiging te produceren bij verschillende voedingsspanningen, 0,8 en 0,6 V", zegt Ioannis Papistas van Imec's machine learning-groep. "Werken met lagere voedingsspanningen zonder de nauwkeurigheid van de bewerking te beïnvloeden, kan het stroomverbruik van de bewerking aanzienlijk verminderen, wat vooral belangrijk is voor inferentie in energiebeperkte systemen. Dit is een belangrijk kenmerk van ons ontwerp, mogelijk gemaakt door het 22FDX-proces, dat concurrerende inferentie op het scherpst van de snede mogelijk maakt.”

Imec toonde nauwkeurigheidsresultaten voor objectherkenningsinferentie op de CIFAR 10-dataset die slechts één procentpunt daalde in vergelijking met een vergelijkbare gekwantiseerde baseline. Met een voedingsspanning van 0,8 V ligt de energie-efficiëntie van AnIA tussen 1050 en 1500 TOPS/W bij 23,5 TOPS. Voor een voedingsspanning van 0,6 V behaalde AnIA 5,8 TOPS bij ongeveer 1800-2900 TOPS/W.

Energie-efficiëntie voor verschillende AI-versnellers vergeleken met Imec's AnIA-testchip (klik om te vergroten) (Afbeelding:Imec)

Mainstream innovatie

"De innovatie [Imec presenteerde] zal mainstream worden", zegt Hiren Majmudar, VP en GM van GlobalFoundries' computing business unit. "We zien partners, klanten van GlobalFoundries die zich in de postproductiefase bevinden met gevalideerd silicium... we verwachten dat analoog, op computers gebaseerd silicium rond het einde van dit jaar of begin volgend jaar in productie zal gaan. Wat de inzet op de massamarkt betreft, verwachten we dat analoge compute zeker niet later dan 2022 op de massamarkt zal verschijnen. Maar het zou mogelijk eerder kunnen gebeuren.”

Diederik Verkest (Afbeelding:Imec)

GlobalFoundries werkt eraan om de AiMC-technologie van Imec op te nemen als een functie die kan worden geïmplementeerd op het 22 FDX-platform om energiezuinige AI-versnellers mogelijk te maken. Het FD-SOI-proces is ontworpen voor een laag stroomverbruik, met de mogelijkheid om te werken tot 0,5 V met 1 pico-ampère per micron voor ultralage standby-lekkage. 22FDX met de nieuwe AiMC-functie is in ontwikkeling bij de 300 mm-productielijn van GlobalFoundries in Fab 1 in Dresden, Duitsland.

Wat Imec betreft, het machine learning-programma zal worden voortgezet. De ambitie van de groep is om 10.000 TOPS/W (10 TOPS onder 100mW) te halen voor always-on slimme sensoren en consumentenwearables, aldus Verkest.

"In ons ML-programma zijn onze volgende stappen om de omvang van deze rekencellen te verkleinen en te gaan kijken naar opkomende geheugenapparaten als een volgende generatie implementatie voor dit principe", zei hij.

>> Dit artikel is oorspronkelijk gepubliceerd op onze zustersite, EE Times.

Ingebed

- Inleiding tot analoge geïntegreerde schakelingen

- Computationele circuits

- Aardappelchips

- Ontwerpen met Bluetooth Mesh:chip of module?

- AI-chiparchitectuur richt zich op grafiekverwerking

- Kleine Bluetooth 5.0-module integreert chipantenne

- Onderzoekers bouwen kleine authenticatie-ID-tag

- 30 fps automotive imaging radarprocessor debuteert

- Low-power radarchip maakt gebruik van spiking neurale netwerken

- Slim sensorbord versnelt edge AI-ontwikkeling

- Duurzame UAV-snelheden tot productie