Een gelijktijdige verklaring maken in VHDL

Een gelijktijdige instructie in VHDL is een signaaltoewijzing binnen de architectuur, maar buiten een normale procesconstructie. De gelijktijdige instructie wordt ook wel een gelijktijdige toewijzing of gelijktijdig proces genoemd.

Wanneer u een gelijktijdige verklaring maakt, creëert u in feite een proces met bepaalde, duidelijk gedefinieerde kenmerken. Gelijktijdige verklaringen zijn altijd gelijk aan een proces dat een gevoeligheidslijst gebruikt, waarbij alle signalen rechts van de signaaltoewijzingsoperator op de gevoeligheidslijst staan.

Deze verkorte notatieprocessen zijn handig wanneer u eenvoudige logica wilt creëren die resulteert in de toewijzing van een enkel signaal. In plaats van een volledige procesconstructie met gevoeligheidslijsten en dergelijke uit te typen, kunt u het doelsignaal eenvoudig rechtstreeks in de architectuur toewijzen.

Deze blogpost maakt deel uit van de serie Basic VHDL Tutorials.

Bij correct gebruik zal de bedoeling van de code nog steeds vrij duidelijk zijn. U hoeft geen proces te maken voor elk bit dat u wilt omdraaien.

Oefening

In deze video leren we hoe u een gelijktijdige verklaring kunt maken:

De laatste code die we in deze tutorial hebben gemaakt:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T13_ConcurrentProcsTb is

end entity;

architecture sim of T13_ConcurrentProcsTb is

signal Uns : unsigned(5 downto 0) := (others => '0');

signal Mul1 : unsigned(7 downto 0);

signal Mul2 : unsigned(7 downto 0);

signal Mul3 : unsigned(7 downto 0);

begin

process is

begin

Uns <= Uns + 1;

wait for 10 ns;

end process;

-- Process multiplying Uns by 4

process is

begin

Mul1 <= Uns & "00";

wait on Uns;

end process;

-- Equivalent process using sensitivity list

process(Uns) is

begin

Mul2 <= Uns & "00";

end process;

-- Equivalent process using a concurrent statement

Mul3 <= Uns & "00";

end architecture;

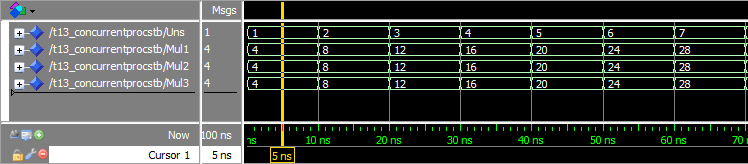

Het golfvormvenster in ModelSim nadat we op run hebben gedrukt en ingezoomd op de tijdlijn:

Analyse

We kunnen aan de golfvorm zien dat Mul1 , Mul2 , en Mul3 precies hetzelfde gedragen. Dit komt omdat het gelijktijdige statement en de twee processen die we hebben gemaakt equivalent zijn.

Een gelijktijdige instructie werkt net als een proces. Alle signalen rechts van de <= worden automatisch toegevoegd aan de gevoeligheidslijst. Dit betekent dat het signaal links van de <= wordt bijgewerkt wanneer een van de geëvalueerde signalen verandert.

Er zijn veel manieren om getallen te vermenigvuldigen in VHDL. In deze oefening vermenigvuldigden we de Uns signaal met 4, met behulp van bitverschuiving. Al onze signalen zijn van unsigned type, wat betekent dat ze worden geïnterpreteerd door getallen. Een 0 toevoegen aan de rechterkant van een binair getal is hetzelfde als het vermenigvuldigen met 2.

Dit is een illustratie van wat er gebeurt bij de cursor in de golfvorm:

Afhaalmaaltijden

- Een gelijktijdige instructie is een signaaltoewijzing direct in de architectuurregio

- Gelijktijdige uitspraken zijn gelijk aan een proces met alle geëvalueerde signalen op de gevoeligheidslijst

Ga naar de volgende tutorial »

VHDL

- Procedureverklaring - VHDL-voorbeeld

- Een lijst met strings maken in VHDL

- Hoe maak je een Tcl-gestuurde testbench voor een VHDL-codeslotmodule?

- Simulatie stoppen in een VHDL-testbench

- Een PWM-controller maken in VHDL

- Hoe maak je een ringbuffer FIFO in VHDL

- Hoe maak je een zelfcontrolerende testbank aan

- Een gekoppelde lijst maken in VHDL

- Een procedure gebruiken in een proces in VHDL

- Een onzuivere functie gebruiken in VHDL

- Een functie gebruiken in VHDL