Zelfstudie - Inleiding tot VHDL

VHDL is een verschrikkelijk acroniem. Het staat voor V HSIC H ardware D beschrijving L taal. Een acroniem in een acroniem, geweldig! VHSIC staat voor V ery H igh S plaste ik geïntegreerde C ircuit. Daarom is VHDL uitgebreid V ery High Speed Integrated Circuit H ardware D beschrijving L taal. Pfoe dat is een mondvol. VHDL is een van de twee talen die door het onderwijs en het bedrijfsleven worden gebruikt om FPGA's en ASIC's te ontwerpen. Als je niet bekend bent met deze fascinerende circuits, heb je misschien eerst baat bij een inleiding tot FPGA's en ASIC's. VHDL en Verilog zijn de twee talen die digitale ontwerpers gebruiken om hun circuits te beschrijven, en ze verschillen qua ontwerp van uw traditionele softwaretalen zoals C en Java.

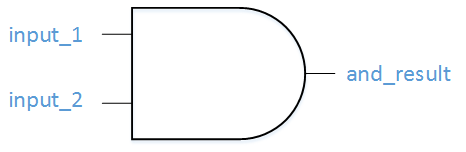

Voor het onderstaande voorbeeld zullen we een VHDL-bestand maken dat beschrijft een En Poort. Als opfriscursus heeft een eenvoudige And Gate twee ingangen en één uitgang. De uitvoer is alleen gelijk aan 1 als beide ingangen gelijk zijn aan 1. Hieronder ziet u een afbeelding van de And Gate die we zullen beschrijven met VHDL.

An And Gate

An And Gate Laten we ernaartoe gaan! De fundamentele eenheid van VHDL wordt een signaal . genoemd . Laten we voor nu aannemen dat een signaal een 0 of een 1 kan zijn (er zijn eigenlijk andere mogelijkheden, maar daar komen we op). Hier is wat basis VHDL-logica:

signal and_gate : std_logic; and_gate <= input_1 and input_2;

De eerste regel code definieert een signaal van het type std_logic en wordt and_gate genoemd. Std_logic is het type dat het meest wordt gebruikt om signalen te definiëren, maar er zijn andere waarover u meer zult leren. Deze code genereert een EN-poort met een enkele uitgang (and_gate) en 2 ingangen (input_1 en input_2). Het trefwoord "en" is gereserveerd in VHDL. De operator <=staat bekend als de toewijzingsoperator. Wanneer je de bovenstaande code verbaal ontleden, kun je hardop zeggen:"Het signaal en_poort KRIJGT input_1 en-ed met input_2."

Nu vraag je je misschien af waar input_1 en input_2 vandaan komen. Zoals hun naam al aangeeft, zijn het inputs voor dit bestand, dus je moet de tools erover vertellen. Ingangen en uitgangen naar een bestand worden gedefinieerd in een entiteit . Een entiteit bevat een poort die alle invoer en uitvoer naar een bestand definieert. Laten we een eenvoudige entiteit maken:

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

Dit is je basisentiteit. Het definieert een entiteit genaamd example_and en 3 signalen, 2 inputs en 1 output, die allemaal van het type std_logic zijn. Er is nog een ander VHDL-sleutelwoord nodig om dit compleet te maken en dat is architectuur . Een architectuur wordt gebruikt om de functionaliteit van een bepaalde entiteit te beschrijven. Zie het als een proefschrift:de entiteit is de inhoudsopgave en de architectuur is de inhoud. Laten we een architectuur maken voor deze entiteit:

architecture rtl of example_and is signal and_gate : std_logic; begin and_gate <= input_1 and input_2; and_result <= and_gate; end rtl;

De bovenstaande code definieert een architectuur met de naam rtl van entiteit example_and. Alle signalen die door de architectuur worden gebruikt, moeten worden gedefinieerd tussen de trefwoorden "is" en "begin". De eigenlijke architectuurlogica komt tussen de trefwoorden "begin" en "eind". Je bent bijna klaar met dit bestand. Een laatste ding dat u de tools moet vertellen, is welke bibliotheek u moet gebruiken. Een bibliotheek definieert hoe bepaalde trefwoorden zich in uw bestand gedragen. Voor nu, neem het als vanzelfsprekend aan dat je deze 2 regels bovenaan je bestand moet hebben:

library ieee; use ieee.std_logic_1164.all;

Gefeliciteerd! U hebt uw eerste VHDL-bestand gemaakt. U kunt het voltooide bestand hier bekijken:

library ieee;

use ieee.std_logic_1164.all;

entity example_and is

port (

input_1 : in std_logic;

input_2 : in std_logic;

and_result : out std_logic

);

end example_and;

architecture rtl of example_and is

signal and_gate : std_logic;

begin

and_gate <= input_1 and input_2;

and_result <= and_gate;

end rtl;

Lijkt het alsof je veel code moest schrijven om een domme en poort te maken? Allereerst, en poorten zijn niet dom. Ten tweede heb je gelijk; VHDL is een zeer uitgebreide taal. Wen er maar aan dat als je iets doet dat heel eenvoudig was in software, je aanzienlijk meer tijd nodig hebt in een HDL zoals Verilog of VHDL. Maar vraag gewoon een softwareman om te proberen een afbeelding te genereren voor een VGA-monitor die Conway's Game of Life weergeeft en kijk hoe hun hoofd ronddraait van verbazing! Die video is trouwens gemaakt met VHDL en een FPGA. Dat lukt je snel genoeg!

VHDL

- Records - VHDL-voorbeeld

- Variabelen - VHDL-voorbeeld

- Een inleiding tot stereolithografie (SLA)

- Een inleiding tot titaniumlegering

- Inleiding tot DC-circuits

- Inleiding tot AC-circuits

- Inleiding tot SPICE

- C Zelfstudie

- Verilog-zelfstudie

- Inleiding tot harmonischen:deel 1

- Inleiding tot SINUMERIK 808D – Video-tutorial Draaien deel 1