Onderzoek naar high-speed PCB-ontwerp in ingebed applicatiesysteem

Modern elektronisch systeem ontwikkelt zich in de trend van klein pakket, grootschalig en hoge snelheid, aangezien de dichtheid van chips steeds groter wordt in SLSI (supergrootschalige integratie), wat onvermijdelijke problemen met zich meebrengt, zoals hoe te analyseren en te handelen met de onderlinge verbindingen en stapelproblemen bij het ontwerpen van hogesnelheidscircuits. Op dit moment bereikt de radiofrequentie van elektronische producten honderden of duizenden MHz en zowel de stijgende rand als de dalende rand worden zo steil dat PCB-lay-outregels en diëlektrische constante van substraatmateriaal uiterst cruciaal zijn voor de elektrische prestaties van het systeem bij het ontwerpen van dergelijke producten.

Als een belangrijk proces en stap in het merendeel van het huidige onderzoek naar elektronische producten, heeft het ontwerp van hogesnelheidsprintplaten de belangrijkste problemen gezien, waaronder timingproblemen, ruisinterferentie en EMI (elektromagnetische interferentie) waarvan de oplossingen verband houden met de normale werking van het systeemontwerp.

Nu leiden traditionele ontwerpmethoden tot de lage betrouwbaarheid en het slagingspercentage van producten, die een hoge praktische waarde en brede marktverwachtingen bieden voor onderzoek naar high-speed PCB-ontwerp in embedded applicatiesystemen.

Systeemschema-ontwerp

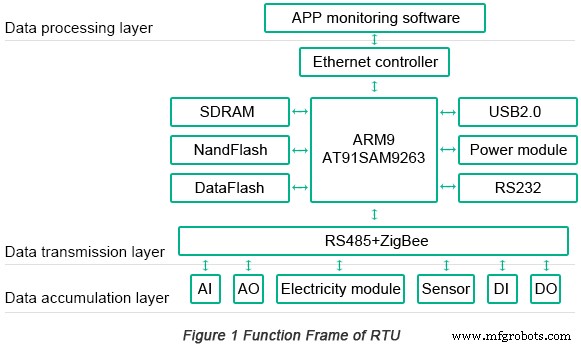

Afbeelding 1 toont het functieframe van embedded RTU (remote terminal unit).

Uit figuur 1 blijkt dat dit systeem een verticale communicatiestructuur is die is samengesteld uit een gegevensaccumulatielaag die de eenheid voor elektriciteitsenergie, een sensoreenheid en een analoge hoeveelheidsmeeteenheid bevat, een gegevenstransmissielaag die een gateway bevat die de gegevens in de gegevensaccumulatielaag aanpast via de commando van internetontvangend ingenieurscentrum en gegevensverwerkingslaag die wordt geïmplementeerd door APP-bewakingssoftware, gegevens in realtime opslaan en analyseren en gegevenscurves maken die worden geconfronteerd met de gebruikersinterface, zodat de flexibiliteit en administratie-efficiëntie van gegevensaccumulatie worden verhoogd.

RTU-systeemhardwareframe

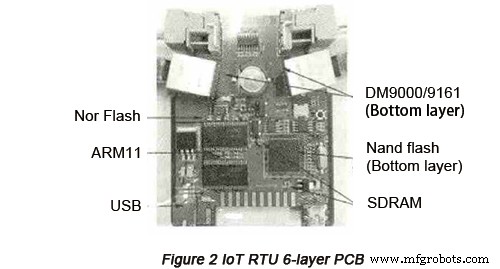

Deze embedded IoT RTU-systeemhardware bestaat voornamelijk uit USB2.0, AT91SAM9263-processor, CAN, SDRAM, Nand Flash, Data Flash, Ethernet-controller, klokchip, RS232/485-interface, onderdelen voor stroombeheer en gegevensaccumulatie.

Dit ontwerp, dat wordt beheerd door het Linux-besturingssysteem, biedt hogere geheugen- en apparaatbeheermogelijkheden, zodat realtime planning voor meerdere missies wordt geïmplementeerd met een complex algoritme en communicatieprotocol dat verantwoordelijk is voor netwerkverbinding, datacommunicatie en configuratie-accumulatie. Afbeelding 2 is de RTU-printplaat die in dit artikel is ontworpen.

Dit systeem ondersteunt de dual-stack van IPv6 en IPv4 en is in staat om de snelheid en realtime-mogelijkheden te implementeren. In termen van gegevensopslag kan aan de eis van lokale opslag worden voldaan onder de voorwaarde van een communicatieblok. Wat de communicatie-interface betreft, beschikt het over verschillende veldgegevenscommunicatie-interfaces, waaronder RS485, RS232 en CAN, die het Modbus RTU-communicatieprotocol ondersteunen en voldoen aan de vereisten van verschillende interfaces en verschillende communicatiesnelheden.

PCB-ontwerp van RTU-systeem

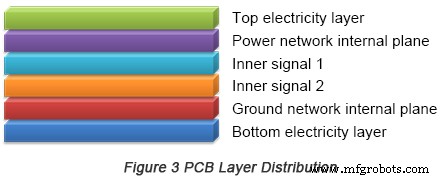

• PCB-stapelontwerp van het systeem

Het aantal lagen PCB's ligt gewoonlijk in het bereik van 2 tot 32, afhankelijk van de moeilijkheidsgraad van het ontwerp. De 6-laags printplaat in dit ontwerp wordt bepaald op basis van de pakketdichtheid van de componenten, de kleine layout-routeringsruimte en de hoge signaalfrequentie. Deze PCB-laagverdeling wordt geïllustreerd in Afbeelding 3 hieronder.

De configuratie van striplijnen wordt in dit systeem opgepikt voor FLASH en SDRAM en routering wordt geïmplementeerd op Inner Signal 1 en Inner Signal 2.

• PCB-beperkingsregels in dit systeem

Tijdens het ontwerpen van high-speed PCB's worden de continuïteit van de impedantie en EMI sterk beïnvloed door de afstand, lengte en breedte van draden en aangrenzende verwerking van lussen. De kwaliteit van de lay-out en routing van de componenten hangt samen met het succes van het uiteindelijke ontwerp, dus PCB-beperkingsregels moeten redelijkerwijs worden toegepast.

Hyper Lynx beschikt over een functionaliteit voor interferentie met kaartanalyse en het IBIS-model kan worden toegepast om verliestransmissie, differentiële signalen en doorgaande gatenmodel dat met de frequentie verandert nauwkeurig te simuleren. Het hoofdnetwerk wordt gesimuleerd voordat het door Line wordt gerouteerd om de PCB-stapelstructuur en de routeringsimpedantie te verbeteren, en regels voor het routeren van high-speed PCB-netwerken worden ontworpen voordat het simulatieresultaat wordt gegenereerd om de ontwerpefficiëntie te verhogen.

• PCB-simulatie van dit systeem

In het proces van high-speed PCB-ontwerp wordt een ideaal transmissielijnmodel toegepast voor simulatie van de frontterminal met eenmalig gesimuleerde beperkte signaallijnen. De transmissielijnen op de PCB-achterterminal zijn echter eigenlijk routeringslijnen van PCB met invloed van doorgaande gaten en vlakkenverschuiving. Onder deze omstandigheden is het verkregen simulatieresultaat uiterst betrouwbaar.

Tijdens het ontwerp van het kerncircuit van het systeem moet de weerstand van het single-terminalsignaal in het bereik van 40 tot 60 liggen en moet de overspraakdrempelwaarde tussen signaallijnen 165 mV zijn. Om de netwerkcontrollers van de DM9000 en DM9161 zelfaanpasbaar te maken voor de communicatiesnelheid van 100 Mbps en de differentiële impedantie moet bovendien binnen de categorie van 100 ± 5Ω vallen. PCB-simulatie wordt geïmplementeerd door Hyper Lynx-simulatiesoftware ontwikkeld door Mentor Graphic op SDRAM, Ethernet-differentiële lijnen, stroomintegriteit en EMC.

a. SDRAM-ontwerp

In het proces van striplijnontwerp zijn overspraak en doorgaande gaten de belangrijkste oorzaken die leiden tot tijdvertraging. Hoewel PCB is voltooid in overeenstemming met de routeringsregels die zijn bepaald door lijnsimulatietools, zijn sommige problemen onvermijdelijk, zoals te veel componentpinnen en beperkte PCB-afmetingen. Daarom is het noodzakelijk om meerdere netwerken op de juiste manier te simuleren via Board-simulatietools.

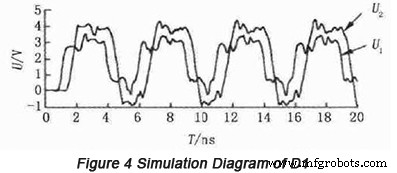

Op basis van het simulatieresultaat is de overspraakintensiteit van het analoge netwerk EBI_D0 en EBI_D2 meer dan 165 mV. De twee netwerken betalen aanval aan EBI_D1 en zoeken naar koppelingsplaats omdat de afstand tussen slangvormige lijnen in het gele markeringsgebied niet geschikt is. Het kan worden geïllustreerd dat het vergroten van de routeringsafstand zal helpen om een dergelijk probleem te elimineren. Waar we echter echt om geven, is waarom het hacknetwerk zo sterk wordt gestoord. De reden ligt mogelijk in de ongeschikte weerstandskeuze die leidt tot een niet-passende impedantie. Tot nu toe is de bepaalde weerstand van de afsluitweerstand 43,1Ω. In de toestand van excitatie van 220 MHz, wordt de analysesimulatiegolf van netwerk EBI_D1 weergegeven in figuur 4 hieronder.

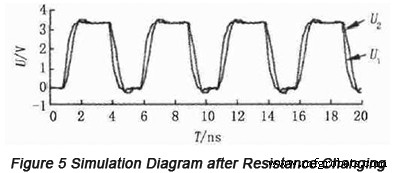

Op basis van figuur 4 vindt impedantiediscontinuïteit plaats op de EMI_D1-transmissielijn en vindt vervorming plaats om golven te signaleren. Hoewel systeemstoringen bij het starten niet kunnen worden veroorzaakt, kan de stabiliteit van de werking van het product nauwelijks worden gegarandeerd. Terug naar Bordsimulatie, doorgaande gaten en beschadigde simulatie worden toegepast om de eindweerstand van EBI_D0 en EBI_D1 te veranderen in 46,9Ω. Daarom wordt het simulatiediagram van overspraak na de verandering van weerstand weergegeven in Afbeelding 5 hieronder.

Op basis van deze figuur kan worden geïllustreerd dat het netwerksignaal is verbeterd en dat de interferentie-intensiteit die wordt opgewekt op EBI_D1 duidelijk is verminderd.

b. Internet differentieel busontwerp

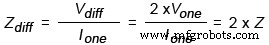

Met kenmerken van hogesnelheids- en 3GIO-interconnecties, past de door Hyper Lynx ontwikkelde kaartsimulatiemodule supersnelle seriële datapad- en bronsynchronisatietechnologie toe op basis van differentiële signaalbus, wat een handig en zeer effectief oplossingsschema biedt voor high-speed PCB-ontwerp. Zowel de DM9000 als de DM9161 in dit systeem hebben twee paar high-speed signaal differentiële bus:TX+, TX- en RX+, RX- met een differentiële impedantie van 100Ω. Dankzij de transmissietheorie kan de differentiële impedantie worden berekend op basis van de formule: .

.

In deze formule verwijst Z naar de transmissie-impedantie van elke signaallijn, wat een cruciaal effect heeft op de communicatieafstand en het vermogen om ruis te weerstaan. Hier wordt DM9000 opgepikt om differentieel naar netwerk TP_E_TX+ en TP_E_TX- te verzenden. Om het effect van reflectie te verminderen, wordt een weerstand van 100Ω parallel geplaatst op signaallijnen met doorlopende gaten.

c. Stroomintegriteitsontwerp van dit systeem

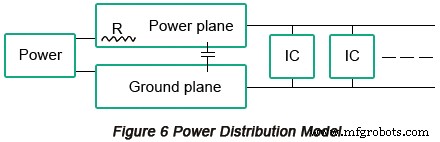

Afbeelding 6 is een basismodel voor stroomdistributie waarin stroom naar elke drager wordt overgebracht via stroomlagen en vervolgens naar de aardlaag.

In het proces van high-speed PCB-ontwerp moet het energieverbruik in elke eenheid worden berekend in het circuitsysteem met de breedte van het stroomnetwerk correct verdeeld en voldoende versterkt.

De vermogensintegriteit van 6 lagen kan als volgt worden samengevat:de maximale drukval is 2,1 mV, dicht bij 0,06%; de maximale stroomdichtheid is 16,3 mA/m²; binnen een geschikte categorie, als de stroomdichtheid 50 mA/m² overschrijdt, zal de temperatuur van PCB stijgen, wat de hoofdchip en signaallijnen tijdens het bedrijf beïnvloedt. Het vergroten van de koperbreedte kan de stroomdichtheid verminderen en het vergroten van de dikte van signaalkabels is nuttig voor het verlagen van de temperatuur van PCB's.

d. Analyse elektromagnetische compatibiliteit van het systeem

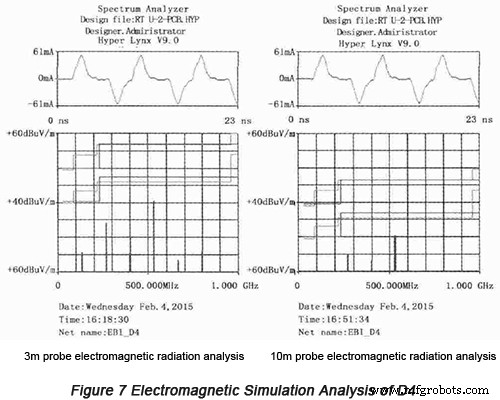

Elektromagnetische interferentie wordt meestal overgedragen als een drager met nuttige signalen bij de koppeling. In dit ontwerp is Hyper Lynx simulatiesoftware toegepast om de stralingsintensiteit van PCB's na voorlopig ontwerp te analyseren. De cruciale signaallijn, D4, wordt opgepikt tussen ARM9 en SDRAM met sondeposities respectievelijk 3m en 10m. In de situatie van een excitatiebron van 220 MHz kunnen zowel FCC- als CISPR-simulatiegegevens met internationale standaard worden verkregen, weergegeven in Afbeelding 7 hieronder.

Op basis van het simulatieresultaat leidt de korte afstand tot PCB tot hoge straling van de printplaat en de straling verandert met de verandering van signaalfrequenties. In het proces van high-speed circuitontwerp kan PCB-anti-interferentie worden geoptimaliseerd terwijl de ruisstraling moet worden verminderd.

Handige bronnen

• Tips voor snelle lay-out

• Technieken voor snelle PCB-routering om de invloed van EMI te verminderen

• Misverstanden en strategieën bij het ontwerpen van snelle PCB's

• Component ingebed PCB-fabricagetechnologie

• Embedded Technology en Component Embedded PCB-assemblageprocedure

• Full Feature PCB-productieservice van PCBCart - Meerdere opties met toegevoegde waarde

• Geavanceerde PCB-assemblageservice van PCBCart - Start vanaf 1 stuk

Industriële technologie

- Fail-safe ontwerp

- PCB-layoutsoftware

- Overwegingen bij PCB-layout

- Ultiboard PCB-ontwerphandleiding

- 3 routeringstechnieken op PCB high-speed signaalcircuitontwerp

- Tips voor snelle lay-out

- Overwegingen bij het thermische ontwerp van PCB's

- Differentiële isometrische verwerking en simulatieverificatie van high-speed PCB-ontwerp

- De meest voorkomende fouten die ingenieurs maken bij het ontwerpen van PCB's

- Signaalintegriteitsanalyse en PCB-ontwerp op high-speed digitaal-analoog gemengd circuit

- Uitdagingen bij het ontwerpen van high-speed PCB's voor signaalintegriteit en hun oplossingen