PCB-ontwerp en onderzoek naar snelle wachtwoordkaarten op basis van PCIE

Op dit moment is de snelle ontwikkeling van internettechnologie getuige van de massale toepassing van e-mail, online betalen en persoonlijke communicatie. Tegen deze achtergrond is informatiebeveiliging wereldwijd een kritisch onderzoeksthema geweest. PKI-technologie (Public Key Infrastructure) biedt beveiligingsservice door gebruik te maken van theorie en technologie van openbare sleutels. PCIE-technologie (Peripheral Component Interface Express) heeft brede toepassingen gekregen in high-speed apparaten als de derde generatie I/O-busstandaard die seriële datatransmissie en point-to-point interconnectietechnologie toepast. Op het gebied van digitaal systeemontwerp leidt een relatief hoge klokfrequentie tot enkele problemen met betrekking tot signaalintegriteit, stroomintegriteit en overspraak, en het traditionele PCB-ontwerp voldoet niet aan de vereiste van systeemstabiliteit.

Dit artikel biedt een PCB-ontwerpschema op een snelle wachtwoordkaart op basis van PCIE volgens de voordelen van PCIE-snelle seriële transmissie.

Algemeen ontwerpschema

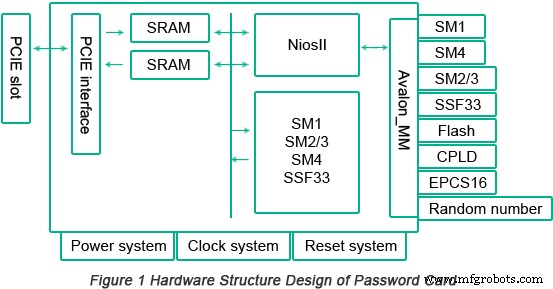

FPGA-chip EP4CGX50CF23C6N behorend tot Cyclone IV GX ontworpen door Altera wordt toegepast in dit ontwerp, waarbij de PCIE IP-hardcore-module wordt geïntegreerd en 4 wachtwoordkaarten met hoge snelheid worden geïmplementeerd. Vier soorten chips, chip 1, chip 2, chip 3 en chip 4, zijn in staat om respectievelijk algoritmen van SM1, SM2/SM3, SM4 en SSF33 te implementeren en functionaliteiten van wachtwoordkaartinitialisatie, geheime sleutelbeheer, back-up en herstel en autoriteit te implementeren beheer. Wachtwoordkaarten worden toegepast in pc's, verbonden met het moederbord in pc's via een PCIE-slot en gecontroleerd door pc's. IP-hardcore in FPGA wordt toegepast om PCIE te implementeren, wat leidt tot de communicatie tussen PCIE-kern en SRAM-cache en besturingsmodule. Als controlecentrum implementeert NiosII de functie van wachtwoordkaartsoftware. Ondertussen implementeert een extra wachtwoordchip de communicatie tussen elke interfacemodule en wachtwoordkaart. Het ontwerp van de hardwarestructuur van de wachtwoordkaart wordt geïllustreerd in Afbeelding 1 hieronder.

Hoge snelheid PCB-ontwerp

• Stapelen en lay-out

Stackup-ontwerp is het belangrijkste probleem waarmee rekening moet worden gehouden en een redelijk stackup-ontwerp kan EMI-straling (Elcetromagnetische Interferentie) remmen, waardoor transiënte spanning op het voedingsvlak of de grondlaag zo klein mogelijk is en het elektromagnetische veld van signaal en vermogen wordt afgeschermd. Over het algemeen worden meerlagige kaarten en meerdere vermogens toegepast bij het ontwerpen van digitale schakelingen met hoge snelheid. PCB-stapelontwerp is geïmplementeerd op basis van uitgebreide elementen, waaronder circuitklokfrequentie, PCB-fabricagekosten, pindichtheid, productieperiode en betrouwbaarheid. Bovendien moeten lagen meerlagig karton symmetrisch worden gehouden en moet het aantal planken een even aantal zijn, aangezien een asymmetrisch stapelontwerp kromtrekken van planken zal veroorzaken. De wachtwoordkaart die in dit artikel is ontworpen, is verbonden met de pc via de PCIE-sleuf en de grootte en vorm van de printplaat is vastgezet met een hoogte van ongeveer 67 mm en een lengte van ongeveer 174 mm, waarbij de PCIE X4-interfacepin onderaan wordt geconfigureerd. Als gevolg van de hoge componentdichtheid en dikke routering wordt het aantal PCB-lagen opgepikt als 6 lagen met verdeling van signaallaag, vermogenslaag, signaallaag, vermogenslaag, grondlaag, signaallaag. Dit ontwerp bevat 3 signaallagen, 1 grondlaag en 2 stroomlagen en biedt de omgeving die vereist is voor signaalintegriteit.

Na de bepaling van PCB-stapeling, moeten componentengroepen en lay-out worden geïmplementeerd. Ten eerste moet de positie van componenten worden geprogrammeerd in overeenstemming met de afmetingen en het patroon van de PCB, waarbij rekening wordt gehouden met lijnverbinding, functionele partities en trim en schoonheid tussen componenten. Vervolgens moeten componenten redelijk worden verdeeld volgens verschillende graden van componentspanning om de spanningsdraden zo kort mogelijk te maken, wat in staat is om de interferentie van stroomruis te verminderen en de stabiliteit van de stroom te vergroten. Bij het plaatsen van de chip moet aandacht worden besteed aan de relatie tussen het hulpcircuit en de chip en aan de plaatsing van de kristaloscillator achter klokpinnen. Er moet worden vermeden dat componenten met veel ruis rond de kristaloscillator worden geplaatst en zich in de buurt van de aandrijfcomponenten bevinden. Bovendien moet de plaatsing van de stroom- en signaalpinnen van elke chip worden overwogen met hun posities en richting aangepast op basis van de verbonden lijnen. Omdat de verhouding tussen lengte en breedte van de wachtwoordkaart meer dan 2:1 is met de posities van de PCIE-sleuf, laadgaten en indicatie-LED vast, moet de componentlay-out voor vaste componenten als eerste in de componentlay-out worden overwogen. Bovendien, als gevolg van het grote aantal verbindingslijnen tussen component en FPGA, moet de lay-out van de componenten worden geïmplementeerd met FPGA als middelpunt voorafgaand aan posities van andere componenten, zodat de bovenste en onderste kamer van PCB effectief kunnen worden gebruikt om om voldoende ruimte tussen componenten en componenten en positioneringsgaten te laten.

• Krachtontwerp

Bij het ontwerpen van high-speed printplaten is het ontwerp van het voedingssysteem direct gerelateerd aan het succes van het hele systeem. Geluid dat wordt gegenereerd door stroom en aarde moet tot een minimum worden beperkt om de betrouwbaarheid van producten te garanderen. De toepassing van een stroomverdelingsschema in de methode van lagen verwijst naar het feit dat de stroom door het metaal over de hele laag wordt verdeeld, waardoor de vermogensimpedantie en ruis afnemen en de betrouwbaarheid toeneemt. Omdat PCB betrekking heeft op meerdere vermogens, moet een ontwerp met meerdere vermogenslagen worden toegepast, dat in staat is om openbare impedantiekoppelingsinterferentie als een ruislus te elimineren. De toepassing van ontkoppelingscapaciteit is in staat om het probleem van stroomintegriteit op te lossen, aangezien de condensator alleen op de onderste of bovenste laag van de PCB kan worden geplaatst, op basis waarvan de draden die de ontkoppelingscondensatoren verbinden kort en breed moeten zijn. Afhankelijk van het chipmateriaal kan de stroom die door hoogspanningslijnen gaat worden berekend en kan de breedte van de kabels worden bepaald. Hoe breder de kabels zijn, hoe meer stroom ze kunnen dragen. De experimentele formule wordt geïllustreerd als:W(lijnbreedte:mm) ≥ L(mm/A) x I(stroom:A)

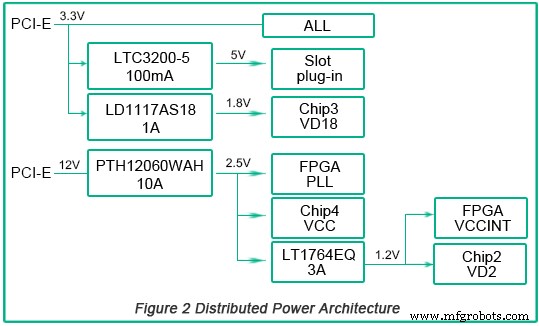

Meerdere voedingen op de printplaat verkrijgen een of twee soorten voeding van de voedingskaart met behulp van de achterkaart en de voeding wordt vervolgens omgezet in ander vermogen dat nodig is voor componenten. De conversie van stroom is verdeeld in twee architecturen:gecentraliseerde stroomarchitectuur en gedistribueerde stroomarchitectuur. De eerste verwijst naar stroom die wordt geleverd door een onafhankelijke kracht en vervolgens wordt omgezet in allerlei vereiste vermogens, terwijl de laatste verwijst naar multi-grade stroomconversie. Omdat gecentraliseerde voedingsarchitectuur nadelen heeft van hoge kosten en een groot PCB-oppervlak, wordt in dit ontwerp een gedistribueerde voedingsarchitectuur toegepast. Cryptografische kaart betreft 6 vermogens, waaronder 12V, 3.3V, 5V, 2.5V, 1.2V en 1.8V. Dit ontwerp begint met de deelname van 3,3V- en 12V-stroom in het PCIE-slot en vervolgens is 3,3V-stroom in staat om 5V-stroom en 1,8V-stroom te genereren via een spanningsconversiechip, die stroom levert voor plug-in en chip 3. Vervolgens wordt 12V-stroom omgezet in 2,5V-stroom om stroom te leveren voor FPGA en chip 4. Ten slotte wordt 2,5V-stroom omgezet in 1,2V-stroom om stroom te leveren voor FPGA en chip 2. De gedistribueerde stroomarchitectuur van de cryptografische kaart wordt weergegeven in Afbeelding 2 hieronder.

• Doorlopend ontwerp

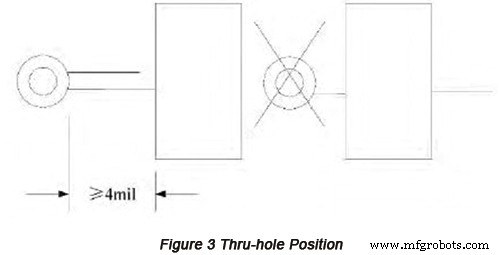

In het proces van ontwerplay-out voor meerlaagse PCB's met een hoge dichtheid, moeten doorlopende gaten worden toegepast, waarbij het signaal van de ene laag naar de andere laag wordt verzonden om elektrische communicatie tussen lagen te bieden. Positieontwerp van doorlopende gaten moet met veel zorg worden uitgevoerd. Er mogen geen doorlopende gaten op de pad worden geplaatst en er kan één gedrukte lijn worden aangebracht voor verbinding, anders leidt dit tot problemen zoals grafsteen en onvoldoende soldeer. Soldeermasker moet worden gecoat op een doorlopende pad met een afstand ingesteld op 4 mil en doorgaande gaten mogen niet in het midden van de pad worden geplaatst voor chipcomponenten aan de soldeerzijde. De positie van de doorgaande gaten wordt geïllustreerd in Afbeelding 3 hieronder.

Bovendien mag de doorlopende positie niet te dicht bij Goldfinger zijn waarvan de plug-in-zijde een afschuining moet hebben. Om printplaten in de PCIE-sleuf te laten steken, kan een afschuining van (1~1,5)x45° worden ontworpen aan twee zijranden van het insteekbord.

• Signaalroutering met hoge snelheid

In het proces van routering moet de distributie redelijk worden aangepast om verbindingslijnen tot een minimum te beperken, zodat overspraak kan worden verminderd. Tijdens het proces van digitale signaalroutering met hoge snelheid, moet de signaallaag in de buurt van multi-power laagroutering ver weg zijn van het referentie-oppervlak van de stroom om het genereren van een terugkerend pad door signaalstroom te voorkomen.

Aangezien de signaalfrequentie van de high-speed circuitklok relatief hoog is, hebben de jitter, drift en vervorming een grote invloed op het systeem, zodat het high-speed PCB-ontwerp een kleine signaalgolfinterferentie vereist. Daarom moet eerst het probleem van klokdistributie en routering worden overwogen. Routing moet worden geïmplementeerd op hogesnelheidskloksignalen en de routering van hoofdkloksignaallijnen moet zo kort mogelijk zijn, recht en vrij van doorvoergaten en stroomgedeelte om overspraak tussen klok en stroom te voorkomen. Wanneer meerdere klokken met verschillende frequenties op dezelfde printplaat worden toegepast, mogen twee kloklijnen met verschillende frequenties niet parallel worden gehouden. Voor meerdere componenten die kloksignalen met dezelfde frequentie gebruiken, kan het netwerk echter worden gedistribueerd per spidertype, boomtype en vertakkingstype.

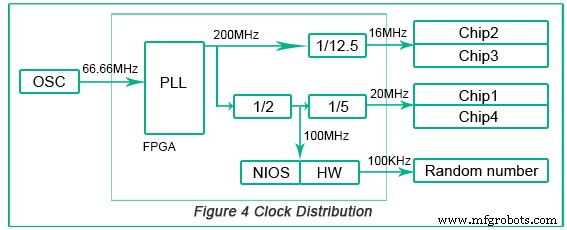

In een snelle cryptografische kaart verkrijgt FPGA een kloksnelheid van 66,66 MHz via de kristaloscillator op de PCB. Na een lus met intrinsieke vergrendelingen in FPGA, wordt 200 MHz basisklok gegenereerd als de interface voor chip 2 en chip 3 om de klok te bedienen. Vervolgens wordt een 100MHz-klok geleverd na het intrinsieke frequentiedelingscircuit als NiosII-softcore en de werkende klok van het hardwarecircuit in FPGA. De gedeelde frequentie 16 MHz is de werkklok voor chip 2 en chip 3, terwijl de gedeelde frequentie 20 MHz de werkklok is voor chip 1 en chip 4. De klokdistributie wordt weergegeven in Afbeelding 4 hieronder.

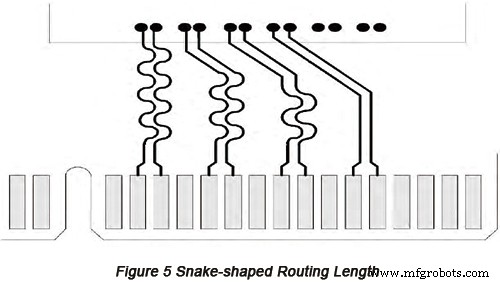

High-speed signaaloverdracht tussen PCIE-slot en pc wordt geïmplementeerd door een high-speed cryptografische kaart in de manier van differentiële paarroutering om problemen met de signaalintegriteit te voorkomen. Over het algemeen worden aardingsdraden niet tussen differentiële paarsignalen geplaatst, anders wordt het koppelingseffect tussen differentiële paarsignalen vernietigd. Na de routering van differentiële paarsignalen, wordt koper rond PCB-hogesnelheidssignalen geplaatst met vrije ruimte die volledig is gevuld met aardingsdraden om de EMI-capaciteit van het circuit te vergroten. De sleutel van PCB-routing is om de symmetrie van differentiële paren te behouden. Als de lengte van differentiële paren niet compatibel is, zal de nauwkeurigheid van het lezen en schrijven van gegevens worden beïnvloed door de verminderde gegevensoverdrachtsnelheid. Om de validiteit van het systeem voor het lezen van gegevens binnen dezelfde periode te garanderen, moet het vertragingsverschil tussen differentiële signalen binnen een toegestane categorie worden gehouden en moet de routeringslengte strikt hetzelfde zijn. Daarom kan slangvormige routering worden toegepast om dit probleem op te lossen door de tijdvertraging aan te passen. In dit ontwerp wordt communicatie geïmplementeerd door pc via PCIE en cryptografische kaart en het verzenden en ontvangen van hogesnelheidssignalen wordt geïmplementeerd door differentiële paarsignalen met de lengte van PCB-routering binnen 25 mil. Het overeenkomende diagram van slangvormige routeringslengte wordt geïllustreerd in figuur 5.

Handige bronnen

• Hoe hoogwaardige PCB's te ontwerpen

• PCB-ontwerpelementen die SMT-productie beïnvloeden

• Onderzoek naar high-speed PCB-ontwerp in ingebed applicatiesysteem

• Differentiële isometrische verwerking en Simulatieverificatie van high-speed PCB-ontwerp

• Full Feature PCB-productieservice van PCBCart - Meerdere opties met toegevoegde waarde

• Geavanceerde PCB-assemblageservice van PCBCart - Start vanaf 1 stuk

Industriële technologie

- PCB-materialen en ontwerp voor hoogspanning

- Flex- en Rigid-Flex Bend-mogelijkheden in PCB-ontwerp

- Stappen en proces Leer om uw PCB-ontwerp te beschermen

- Een richtlijn van schematisch tot PCB-ontwerp op basis van Altium Designer

- Tegenslagen en oplossingen in RF PCB-ontwerp

- 3 routeringstechnieken op PCB high-speed signaalcircuitontwerp

- Tips voor snelle lay-out

- Intern ontwerp van thermische dissipatie van PCB op basis van thermisch model

- Discussie over voeding en aarde in elektromagnetische compatibiliteit van PCB

- Differentiële isometrische verwerking en simulatieverificatie van high-speed PCB-ontwerp

- Signaalintegriteitsanalyse en PCB-ontwerp op high-speed digitaal-analoog gemengd circuit