Shift Registers:Parallel-in, Serial-out (PISO) conversie

Parallel-in/serieel-uit schuifregisters doen alles wat de vorige serieel-in/serieel-uit schuifregisters doen, plus invoergegevens naar alle fasen tegelijk.

Het parallel-in/seriële-uit schuifregister slaat gegevens op, verschuift deze klok voor klok en vertraagt deze met het aantal stappen maal de klokperiode.

Bovendien betekent parallel-in/serial-out dat we gegevens parallel in alle stadia kunnen laden voordat er enige verschuiving ooit begint.

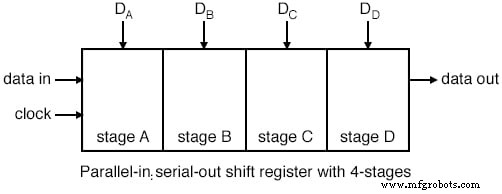

Dit is een manier om gegevens te converteren van een parallel formaat naar een serie formaat. Met parallel formaat bedoelen we dat de databits tegelijkertijd aanwezig zijn op individuele draden, één voor elke databit zoals hieronder weergegeven.

Met serieel formaat bedoelen we dat de databits sequentieel in de tijd worden gepresenteerd op een enkele draad of circuit, zoals in het geval van de "data out" in het onderstaande blokschema.

Hieronder bekijken we de interne details van een 3-traps parallel-in/serieel-uit schuifregister.

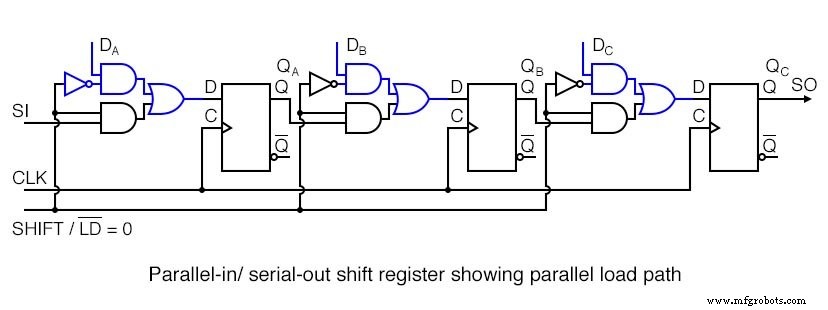

Een stage bestaat uit een type D Flip-Flop voor opslag en een EN-OF-selector om te bepalen of gegevens parallel worden geladen of opgeslagen gegevens naar rechts worden verschoven.

Over het algemeen zullen deze elementen worden gerepliceerd voor het aantal vereiste fasen. We laten drie fasen zien vanwege ruimtebeperkingen.

Vier, acht of zestien bits is normaal voor echte delen.

Hierboven laten we het parallelle belastingspad zien wanneer SHIFT/LD' logisch laag is. De bovenste NAND-poorten die DA . bedienen DB DC zijn ingeschakeld, gegevens doorgeven aan de D-ingangen van het type D Teenslippers QA QB DC respectievelijk.

Bij de volgende positieve klokflank worden de gegevens geklokt van D naar Q van de drie FF's. Er worden drie bits gegevens in QA . geladen QB DC tegelijkertijd.

Het zojuist beschreven type parallelle belasting, waarbij de gegevens op een klokpuls worden geladen, staat bekend als synchrone belasting omdat het laden van gegevens wordt gesynchroniseerd met de klok.

Dit moet worden onderscheiden van asynchrone belasting waar het laden wordt geregeld door de vooraf ingestelde en duidelijke pinnen van de flip-flops waarvoor de klok niet nodig is.

Slechts één van deze laadmethoden wordt gebruikt binnen een afzonderlijk apparaat, de synchrone belasting komt vaker voor bij nieuwere apparaten.

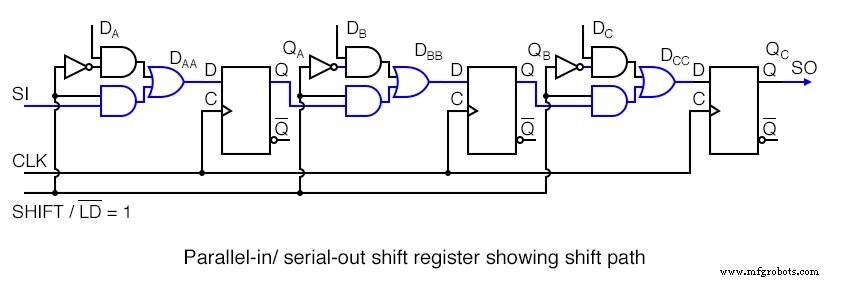

Het schakelpad wordt hierboven weergegeven wanneer SHIFT/LD' logisch hoog is. De onderste EN-poorten van de paren die de OF-poort voeden, zijn ingeschakeld en geven ons een schuifregisterverbinding van SI naar DA , VA naar DB , QB naar DC , QC naar ZO. Klokpulsen zorgen ervoor dat gegevens bij opeenvolgende pulsen naar rechts worden verschoven naar SO.

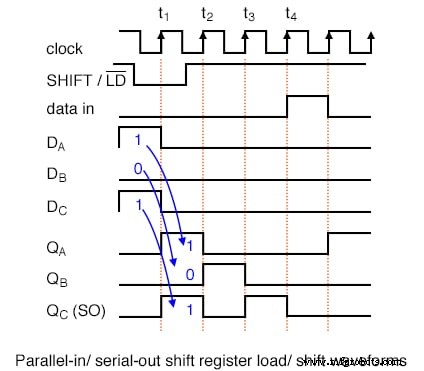

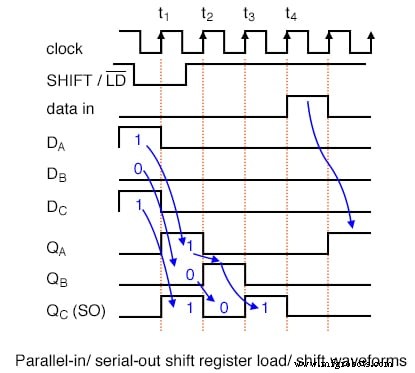

De onderstaande golfvormen tonen zowel parallel laden van drie bits gegevens als seriële verschuiving van deze gegevens. Parallelle gegevens op DA DB DC wordt geconverteerd naar seriële data bij SO.

Wat we eerder beschreven met woorden voor parallel laden en verschuiven, is nu als golfvormen hierboven vastgelegd.

Als voorbeeld presenteren we 101 naar de parallelle ingangen DAA DBB DCC . Vervolgens gaat de SHIFT/LD' laag, waardoor het laden van gegevens mogelijk wordt in plaats van het verschuiven van gegevens.

Het moet een korte tijd voor en na de klokpuls laag zijn vanwege vereisten voor instellen en vasthouden. Het is aanzienlijk breder dan het moet zijn.

Met synchrone logica is het echter handig om het breed te maken. We hadden de actieve lage SHIFT/LD' bijna twee klokken breed kunnen maken, laag bijna een klok voor t1 en terug hoog net voor t3 .

De belangrijke factor is dat het de klok rond laag moet zijn t1 om parallel laden van de gegevens door de klok mogelijk te maken.

Merk op dat bij t1 de gegevens 101 bij DA DB DC wordt geklokt van D naar Q van de Flip-Flops zoals weergegeven bij QA QB QC op tijd t1 .

Dit is het parallel laden van de gegevens synchroon met de klok.

Nu de gegevens zijn geladen, kunnen we deze verschuiven op voorwaarde dat SHIFT/LD' hoog is om verschuiving mogelijk te maken, wat vóór t2 is .

Op t2 de gegevens 0 bij QC wordt verschoven uit SO wat hetzelfde is als de QC golfvorm. Het wordt ofwel naar een ander geïntegreerd circuit verplaatst of gaat verloren als er niets op SO is aangesloten.

De gegevens bij QB , een 0 wordt verschoven naar QC . De 1 bij QA wordt verschoven naar QB . Met “gegevens in” een 0 , VA wordt 0 . Na t2 , VA QB QC =010 .

Na t3 , VA QB QC =001 . Deze 1 , die oorspronkelijk aanwezig was op QA na t1 , is nu aanwezig bij SO en QC .

De laatste databit wordt verschoven naar een externe geïntegreerde schakeling als deze bestaat. Na t4 alle gegevens van de parallelle belasting zijn verdwenen.

Op klok t5 we tonen het inschuiven van een data 1 aanwezig op de SI, seriële ingang.

V:Waarom SI- en SO-pinnen op een schuifregister leveren?

A:Deze verbindingen stellen ons in staat om schuifregistertrappen te cascaderen om grotere shifters te bieden dan beschikbaar in een enkel IC-pakket (Integrated Circuit). Ze maken ook seriële verbindingen van en naar andere IC's mogelijk, zoals microprocessors.

Laten we eens nader kijken naar parallel-in/seriële-uit schuifregisters die beschikbaar zijn als geïntegreerde schakelingen, met dank aan Texas Instruments.

Volg deze links voor volledige apparaatgegevensbladen.

Parallel-in/serial-out apparaten

- SN74ALS166 parallel-in/serieel-uit 8-bit schuifregister, synchrone belasting

- SN74ALS165 parallel-in/serieel-uit 8-bit schuifregister, asynchrone belasting

- CD4014B parallel-in/serieel-uit 8-bit schuifregister, synchrone belasting

- SN74LS647 parallel-in/serieel-uit 16-bit schuifregister, synchrone belasting

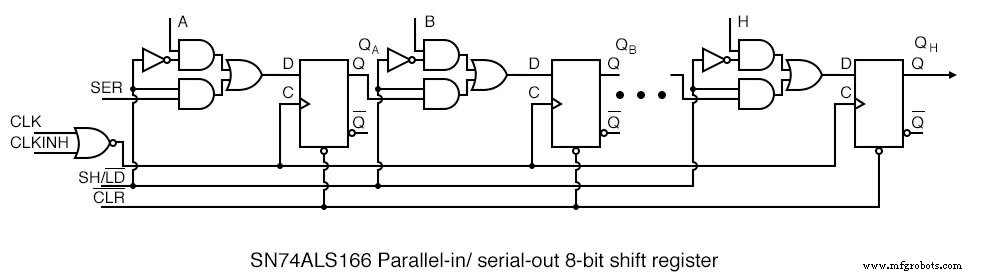

De hierboven getoonde SN74ALS166 is de dichtstbijzijnde match van een echt onderdeel met de vorige parallel-in/seriële uit shifter-cijfers.

Laten we de kleine wijzigingen in onze bovenstaande figuur noteren. Allereerst zijn er 8 fasen. We laten er maar drie zien.

Alle 8-fasen worden weergegeven op het gegevensblad dat beschikbaar is via de bovenstaande link. De fabrikant labelt de data-ingangen A, B, C, enzovoort tot H.

De SHIFT/LOAD-regelaar wordt SH/LD' genoemd. Het is afgekort van onze vorige terminologie, maar werkt hetzelfde:parallelle belasting indien laag, shift indien hoog.

De shift-ingang (seriële data in) is SER op de ALS166 in plaats van SI. De klok CLK wordt bestuurd door een blokkeersignaal, CLKINH.

Als CLKINH hoog is, wordt de klok geblokkeerd of uitgeschakeld. Anders is dit "echte deel" hetzelfde als waar we in detail naar hebben gekeken.

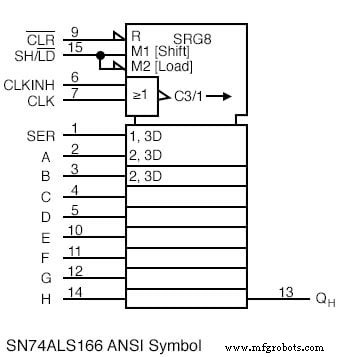

Hierboven staat het ANSI-symbool (American National Standards Institute) voor de SN74ALS166 zoals vermeld op het gegevensblad.

Als we eenmaal weten hoe het onderdeel werkt, is het handig om de details binnen een symbool te verbergen. Er zijn veel algemene vormen van symbolen.

Het voordeel van het ANSI-symbool is dat de labels hints geven over hoe het onderdeel werkt.

Het grote ingekeepte blok aan de bovenkant van de '74ASL166 is het bedieningsgedeelte van het ANSI-symbool. Er is een reset aangegeven door R .

Er zijn drie stuursignalen:M1 (Shift), M2 (Laden) en C3/1 (pijl) (geblokkeerde klok). De klok heeft twee functies.

Ten eerste, C3 voor het verplaatsen van parallelle gegevens waar een voorvoegsel van 3 verschijnt. Ten tweede, wanneer M1 wordt beweerd, zoals aangegeven door de 1 van C3/1 (pijl) , worden de gegevens verschoven zoals aangegeven door de naar rechts wijzende pijl.

De schuine streep (/) is een scheidingsteken tussen deze twee functies. De fasen van 8 ploegen, zoals aangegeven door titel SRG8 , worden geïdentificeerd door de externe ingangen A, B, C, tot H .

De interne 2, 3D geeft aan dat gegevens, D , wordt beheerd door M2 [Laden] en C3 klok. In dit geval kunnen we concluderen dat de parallelle gegevens synchroon worden geladen met de klok C3 .

De bovenste trap bij A is een breder blok dan de andere voor de invoer SER .

De legende 1, 3D houdt in dat SER wordt bestuurd door M1 [Shift] en C3 klok. We verwachten dus gegevens in te klokken bij SER bij het schakelen in tegenstelling tot parallel laden.

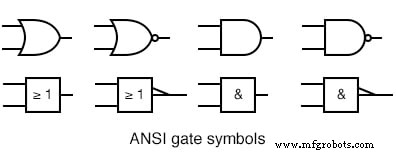

De ANSI/IEEE basispoort rechthoekige symbolen worden hierboven gegeven ter vergelijking met de meer bekende vormsymbolen zodat we de betekenis van de symboliek van de CLKIN . kunnen ontcijferen H en CLK pinnen op het vorige ANSI SN74ALS166-symbool.

De CLK en CLKINH geven een OF poort op het SN74ALS166 ANSI-symbool. OF wordt aangegeven door => op het rechthoekige inzetsymbool.

De lange driehoek aan de uitgang geeft een klok aan. Als er een bel met de pijl was, zou dit een verschuiving op de negatieve klokflank hebben aangegeven (van hoog naar laag).

Omdat er geen bel is met de klokpijl, verschuift het register op de positieve (van lage naar hoge overgang) klokflank.

De lange pijl, na de legende C3/1 naar rechts wijzend geeft verschuiving naar rechts aan, dat is het symbool omlaag.

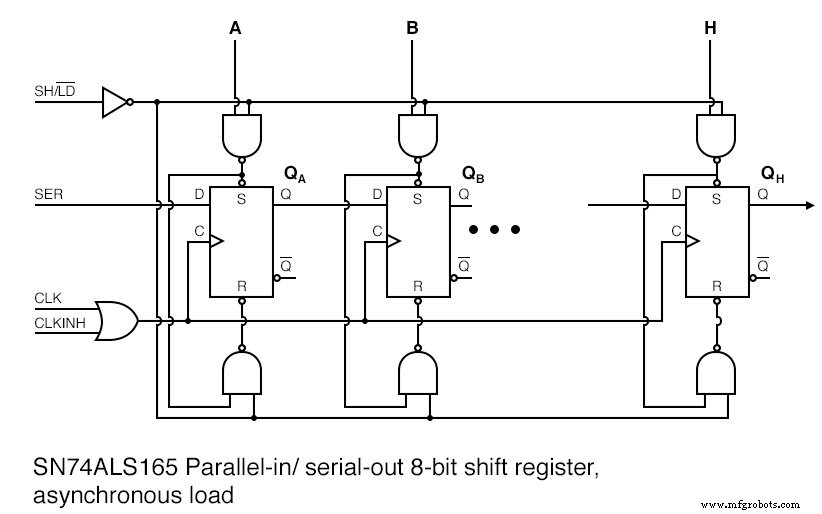

Een deel van de interne logica van het SN74ALS165 parallel-in/serial-out, asynchrone load-shift register wordt gereproduceerd uit het bovenstaande gegevensblad.

Zie de link aan het begin van deze sectie voor het volledige diagram. We hebben tot nu toe niet gekeken naar het asynchroon laden van gegevens.

Allereerst wordt het laden bereikt door de juiste signalen toe te passen op de Set (preset) en Reset (heldere) ingangen van de Flip-Flops.

De bovenste NAND poorten voeden de Set pinnen van de FF's en ook cascades in de lagere NAND poort voedt de Reset pinnen van de FF's.

De lagere NAND gate keert het signaal om vanaf de Set vastzetten op de Reset pinnen.

Ten eerste, SH/LD' moet Laag worden getrokken om de bovenste en onderste NAND . in te schakelen poorten.

Als SH/LD' waren op een logische high in plaats daarvan voedt de omvormer een logisch laag aan iedereen NAND poorten zouden een High . forceren uit, waarbij de "actieve laag" Set . wordt losgelaten en Resetten pinnen van alle FF's.

Er zou geen mogelijkheid zijn om de FF's te laden.

Met SH/LD' gehouden Laag , we kunnen bijvoorbeeld een gegevens 1 naar parallelle ingang A , die wordt omgekeerd naar een nul bovenaan NAND poortuitgang, instelling FF QA naar een 1 .

De 0 bij de Set pin wordt ingevoerd in de onderste NAND poort waar het wordt omgekeerd naar een 1 , het loslaten van de Reset speld van QA .

Dus een data A=1 stelt QA . in =1 . Aangezien hiervoor geen klok nodig was, is het laden asynchroon ten opzichte van de klok.

We gebruiken een asynchroon ladend schuifregister als we niet kunnen wachten tot een klok gegevens parallel laadt, of als het onhandig is om een enkele klokpuls te genereren.

Het enige verschil in het invoeren van een gegevens 0 naar parallelle ingang A is dat het inverteert naar een 1 uit de bovenste poort en laat Set . los .

Deze 1 bij Set wordt omgekeerd naar een 0 bij de onderste poort, Reset . trekken naar een Laag , waarmee QA . wordt gereset =0 .

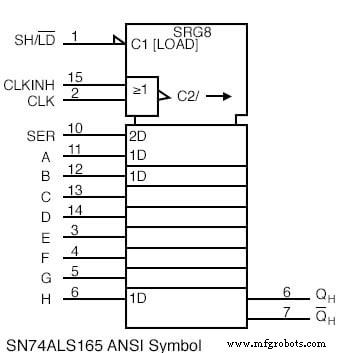

Het ANSI-symbool voor de SN74ALS166 hierboven heeft twee interne controles C1 [LOAD] en C2 klok van de OF functie van (CLKINH, CLK ).

SRG8 zegt 8-traps shifter. De pijl na C2 geeft aan naar rechts of naar beneden te schakelen. SER invoer is een functie van de klok zoals aangegeven door het interne label 2D .

De parallelle data-ingangen A, B, C tot H zijn een functie van C1 [LOAD], aangegeven door het interne label 1D .

C1 wordt bevestigd wanneer sh/LD’ =0 door de half-pijl-omvormer aan de ingang.

Vergelijk dit met de besturing van de parallelle data-ingangen door de klok van de vorige synchrone ANSI SN75ALS166. Let op de verschillen in de ANSI-gegevenslabels.

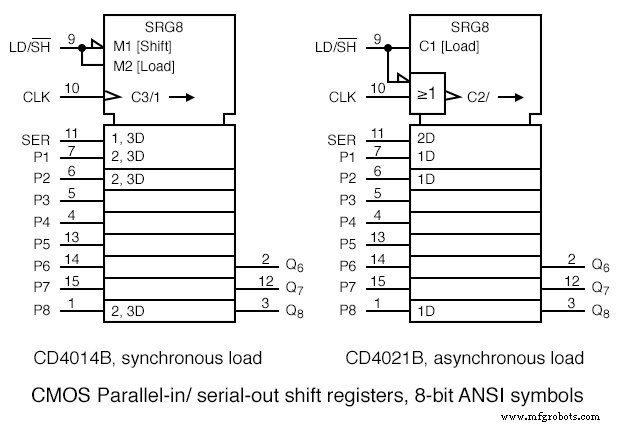

Op de CD4014B hierboven, M1 wordt bevestigd wanneer LD/SH'=0 . M2 wordt bevestigd wanneer LD/SH'=1 .

Klok C3/1 wordt gebruikt voor het parallel laden van gegevens op 2, 3D wanneer M2 is actief zoals aangegeven door de 2,3 voorvoegsellabels.

Pinnen P3 naar P7 worden geacht de interne 2,3 . te hebben voorvoegsellabels als P2 en P8 . Bij SER , de 1,3D voorvoegsel houdt in dat M1 en klok C3 zijn nodig om seriële gegevens in te voeren.

Er wordt naar rechts geschakeld wanneer M1 actief is, zoals aangegeven door de 1 in C3/1-pijl .

De CD4021B is een soortgelijk onderdeel, behalve voor het asynchrone parallel laden van gegevens zoals geïmpliceerd door het ontbreken van een 2 voorvoegsel in het gegevenslabel 1D voor pinnen P1, P2 tot P8.

Natuurlijk, prefix 2 in label 2D bij invoer SER zegt dat de gegevens in deze pin worden geklokt. De OF gate-inzet laat zien dat de klok wordt bestuurd door LD/SH' .

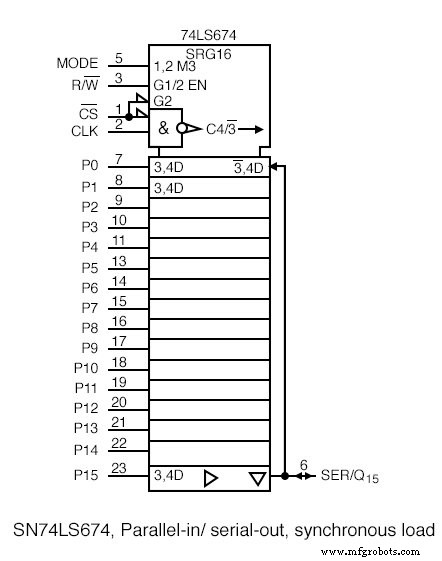

Het bovenstaande SN74LS674 interne label SRG 16 geeft 16-bits schuifregister aan.

De MODUS invoer naar de bedieningssectie bovenaan het symbool is gelabeld 1,2 M3 . Interne M3 is een functie van invoer MODE en G1 en G2 zoals aangegeven door de 1,2 voorafgaand aan M3 .

Het basislabel G geeft een EN . aan functie van een dergelijke G ingangen. Invoer R/W' is intern gelabeld G1/2 EN .

Dit is een enable EN (gecontroleerd door G1 EN G2 ) voor tristate-apparaten die elders in het symbool worden gebruikt.

We merken op dat CS' aan (pin 1) is intern G2 . Chipselectie CS' ook is EN ed met de invoer CLK om interne klok C4 te geven .

De bel in de klokpijl geeft aan dat de activiteit zich op de negatieve (overgang van hoog naar laag) van de klok bevindt.

De schuine streep (/) is een scheidingsteken dat twee functies voor de klok impliceert. Voor de schuine streep, C4 geeft controle aan over alles met het voorvoegsel 4 .

Na de schuine streep, de 3' (pijl) geeft aan dat het verschuift. De 3’ van C4/3' impliceert schakelen wanneer M3 niet wordt bevestigd (MODE=0 ). De lange pijl geeft verschuiving naar rechts (omlaag) aan.

Als we naar beneden gaan onder het besturingsgedeelte naar het gegevensgedeelte, hebben we externe ingangen P0-P15 , pinnen (7-11, 13-23).

Het voorvoegsel 3,4 van intern label 3,4D geeft aan dat M3 en de klok C4 controle laden van parallelle gegevens.

De D staat voor Gegevens. Dit label wordt verondersteld van toepassing te zijn op alle parallelle ingangen, maar is niet expliciet uitgeschreven.

Zoek het label 3’,4D aan de rechterkant van de P0 (pin7) podium. De aangevulde-3 geeft aan datM3=MODE=0 ingangen (ploegen) SER/Q15 (pin5) op kloktijd, (4 van 3’,4D) overeenkomend met klok C4 .

Met andere woorden, met MODE=0 , we verplaatsen gegevens naar Q0 van de seriële ingang (pin 6). Alle andere trappen verschuiven naar rechts (omlaag) op kloktijd.

Als u naar de onderkant van het symbool gaat, geeft de driehoek die naar rechts wijst een buffer aan tussen Q en de uitvoerpin.

De naar beneden wijzende driehoek duidt op een apparaat met drie toestanden. We hebben eerder aangegeven dat de tristate wordt bestuurd door enable EN , wat eigenlijk G1 AND G2 . is vanuit het bedieningsgedeelte.

Als R/W=0 , de drie-status is uitgeschakeld en we kunnen gegevens verschuiven naar Q0 via SER (pin 6), een detail dat we hierboven hebben weggelaten. We hebben eigenlijk MODE=0, R/W’=0, CS’=0 . nodig

De interne logica van de SN74LS674 en een tabel met een samenvatting van de werking van de stuursignalen is beschikbaar via de link in de lijst met opsommingstekens, bovenaan de sectie.

Als R/W'=1 , de tristate is ingeschakeld, Q15 verschuift SER/Q15 (pin 6) en recirculeert naar de Q0 podium via de rechterhand draad naar 3’,4D .

We zijn ervan uitgegaan dat CS' laag was, wat ons klok C4/3' en G2 tot EN gaf staat de drie-staten.

Praktische toepassingen

Een toepassing van een parallel-in/serieel-uit schuifregister is het inlezen van gegevens in een microprocessor.

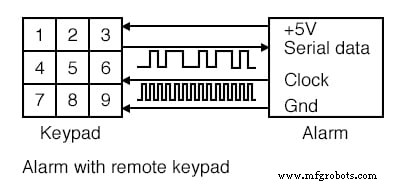

Het bovenstaande alarm wordt bestuurd door een afstandsbediening. De alarmbox levert +5V en aarde aan het externe toetsenbord om het van stroom te voorzien.

Het alarm leest het externe toetsenbord om de paar tientallen milliseconden door ploegenklokken naar het toetsenbord te sturen, die seriële gegevens retourneren die de status van de toetsen weergeven via een parallel-in/serieel-uit ploegregister.

Zo lezen we negen sleutelschakelaars met vier draden. Hoeveel draden zouden er nodig zijn als we voor elk van de negen sleutels een circuit moesten laten lopen?

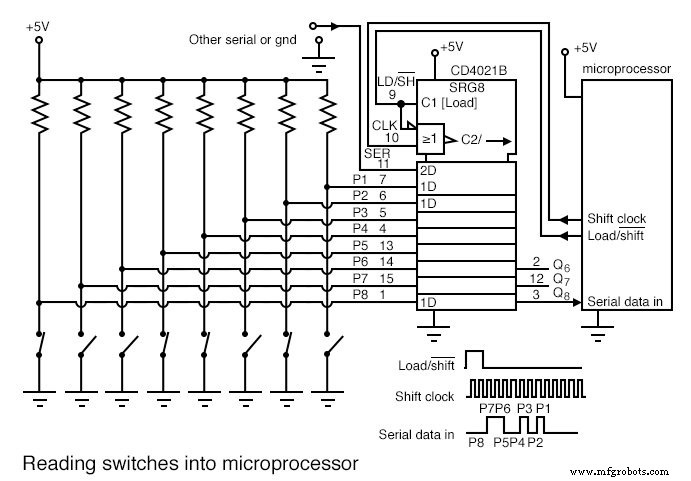

Een praktische toepassing van een parallel-in/serieel-uit schuifregister is het inlezen van veel schakelaarsluitingen in een microprocessor op slechts een paar pinnen.

Sommige low-end microprocessors hebben alleen 6-I/O (Input/Output)-pinnen beschikbaar op een 8-pins behuizing.

Of misschien hebben we de meeste pinnen op een 84-pins pakket gebruikt. Misschien willen we het aantal draden dat rond een printplaat, machine, voertuig of gebouw loopt verminderen.

Dit verhoogt de betrouwbaarheid van ons systeem. Er is gemeld dat fabrikanten die het aantal draden in een auto hebben verminderd, een betrouwbaarder product produceren.

In ieder geval zijn er slechts drie microprocessor-pinnen nodig om 8-bits gegevens van de schakelaars in de bovenstaande afbeelding in te lezen.

We hebben gekozen voor een asynchroon laadapparaat, de CD4021B, omdat het gemakkelijker is om het laden van gegevens te regelen zonder een enkele parallelle laadklok te hoeven genereren.

De parallelle data-ingangen van het schuifregister worden opgetrokken tot +5V met een weerstand op elke ingang.

Als alle schakelaars open zijn, alle 1 s worden in het schuifregister geladen wanneer de microprocessor de LD/SH' . verplaatst lijn van laag naar hoog en dan terug laag in afwachting van verschuiving.

Alle schakelaarsluitingen passen logica 0 . toe s naar de overeenkomstige parallelle ingangen. Het datapatroon op P1-P7 wordt parallel geladen door de LD/SH’=1 gegenereerd door de microprocessorsoftware.

De microprocessor genereert schuifpulsen en leest een databit voor elk van de 8 bits.

Dit proces kan volledig met software worden uitgevoerd, of grotere microprocessors kunnen een of meer seriële interfaces hebben om de taak sneller met hardware uit te voeren.

Met LD/SH'=0 , genereert de microprocessor een 0 tot 1 overgang op de Ploegenkloklijn , leest vervolgens een databit op de Seriële data in lijn. Dit wordt herhaald voor alle 8-bits.

De SER lijn van het schuifregister kan worden aangestuurd door een ander identiek CD4021B-circuit als er meer schakelcontacten moeten worden gelezen.

In dat geval genereert de microprocessor 16-shiftpulsen. Het is waarschijnlijker dat het wordt aangestuurd door iets anders dat compatibel is met dit seriële gegevensformaat, bijvoorbeeld een analoog-naar-digitaalomzetter, een temperatuursensor, een toetsenbordscanner, een serieel alleen-lezen geheugen.

Wat de sluitingen van schakelaars betreft, dit kunnen eindschakelaars zijn op het onderstel van een machine, een oververhittingssensor, een magnetische reed-schakelaar, een deur- of raamschakelaar, een lucht- of waterdrukschakelaar of een optische onderbreker in vaste toestand.

GERELATEERDE WERKBLAD:

- Werkblad Ploegregisters

Industriële technologie