Edge-triggered vergrendelingen:teenslippers

Tot nu toe hebben we zowel S-R- als D-latch-circuits bestudeerd met enable-ingangen. De grendel reageert alleen op de data-ingangen (S-R of D) als de vrijgave-ingang is geactiveerd. In veel digitale toepassingen is het echter wenselijk om het reactievermogen van een vergrendelingscircuit te beperken tot een zeer korte tijdsperiode in plaats van de gehele duur dat de activeringsingang wordt geactiveerd.

Een methode om een multivibratorcircuit in te schakelen, wordt edge-triggering genoemd , waarbij de data-ingangen van het circuit alleen controle hebben gedurende de tijd dat de enable-ingang overgang is van de ene staat naar de andere.

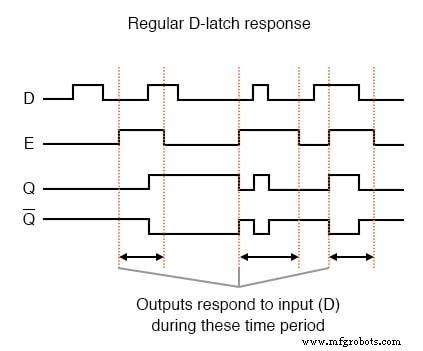

Laten we timingdiagrammen voor een normale D-latch vergelijken met een die edge-triggered is:

In het eerste timingdiagram reageren de uitgangen op ingang D wanneer de ingang (E) hoog is, hoe lang deze ook hoog blijft. Wanneer het activeringssignaal terugvalt naar een lage status, blijft het circuit vergrendeld.

In het tweede timingdiagram zien we een duidelijk andere respons in de circuituitgang(en):deze reageert alleen op de D-ingang gedurende dat korte moment waarop het activeringssignaal verandert , of overgangen , van laag naar hoog. Dit staat bekend als positief edge-triggering.

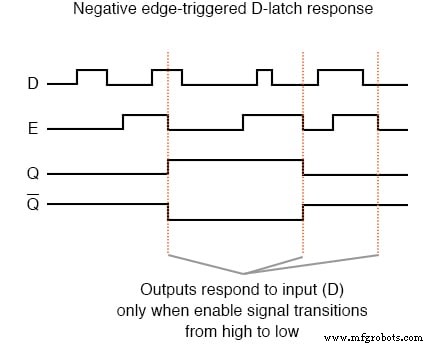

Er bestaat zoiets als negatief edge-triggering ook, en het produceert de volgende reactie op dezelfde ingangssignalen:

Telkens wanneer we een multivibratorcircuit inschakelen op de overgangsrand van een blokgolfactiveringssignaal, noemen we het een flip-flop in plaats van een vergrendeling .

Dientengevolge is een aan de rand getriggerd SR-circuit beter bekend als een SR-flip-flop, en een aan de rand getriggerd D-circuit als een D-flip-flop. Het activeringssignaal wordt hernoemd naar de klok signaal. We verwijzen ook naar de gegevensinvoer (respectievelijk S, R en D) van deze flip-flops als synchrone inputs, omdat ze alleen effect hebben op het moment van de klokpulsflank (overgang), waardoor eventuele outputveranderingen worden gesynchroniseerd met die klokpuls, in plaats van naar de grillen van de data-ingangen.

Maar hoe bereiken we deze edge-triggering eigenlijk? Een "gated" S-R-latch maken van een gewone S-R-latch is eenvoudig genoeg met een paar AND-poorten, maar hoe implementeren we logica die alleen aandacht besteedt aan de stijgende of dalende flank van een veranderend digitaal signaal?

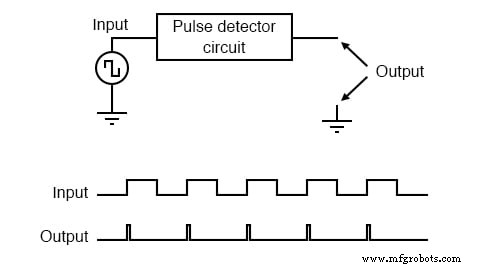

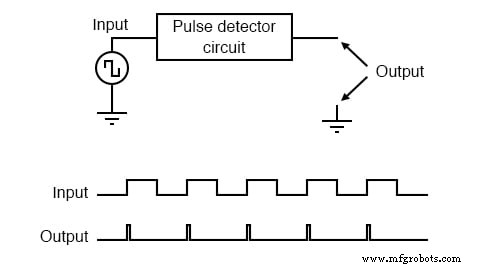

Wat we nodig hebben, is een digitaal circuit dat een korte puls afgeeft wanneer de ingang gedurende een willekeurige tijdsperiode wordt geactiveerd, en we kunnen de uitgang van dit circuit gebruiken om de grendel kort in te schakelen. We lopen hier een beetje voor op onszelf, maar dit is eigenlijk een soort monostabiele multivibrator, die we voorlopig een pulsdetector zullen noemen .

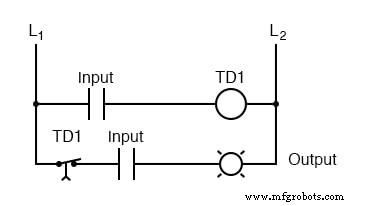

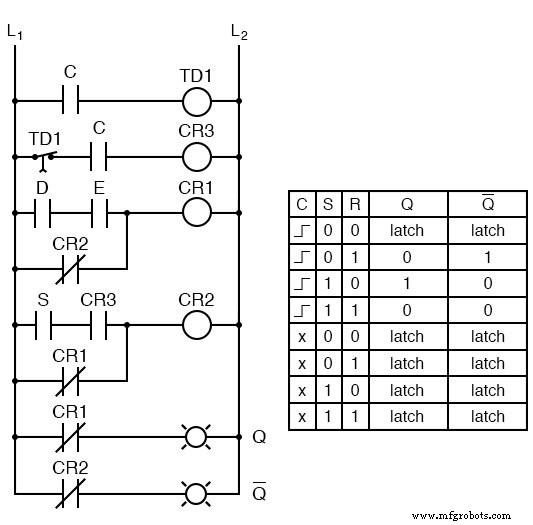

De duur van elke uitgangspuls wordt ingesteld door componenten in het pulscircuit zelf. In ladderlogica kan dit vrij eenvoudig worden bereikt door het gebruik van een tijdvertragingsrelais met een zeer korte vertragingstijd:

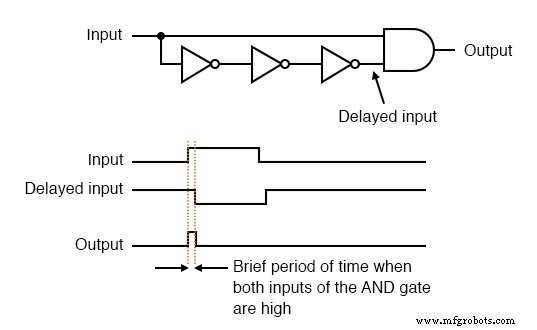

Het implementeren van deze timingfunctie met halfgeleidercomponenten is eigenlijk vrij eenvoudig, omdat het gebruik maakt van de inherente tijdvertraging binnen elke logische poort (bekend als voortplantingsvertraging ). Wat we doen is een ingangssignaal nemen en het op twee manieren splitsen, dan een poort of een reeks poorten in een van die signaalpaden plaatsen om het een beetje te vertragen, en dan laten zowel het originele signaal als zijn vertraagde tegenhanger een poort met twee ingangen die een hoog signaal afgeeft gedurende het korte moment dat het vertraagde signaal de verandering van laag naar hoog in het niet-vertraagde signaal nog niet heeft ingehaald. Een voorbeeldschakeling voor het produceren van een klokpuls bij een overgang van laag naar hoog ingangssignaal wordt hier getoond:

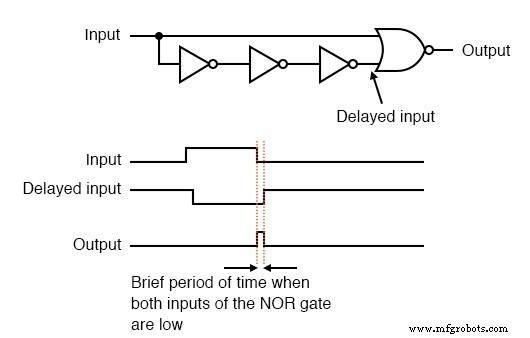

Dit circuit kan worden omgezet in een negatieve-flankpulsdetectorcircuit met alleen een verandering van de laatste poort van EN naar NOR:

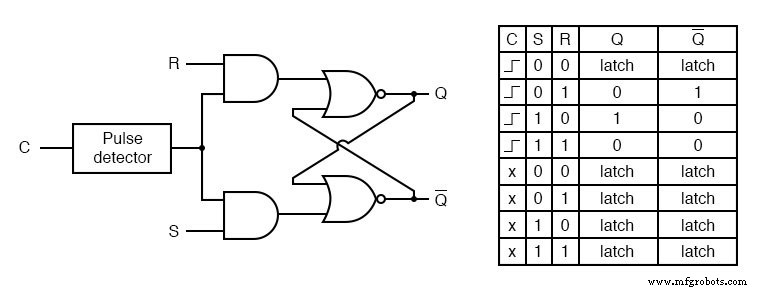

Nu we weten hoe een pulsdetector kan worden gemaakt, kunnen we laten zien dat deze is aangesloten op de activeringsingang van een grendel om er een flip-flop van te maken. In dit geval is de schakeling een SR-flip-flop:

Alleen wanneer het kloksignaal (C) van laag naar hoog overgaat, reageert het circuit op de S- en R-ingangen. Voor elke andere toestand van het kloksignaal ("x") wordt het circuit vergrendeld.

Een ladderlogica-versie van de SR-flip-flop wordt hier getoond:

Relaiscontact CR3 in het ladderdiagram neemt de plaats in van het oude E-contact in het SR-grendelcircuit en is alleen gesloten gedurende de korte tijd dat zowel C is gesloten als tijdvertragingscontact TR1 is gesloten. In beide gevallen (poort- of laddercircuit) zien we dat de ingangen S en R geen effect hebben tenzij C overgaat van een lage (0) naar een hoge (1) toestand. Anders blijven de uitgangen van de flip-flop in hun vorige toestanden hangen.

Het is belangrijk op te merken dat de ongeldige toestand voor de SR-flip-flop alleen wordt gehandhaafd gedurende de korte tijd dat het pulsdetectorcircuit de vergrendeling mogelijk maakt. Nadat die korte tijdsperiode is verstreken, worden de uitgangen vergrendeld in de ingestelde of de resetstatus. Nogmaals, het probleem van een rasconditie manifesteert zichzelf. Zonder vrijgavesignaal kan een ongeldige uitgangsstatus niet worden gehandhaafd. De geldige "vergrendelde" toestanden van de multivibrator - set en reset - sluiten elkaar echter uit. Daarom zullen de twee poorten van het multivibratorcircuit met elkaar "racen" om de suprematie, en degene die als eerste een hoge uitgangsstatus bereikt, zal "winnen".

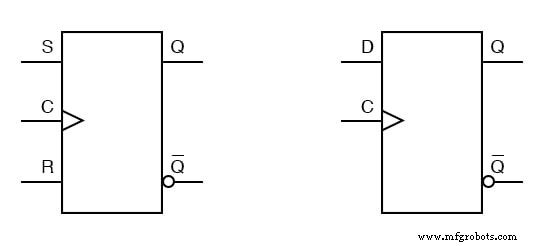

De bloksymbolen voor flip-flops verschillen enigszins van die van hun respectievelijke latch-tegenhangers:

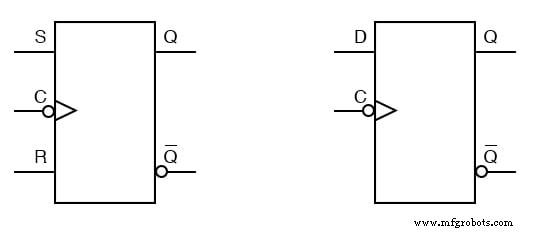

Het driehoeksymbool naast de klokingangen vertelt ons dat dit edge-triggered devices zijn, en dat dit dus flip-flops zijn in plaats van grendels. De symbolen hierboven zijn positieve flank-getriggerd:dat wil zeggen, ze "klokken" op de stijgende flank (van laag naar hoog) van het kloksignaal. Negatieve edge-triggered apparaten worden gesymboliseerd met een bel op de klokinvoerlijn:

Beide bovenstaande flip-flops "klokken" op de dalende flank (overgang van hoog naar laag) van het kloksignaal.

BEOORDELING:

- Een flip-flop is een vergrendelingscircuit met een "pulsdetector"-circuit aangesloten op de activeringsingang (E), zodat het slechts voor een kort moment wordt ingeschakeld bij ofwel de stijgende of dalende flank van een klokpuls.

- Pulsdetectorcircuits kunnen worden gemaakt van tijdvertragingsrelais voor ladderlogica-toepassingen, of van halfgeleiderpoorten (waarbij gebruik wordt gemaakt van het fenomeen voortplantingsvertraging ).

GERELATEERDE WERKBLAD:

- Werkblad Flip Flops

Industriële technologie