CXL 2.0 /PCIe 5.0-oplossingen ontsluiten heterogene compute- en dataknelpunten

Fabless semiconductor startup Astera Labs heeft een nieuwe, speciaal gebouwde CXL 2.0- en PCIe 5.0-connectiviteitsoplossingen aangekondigd om heterogene computerarchitecturen te ontgrendelen en latentiegevoelige workloads in het datacenter aan te pakken. Het bedrijf zei dat het doel van deze nieuwe oplossingen is om systeembrede prestatieknelpunten in datacentrische applicaties aan te pakken.

De wildgroei aan data en mainstreaming van gespecialiseerde workloads - zoals kunstmatige intelligentie (AI) en machine learning (ML) - vereisen dat speciaal gebouwde accelerators zij aan zij werken met universele CPU's op hetzelfde moederbord of binnen hetzelfde rack, terwijl het delen van een gemeenschappelijke geheugenruimte. CXL 2.0-interconnect is essentieel om dergelijke coherente cachesysteemtopologieën mogelijk te maken.

Het eerste product in het nieuwe portfolio van Astera Labs is het Aries Compute Express Link (CXL 2.0) smart retimer-portfolio (PT5161LX, PT5081LX) voor CXL.io-connectiviteit met lage latentie, dat actief wordt getest bij strategische klanten. De CEO van het bedrijf, Jitendra Mohan, zei:"Met onze uitbreiding naar het CXL-ecosysteem neemt Astera Labs opnieuw een grote sprong om speciaal gebouwde oplossingen te bieden die complexe heterogene computer- en configureerbare desaggregatiesysteemtopologieën ontsluiten."

De CXL 2.0-specificatie is in november 2020 vrijgegeven door het CXL Consortium. CXL is een open industriestandaard interconnect die coherentie en geheugensemantiek biedt met behulp van hoge bandbreedte, lage latentieconnectiviteit tussen hostprocessor en apparaten zoals versnellers, geheugenbuffers en slimme I/O-apparaten. De CXL 2.0-specificatie voegt ondersteuning toe voor schakelen voor fan-out om verbinding te maken met meer apparaten; geheugenpooling voor een efficiënter geheugengebruik en het leveren van geheugencapaciteit op aanvraag; en ondersteuning voor persistent geheugen. Dit alles met behoud van industriële investeringen door volledige achterwaartse compatibiliteit met CXL 1.1 en 1.0 te ondersteunen.

De president van het CXL Consortium, Barry McAuliffe, zei:"Als vroeg lid van het CXL Consortium heeft Astera Labs zijn connectiviteitsexpertise bijgedragen aan de vooruitgang van de CXL-standaard. Het is geweldig om te zien dat de eerste CXL-siliciumimplementatie op de markt komt ter ondersteuning van een snelgroeiend CXL-ecosysteem.”

Nieuwe PCIe 5.0-oplossingen in samenwerking met Intel

Astera Labs kondigde ook de beschikbaarheid aan van een nieuwe lage latentiemodus in zijn Aries smart retimer-portfolio voor PCIe-connectiviteit met schaalbare Intel Xeon-processors. Deze ontwikkeling was het resultaat van een nauwe samenwerking met Intel Corporation om de latentie in PCIe-koppelingen verder te verminderen tot sub-10ns en de prestaties in datacentrische workloads te verbeteren. Astera Labs beweerde dat het de eerste leverancier is die robuuste PCIe 5.0-interoperabiliteit demonstreert met Intel Xeon Scalable-processors met de codenaam 'Sapphire Rapids'.

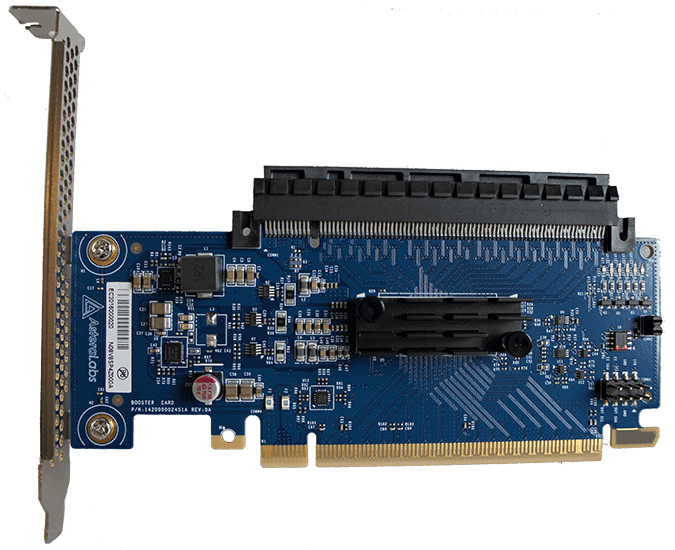

Tegelijkertijd werd ook een nieuwe plug-and-play Smart retimer add-in-kaart voor PCIe/CXL-toepassingen gelanceerd, Equinox genaamd. De kaart en de bijbehorende speciaal gebouwde firmware, ook ontwikkeld in samenwerking met Intel, zullen de ontwikkeling van PCIe 5.0-systemen vereenvoudigen met Intel's nieuwste Xeon Scalable-processors. Dit vertegenwoordigt de overgang van Astera Labs om gebruiksvriendelijke plug-and-play-kaarten aan te bieden om snel complexe systeemtopologieën te implementeren.

"PCIe Gen5 en CXL zijn fundamentele technologieën voor heterogene computerworkloads en datacenterarchitecturen van vandaag en morgen", zegt Zane Ball, corporate VP en general manager voor datacenterengineering en architectuur bij Intel. "Intel werkt samen met ecosysteemleiders zoals Astera Labs om de PCIe- en CXL-interconnectlatentie aanzienlijk te verminderen op het aankomende Intel Xeon Scalable-platform met de codenaam 'Sapphire Rapids' en aanvullende platforms."

Verwante inhoud:

- USB4 opnieuw timen via USB-C

- High-performance interconnects bouwen met meerdere PCIe-generaties

- Xilinx richt zich op de offload van datacenters met 'composable' hardware

- Hoe edge-supercomputing de grote datastroom zal transformeren

Ingebed

- Juridische problemen in cloud computing en hun oplossingen

- DATA MODUL:klantgerichte digital signage-oplossingen te zien op ISE

- Microchip:klokbuffers voldoen aan de DB2000Q/QL-standaarden plus PCIe Gen 4 en 5 lage jitter-specificaties

- Apacer:PCIe NVMe Gen3 SSD's, de volgende logische stap voor industriële opslag

- Swissbit:op hardware gebaseerde beveiligingsoplossingen om gegevens en apparaten te beschermen

- TECHWAY:Kintex-7 FPGA PCIe-platform om de gegevenssnelheid te verbeteren met 12 HSS-links

- De strategie en oplossingen van het leger voor op conditie gebaseerd onderhoud

- De voordelen van het aanpassen van IIoT- en data-analyseoplossingen voor EHS

- Overstromingen in stedelijke gebieden bestrijden met IoT-netwerkoplossingen

- Hoe het internet der dingen de toeleveringsketen transformeert:deel 2, toekomstige oplossingen

- Elektronisch ontwerp maakt gebruik van AI-oplossingen om hoogwaardige service te leveren