Nieuwe op ML gebaseerde tool biedt geautomatiseerde optimalisatie van de chipontwerpstroom

Het staat buiten kijf dat het chipontwerp steeds complexer wordt omdat klanten meer functies en kleinere apparaten en een lager stroomverbruik eisen. Om aan deze vraag te voldoen, raken ingenieurs overbelast en hebben ze ondersteuning nodig om de vraag bij te houden en tijdige productontwikkeling.

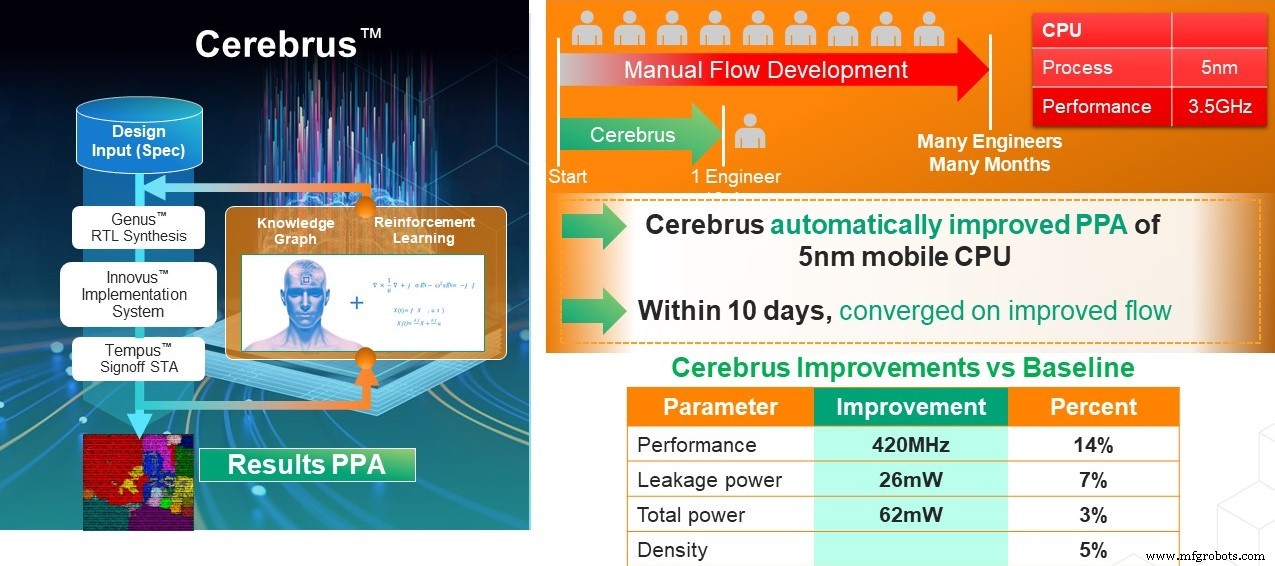

Om dit aan te pakken, heeft Cadence Design Systems een nieuwe tool geïntroduceerd die gebruikmaakt van machine learning (ML) om de Cadence RTL-naar-ondertekening implementatiestroom te stimuleren, wat levert wat het zei is tot 10X productiviteit en 20% PPA (vermogen, prestaties en oppervlakte ) verbeteringen voor implementatie. De nieuwe Cerebrus Intelligent Chip Explorer biedt efficiëntere on-site en cloud computing resource management-mogelijkheden dan traditionele, door mensen aangestuurde ontwerpverkenning; en verbetert de PPA en productiviteit op veel knooppunten en meerdere eindtoepassingen, waaronder consumenten-, hyperscale computing, 5G-communicatie, automotive en mobiel ontwerp.

In een briefing met embedded.com zei Rod Metcalfe, groepsdirecteur productbeheer bij Cadence:"Dit is de eerste full-flow digitale optimalisatietool die ML gebruikt. Dit is belangrijk, aangezien de complexiteit van het ontwerp toeneemt, chipontwerp meer functies en intelligentie vereist, maar er is een beperking op het aantal beschikbare ingenieurs om deze taken uit te voeren. We zien ontwerpers nog steeds handmatige flow-ontwikkeling doen en de lus doorlopen om hun ontwerpdoelen te bereiken:dit vereist een enorme hoeveelheid engineering-inspanning en is niet schaalbaar. Dat is waar Cerebrus om de hoek komt kijken, met behulp van enorme rekenkracht om de productiviteit voor ontwerpautomatisering te verbeteren.”

Metcalfe benadrukte een voorbeeld waarbij Cerebrus slechts één ingenieur nodig had om binnen 10 dagen samen te komen tot een verbeterde ontwerpstroom om automatisch de PPA van een 5nm mobiele CPU te verbeteren (zie onderstaande afbeelding).

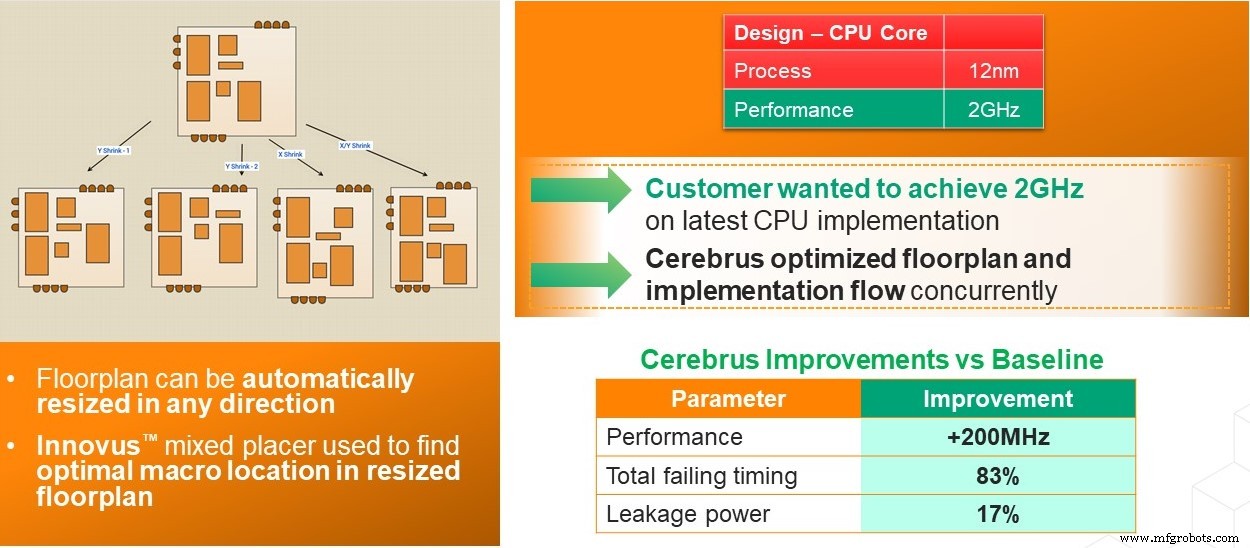

Een ander voorbeeld op een hoger niveau is geautomatiseerde optimalisatie van de plattegrond, zoals in de onderstaande afbeelding:

De impact van het gebruik van een op ML gebaseerde tool zoals Cerebrus is dat ontwerpteams een geautomatiseerde manier hebben om historische ontwerpkennis opnieuw te gebruiken - voorheen zouden ze bij elk nieuw project teveel tijd hebben besteed aan handmatig opnieuw leren. Vandaar dat Cadence zei dat Cerebrus een EDA-industrierevolutie markeert met ML-gestuurd digitaal chipontwerp, waarbij engineeringteams een grotere kans hebben om een grotere impact in hun organisaties te bieden, omdat ze handmatige processen kunnen ontlasten. Naarmate de industrie steeds meer overstapt naar geavanceerde knooppunten en de grootte en complexiteit van het ontwerp toenemen, zal Cerebrus ontwerpers helpen om PPA-doelen efficiënter te bereiken.

De eerste aanbevelingen van klanten voor de tool kwamen van Renesas en Samsung Foundry.

Satoshi Shibatani, directeur van de afdeling digitale ontwerptechnologie van de gedeelde R&D EDA-divisie van Renesas, zei:"Om de prestaties van nieuwe producten die gebruikmaken van opkomende procesknooppunten efficiënt te maximaliseren, moeten de digitale implementatiestromen die door ons engineeringteam worden gebruikt, voortdurend worden bijgewerkt. Geautomatiseerde ontwerpstroomoptimalisatie is van cruciaal belang voor het realiseren van productontwikkeling met een veel hogere doorvoer. Cerebrus, met zijn innovatieve ML-mogelijkheden en de Cadence RTL-to-signoff-tools, hebben gezorgd voor geautomatiseerde stroomoptimalisatie en plattegrondverkenning, waardoor de ontwerpprestaties met meer dan 10% zijn verbeterd.”

Ondertussen zei Sangyun Kim, vice-president voor ontwerptechnologie bij Samsung Foundry:"Terwijl we up-to-date procesknooppunten blijven implementeren, is de efficiëntie van ons programma voor co-optimalisatie van ontwerptechnologie (DTCO) erg belangrijk. . Als onderdeel van onze langdurige samenwerking met Cadence heeft Samsung Foundry Cerebrus en de Cadence digitale implementatiestroom voor meerdere applicaties gebruikt. We hebben in slechts een paar dagen tijd meer dan 8% stroomvermindering waargenomen op enkele van onze meest kritieke blokken, vergeleken met vele maanden handmatige inspanning. Daarnaast gebruiken we Cerebrus voor de geautomatiseerde dimensionering van stroomdistributienetwerken, wat heeft geresulteerd in een meer dan 50% betere timing van het uiteindelijke ontwerp.

De belangrijkste kenmerken en voordelen van Cerebrus zijn:

- Versterking ML : vindt snel flow-oplossingen die menselijke ingenieurs misschien niet van nature proberen of verkennen, waardoor PPA en productiviteit worden verbeterd.

- Hergebruik van ML-model :maakt het mogelijk om geleerde ontwerpen automatisch toe te passen op toekomstige ontwerpen, waardoor er minder tijd nodig is voor betere resultaten.

- Verbeterde productiviteit :laat een enkele ingenieur de volledige RTL-naar-GDS-stroom automatisch optimaliseren voor veel blokken tegelijk, waardoor volledige ontwerpteams productiever kunnen zijn.

- Enorm gedistribueerd computergebruik :biedt schaalbare ontwerpverkenning op locatie of in de cloud voor snellere stroomoptimalisatie.

- Eenvoudig te gebruiken interface: krachtige gebruikerscockpit maakt interactieve resultatenanalyse en runbeheer mogelijk om waardevolle inzichten in ontwerpstatistieken te krijgen.

Cerebrus maakt deel uit van de bredere digitale volledige stroom van Cadence en werkt naadloos samen met de Genus-syntheseoplossing, het Innovus-implementatiesysteem, de Tempus-timingsignoff-oplossing, de Joules RTL-stroomoplossing, de Voltus IC-stroomintegriteitsoplossing en het Pegasus-verificatiesysteem om klanten een snel pad te bieden om afsluiting en betere voorspelbaarheid te ontwerpen.

Ingebed

- Op naar een nieuw niveau van Edge AI

- Pulsic biedt realtime analoge chiplay-outvoorbeelden in schematische editor

- Project onderzoekt betrouwbare ontwerp- en verificatiestroom voor IoT-beveiliging

- SIMULIA Tyre Engineering en Design

- Pennsylvania biedt nieuwe financiering om studenten uit Philadelphia te helpen kansen in productie te ontdekken

- Ontwerptechniek van op maat gemaakte preforms

- Bar/Chucker met open ontwerp en meer

- Nieuw transistorontwerp verhult belangrijke computerchiphardware ter bescherming tegen hackers

- Sandvik introduceert nieuw draaiconcept

- Het nieuwe lijnintegratielandschap

- Nieuw gereedschap toevoegen