Ondertekend versus niet-ondertekend in VHDL

Alle digitale ontwerpers moeten begrijpen hoe wiskunde werkt in een FPGA of ASIC. De eerste stap daarvoor is begrijpen hoe ondertekende en niet-ondertekende signaaltypen werken. Ondertekende en niet-ondertekende typen bestaan in de numeric_std pakket, dat deel uitmaakt van de ieee-bibliotheek. Opgemerkt moet worden dat er een ander pakketbestand is dat vaak wordt gebruikt om wiskundige bewerkingen uit te voeren:std_logic_arith . Std_logic_arith is echter geen officieel door ieee ondersteund pakketbestand en wordt niet aanbevolen voor gebruik in digitale ontwerpen.

Een signaal dat is gedefinieerd als type ondertekend betekent dat de tools dit signaal als positief of negatief interpreteren. Een signaal dat is gedefinieerd als type unsigned betekent dat het signaal alleen positief zal zijn. Intern zal de FPGA gebruik maken van Two's Complement vertegenwoordiging. Een 3-bits signaal kan bijvoorbeeld worden geïnterpreteerd volgens de onderstaande tabel:

Ben je al in de war? Dat zou je moeten zijn, dit is niet intuïtief! Laten we eens kijken naar een voorbeeld dat hopelijk duidelijkheid zal scheppen. Het onderstaande bestand test hoe ondertekend niet-ondertekend werkt. Wat moet worden begrepen, is dat of de signalen al dan niet als ondertekend of niet-ondertekend zijn gedefinieerd, niet beïnvloeden hoe de eigenlijke binaire wiskunde wordt uitgevoerd.

Bijvoorbeeld:voor twee ondertekende vectoren 10001 + 00010 is het antwoord nog steeds 10011, MAAR het is de interpretatie van het resultaat dat anders is.

Voor de niet-ondertekende casus staat het antwoord (10011) voor 19.

Voor de ondertekende casus staat het antwoord (10011) voor -13.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity signed_unsigned is

port (

i_rst_l : in std_logic;

i_clk : in std_logic;

i_a : in std_logic_vector(4 downto 0);

i_b : in std_logic_vector(4 downto 0)

);

end signed_unsigned;

architecture behave of signed_unsigned is

signal rs_SUM_RESULT : signed(4 downto 0) := (others => '0');

signal ru_SUM_RESULT : unsigned(4 downto 0) := (others => '0');

signal rs_SUB_RESULT : signed(4 downto 0) := (others => '0');

signal ru_SUB_RESULT : unsigned(4 downto 0) := (others => '0');

begin

-- Purpose: Add two numbers. Does both the signed and unsigned

-- addition for demonstration. This process is synthesizable.

p_SUM : process (i_clk, i_rst_l)

begin

if i_rst_l = '0' then -- asynchronous reset (active low)

rs_SUM_RESULT <= (others => '0');

ru_SUM_RESULT <= (others => '0');

elsif rising_edge(i_clk) then

ru_SUM_RESULT <= unsigned(i_a) + unsigned(i_b);

rs_SUM_RESULT <= signed(i_a) + signed(i_b);

end if;

end process p_SUM;

-- Purpose: Subtract two numbers. Does both the signed and unsigned

-- subtraction for demonstration. This process is synthesizable.

p_SUB : process (i_clk, i_rst_l)

begin

if i_rst_l = '0' then -- asynchronous reset (active low)

rs_SUB_RESULT <= (others => '0');

ru_SUB_RESULT <= (others => '0');

elsif rising_edge(i_clk) then

ru_SUB_RESULT <= unsigned(i_a) - unsigned(i_b);

rs_SUB_RESULT <= signed(i_a) - signed(i_b);

end if;

end process p_SUB;

end behave;

Testbank:

library ieee;

use ieee.std_logic_1164.all;

entity example_signed_unsigned_tb is

end example_signed_unsigned_tb;

architecture behave of example_signed_unsigned_tb is

--Registers

signal r_CLK : std_logic := '0';

signal r_RST_L : std_logic := '0';

signal r_A : natural := 0;

signal r_B : natural := 0;

signal r_A_SLV : std_logic_vector(4 downto 0) := (others => '0');

signal r_B_SLV : std_logic_vector(4 downto 0) := (others => '0');

constant c_CLK_PERIOD : time := 10 ns;

component example_signed_unsigned is

port (

i_rst_l : in std_logic;

i_clk : in std_logic;

i_a : in std_logic_vector(4 downto 0);

i_b : in std_logic_vector(4 downto 0)

);

end component example_signed_unsigned;

begin

i_DUT: example_signed_unsigned

port map (

i_rst_l => r_RST_L,

i_clk => r_CLK,

i_a => r_A_SLV,

i_b => r_B_SLV

);

clk_gen : process is

begin

r_CLK <= '0' after c_CLK_PERIOD/2, '1' after c_CLK_PERIOD;

wait for c_CLK_PERIOD;

end process clk_gen;

process

begin

r_RST_L <= '0';

wait for 20 ns;

r_RST_L <= '1';

wait for 20 ns;

r_A_SLV <= "01001";

r_B_SLV <= "00110";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00110";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00001";

wait for 20 ns;

r_A_SLV <= "10001";

r_B_SLV <= "00010";

wait for 20 ns;

r_A_SLV <= "11111";

r_B_SLV <= "00001";

wait for 20 ns;

r_A_SLV <= "00000";

r_B_SLV <= "00001";

wait for 20 ns;

wait;

end process;

end behave;

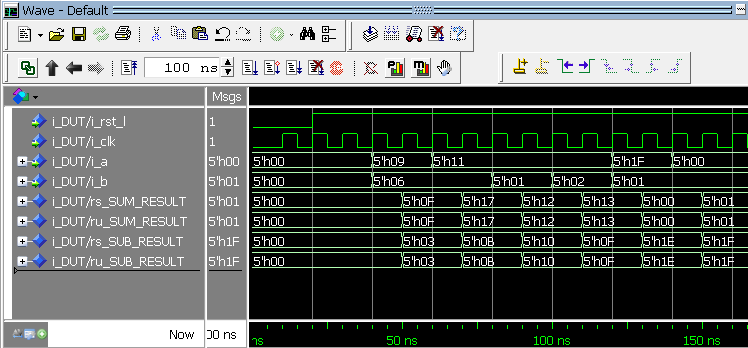

Modelsim-simulatiegolfuitvoer Waarden weergegeven in HEX

Modelsim-simulatiegolfuitvoer Waarden weergegeven in HEX

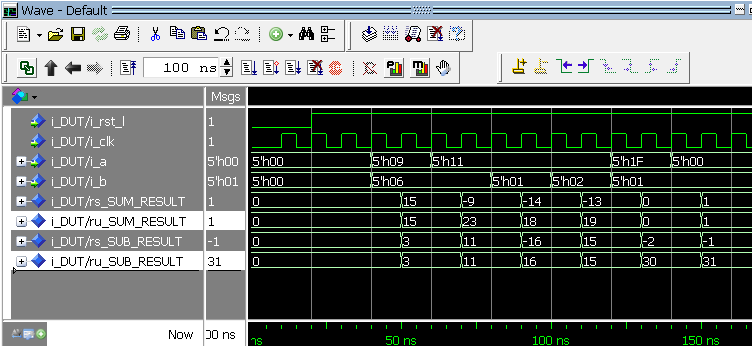

Modelsim-simulatiegolfuitvoer Waarden weergegeven in DECIMAL

Modelsim-simulatiegolfuitvoer Waarden weergegeven in DECIMAL Vergelijk de twee bovenstaande screenshots van modelsim. In de eerste kun je zien dat de resultaten van de wiskundige functies zijn precies hetzelfde wanneer ze worden weergegeven in hex. Het is de interpretatie van de resultaten is dat anders. Dit is te zien door naar de onderste schermafbeelding te kijken. Wanneer Modelsim de resultaten in decimalen weergeeft, interpreteert het sommige ervan als negatieve getallen. Bij het gebruik van ondertekende en niet-ondertekende typen moet u zeer voorzichtig zijn! Hopelijk begrijp je dit onderwerp een beetje beter. Ik heb het gevoel dat dit een gebied is waar veel digitale ontwerpers mee worstelen, dus als er iets is dat je niet volledig begrijpt, stuur me dan een e-mail via de contactlink in de zijbalk en ik zal proberen het duidelijker te maken.

VHDL

- Zelfstudie - Inleiding tot VHDL

- Voorbeelden van VHDL-conversies

- Procedureverklaring - VHDL-voorbeeld

- Records - VHDL-voorbeeld

- Variabelen - VHDL-voorbeeld

- Stroomsignaalsystemen

- Verkeerssignaal

- LoRa-lokalisatie

- Formele verificatie in VHDL met PSL

- Een lijst met strings maken in VHDL

- Signaalintegriteit &PCB