Op weg naar 7nm

Dit is de vierde van een vierdelige serie over IBM-papers op IEDM 2016.

De jaarlijkse International Electron Devices Meeting is "'s werelds meest vooraanstaande forum voor het rapporteren van technologische doorbraken op het gebied van halfgeleider- en elektronische apparaattechnologie, ontwerp, fabricage, fysica en modellering." Dus IBM-onderzoekers brachten hun scansonde-thermometer, hun luchtafstandsstuk voor een 10 nanometer-chip, hun 7 nm-chip, en om niet te worden overtroffen door silicium, brachten ze ook hun koolstofnanobuisjes mee. Deze papers en presentaties van IBMers en vele partners zullen deze week deelnemen aan de conferentie in San Francisco.

IEDM bevat vier IBM-papers als enkele van de beste voorbeelden van de conferentie van deze herinterpretatie van computergebruik:het uitbreiden van de wet van Moore, het bouwen van nieuwe architecturen en het gebruik van nieuwe materialen om verder te gaan. Hier is een nadere blik op deze artikelen en de wetenschappers achter het werk. De laatste aflevering van de serie belicht het artikel "A 7nm FinFET Technology featuring EUV Patterning and Dual-Strained High-Mobility Channels", door Ruilong Xie, een senior lid van de technische staf van GlobalFoundries, en leden van IBM's team in het Albany Nanotech Center .

Afgelopen juli kondigden IBM en zijn Alliance-partners aan dat ze 's werelds eerste 7nm node-testchips hadden ontwikkeld. De doorbraak kwam door het toepassen van Extreme Ultaviolet (EUV) Lithografie – een techniek waarbij licht gebruikt wordt om patronen in andere materialen te etsen – en het gebruik van Silicium Germanium (SiGe) als kanaalmateriaal in de transistor.

Van silicium tot siliciumgermanium

De IEDM-paper van het team laat zien dat "SiGe-gebaseerde FinFET-technologie prestatieverbetering heeft aangetoond met 10nm-technologiebasisregels (industrienormen), wat elegante oplossingen biedt voor een levensvatbare CMOS-technologieoptie. Een van die elegante oplossingen is het toestaan van apparaten met een laag vermogen en hoge prestaties op dezelfde chip - zonder prestatieverlies of variabiliteit van het ene type apparaat ten opzichte van het andere", zoals uitgelegd in Materiële innovatie tot 7nm .

Verder verlegt SiGe de grenzen van chipscaling door de manier te veranderen waarop stroom door het kanaal van een transistor gaat. Het blijkt dat door grotere germaniumatomen toe te voegen aan een kristal gemaakt van kleinere siliciumatomen, het kristal een roostermismatch ontwikkelt, waardoor spanning in het transistorkanaal ontstaat. Deze spanning maakt het mogelijk om bij lagere spanningen meer stroom door het kanaal te verplaatsen. Dus door SiGe als kanaalmateriaal te gebruiken in combinatie met innovaties op het gebied van parasitaire weerstand en capaciteitsvermindering, kon het team een routekaart naar een 7nm-chip uitstippelen, met behoud van een balans tussen vermogen en prestatie - een prestatie bij constant vermogen die, zoals gepresenteerd op IEDM , 40 procent beter dan een 10nm-chip!

Extreem kleine golflengten van licht

Het licht dat wordt gebruikt, met een golflengte van slechts 13,5 nm, is veel korter dan het huidige standaardlicht met een golflengte van 193 nm, waardoor het in staat is 20 miljard transistors van 7 nm op een chip te etsen. Maar voordat het team zoveel schakelaars op een chip kan zetten, moeten ze de technologie achter het gebruik van zo'n korte golflengte tot een consistent, gecontroleerd en herhaalbaar proces maken.

Om chips te maken met behulp van lithografie, wordt een wafel blootgesteld aan een lichtpatroon op dezelfde manier als alle niet-digitale fotonegatieven worden afgedrukt op contactpapier - het wordt boven de wafel gehouden en licht wordt door een masker geleid (het 'negatief') . De grootte van de lijnen en draden die met deze techniek kunnen worden afgedrukt, weerspiegelen niet alleen de grootte van de lijnen op het masker, maar ook de golflengte van het gebruikte licht. Tegenwoordig kan een wafel met 193 nm-licht meerdere keren worden belicht als het benodigde patroon kleiner is dan wat 193 nm op zichzelf kan leveren.

Dus, net als bij het afdrukken op Japanse houtsneden, wordt patroon na patroon gelaagd op de wafel om een meer ingewikkelde - en kleinere - chip te krijgen. Deze techniek met meerdere patronen veroorzaakt echter degradatie; wat misschien niet zo'n kritiek probleem is voor chips in massaproductie-apparaten zoals smartphones, maar een belangrijke wegversperring is voor supercomputers en gespecialiseerde systemen die een zeer hoge betrouwbaarheid vereisen. En hoewel het technisch mogelijk is om op deze manier 7 nm-chips te maken, is het een belangrijke reden waarom IBM heeft besloten te onderzoeken hoe 7 nm-chips kunnen worden gemaakt met EUV-technologie.

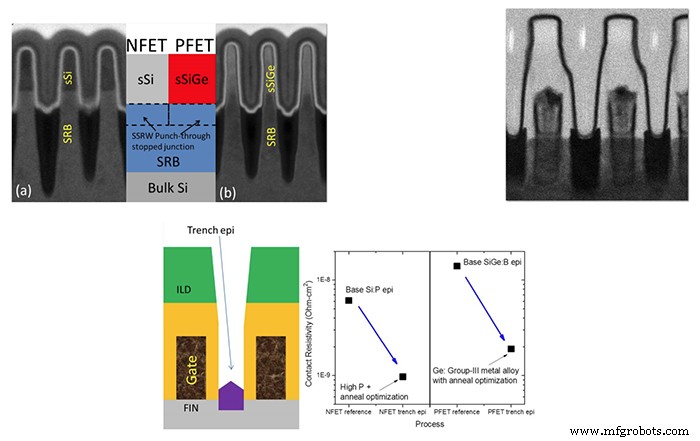

Linksboven: Een schematische beschrijving van dual-stressed kanaalmaterialen op de SRB met een supersteile retrograde well (SSRW), samen met TEM-afbeeldingen van (a) de trekgespannen siliciumvin en (b) de samendrukkend gespannen SiGe-vin op een gemeenschappelijke SRB. Rechtsboven: Een TEM-beeld van een 48nm gecontacteerd polysilicium pitch-apparaat met een geoptimaliseerd zelf-uitgelijnd contact met een contactopening van ~10nm en Lmetaal van ~15nm. Midden onder: illustratie en grafiek laten zien dat het epitaxiale proces van de sleuf tegelijkertijd voldoet aan de basisregels en vermindering van de contactweerstand na implantatie- en anneal-optimalisaties.

Met 13,5 nm EUV is slechts één high-fidelity-patroon nodig om een enkel patroon op een 7 nm-chip af te drukken. De uitdaging voor EUV is hoe de technologie te rijpen om klaar te zijn voor productie. Net zoals de IBM System 360, gebouwd in 1964, leidde tot de kleinere, snellere machines van vandaag door verfijning, schaalvergroting en technische inspanningen, zo zal EUV op een vergelijkbare manier moeten rijpen.

Overweeg dit:om 13,5 nm licht te genereren, laat het EUV-apparaat een druppel gesmolten tin vrij in een vacuüm (om een bolvorm te krijgen) die vervolgens wordt geraakt met een koolstofdioxidelaser die het vlak maakt en naar een specifieke hoek verplaatst. Het tin, dat nog steeds valt, wordt vervolgens geraakt - en verdampt - met een andere krachtigere koolstofdioxidelaser om 13,5 nm-licht vrij te geven, dat vervolgens wordt opgevangen en gefocust op een wafel met behulp van gespecialiseerde spiegels.

Hoewel het proces om dit 13,5 nm-licht te gebruiken ingewikkeld is, bewijst het werk van het team dat het mogelijk is om een 7 nm-chip met EUV te maken en resultaten van hoge kwaliteit te leveren. Wat zou moeten betekenen dat gespecialiseerde, zeer betrouwbare chips voor toekomstige high-performance systemen kunnen worden vervaardigd om te voldoen aan de eisen van de volgende generatie supercomputers en systemen.

Lees deel één:hotspots in kaart brengen

Lees deel twee:Een ander soort chip met koolstofnanobuisjes

Lees deel drie:Luchtafstandhouders voor 10nm-chips

Nanomaterialen

- 5 voordelen van het gebruik van kunststof scharnieren

- C# met behulp van

- Bewegingssensor met Raspberry Pi

- Vooruitgang in halfgeleidertechnologie, één nanometer per keer

- Miniatuur long-hartsensor op een chip

- 3 voordelen van het gebruik van een boorfrees

- Voordelen van het gebruik van legeringen

- Wat zijn spaantransporteurs?

- Een inleiding tot spaantransporteurs

- Wat is een magnetische chiptransporteur?

- Een frees als draaibank gebruiken