DSP-activering begrijpen met behulp van de i.MX RT500 Crossover MCU van NXP

Meer informatie over multi-threaded programma's, het ontwikkelen van applicaties met het XOS real-time besturingssysteem, het delen van bronnen met semaforen en hoe de i.MX RT500-familie van NXP van microcontrollers helpen ingenieurs bij het ontwerpen van slimme apparaten met DSP-functionaliteit.

De huidige slimme consumentenapparaten hebben componenten nodig die grote hoeveelheden gegevens kunnen verwerken om te voldoen aan de eisen van verschillende beveiligings- en signaalverwerkingstoepassingen. Deze componenten (inclusief microcontrollers) moeten die gegevens snel en efficiënt kunnen verwerken, waarvoor sterk geoptimaliseerde digitale signaalprocessors nodig zijn.

Dit artikel introduceert enkele kenmerken van de Cadence® Tensilica® Fusion F1-audioprocessor, een aangewezen co-processor die de hoofd-CPU van de i.MX RT500 MCU helpt bij het uitvoeren van signaalverwerkingsberekeningen.

Kernconcepten van programma's met meerdere threads

Op het eerste gezicht wekt moderne verwerkingshardware de illusie dat het veel threads tegelijk uitvoert. In werkelijkheid zorgt een enkele CPU-kern voor een enkele thread tegelijk. Wanneer het aantal threads het aantal beschikbare CPU-cores overschrijdt, is een besturingssysteem nodig om de threads te plannen.

Het besturingssysteem moet alle gestarte threads en hun status bijhouden en wijst CPU-tijdslots toe aan elke thread, zodat verschillende toepassingen efficiënt en schijnbaar parallel kunnen lopen.

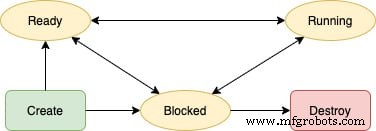

Figuur 1. De verschillende statussen van een thread

De planner van het besturingssysteem houdt een wachtrij bij voor threads die klaar zijn om te worden uitgevoerd, een wachtrij voor het blokkeren van threads en moet informatie opslaan over de threads die momenteel worden uitgevoerd om een eerlijke verdeling van de CPU-tijd te bewerkstelligen:

- Threads in de klaar-wachtrij wachten momenteel tot het besturingssysteem ze op de CPU plant. Doorgaans kent de OS-planner verschillende prioriteitsniveaus, waarmee hij rekening houdt bij het kiezen van de aanstaande thread om op de CPU te draaien.

- Het blokkeren van threads wacht op een externe gebeurtenis, bijvoorbeeld een pin-interrupt of een bestandsbewerking. Het plannen van deze threads zou betekenen dat de CPU verwerkingskracht verspilt door te wachten tot een externe bewerking is voltooid. Zodra de blokkeerbewerking is voltooid, keert de bijbehorende wachtende thread terug naar het einde van de wachtrij 'klaar'.

- De momenteel actieve threads kunnen een blokkerende bewerking uitvoeren, of het besturingssysteem kan een andere thread plannen volgens zijn planningsstrategie. In dat geval zal de planner de huidige thread verplaatsen naar respectievelijk de lijst met geblokkeerde threads of het einde van de wachtrij die klaar is.

OS-ontwikkelaars kunnen ervoor kiezen om een of meerdere planningsstrategieën te implementeren, afhankelijk van de exacte vereisten. Naast planning zijn synchronisatie en communicatie tussen verschillende threads andere essentiële aspecten van multi-threaded systemen.

Voorwaarden en gebeurtenissen in XOS

Condities binnen de XOS RTOS (real-time besturingssysteem) stellen ontwikkelaars in staat om een thread te instrueren om te blokkeren totdat een gespecificeerde voorwaarde waar wordt. Het systeem evalueert elke conditie met behulp van een conditiefunctie die is gedefinieerd door de applicatieontwikkelaars. XOS voert een evaluatie uit wanneer een andere thread het condition-object signaleert of wanneer een interrupt-handler er een activeert.

Gebeurtenissen binnen XOS vertegenwoordigen daarentegen een groep bits die ontwikkelaars kunnen gebruiken om verschillende threads of threads en interrupt-handlers te synchroniseren. XOS staat meerdere threads toe om op gebeurtenissen te wachten en deze gelijktijdig te signaleren.

Onderbrekingen in XOS

XOS biedt een uitgebreide reeks functies voor het afhandelen van onderbrekingen en uitzonderingen die optreden tijdens runtime. De interrupt-mechanismen binnen XOS bieden programmeurs de flexibiliteit om aangepaste handlers te installeren en ervoor te zorgen dat het verzenden van interrupts zo snel mogelijk binnen het systeem werkt. De XOS ondersteunt ook geneste interruptafhandeling, wat betekent dat het besturingssysteem de huidige interrupt-handler pauzeert als er interrupts met een hogere prioriteit optreden. Zodra het systeem klaar is met het afhandelen van de onderbreking met hoge prioriteit, hervat het automatisch de verwerking van de onderbrekingen met lage prioriteit.

Threads kunnen ook tijdgerelateerde services hebben, zoals getimede vertragingen en periodieke timer-callbacks in XOS. De DSP-co-processor ondersteunt maximaal drie interne timers die de programmeurs naar wens kunnen configureren.

Semaforen begrijpen

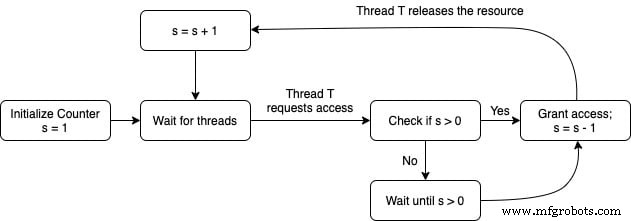

Bij multi-threaded programmeren bieden semaforen een middel om de toegang tot een gedeelde bron te controleren en te coördineren. Semaforen helpen kritieke sectieproblemen in gelijktijdige systemen te voorkomen door verschillende threads te synchroniseren. Semaforen zijn een eenvoudige constructie die een interne teller bijhoudt met een vooraf bepaalde startwaarde die de programmeurs vrij in de broncode kunnen instellen. Er zijn verschillende implementaties, maar de teller geeft meestal aan hoeveel threads nog toegang hebben tot een gedeelde bron.

Telkens wanneer een thread toegang wil tot de gedeelde bron, controleert het systeem of de bijbehorende teller groter is dan nul. Als dat zo is, verleent het besturingssysteem toegang tot de bron en verlaagt het de interne teller van de semafoor. Als een thread op het gegeven moment geen toegang heeft tot de resource, schakelt de thread over naar een blokkerende status en wacht totdat deze toegang krijgt tot de resource. Telkens wanneer een thread de bron vrijmaakt, verhoogt het besturingssysteem de semafoorteller en kan een nieuwe thread de kritieke sectie betreden.

Figuur 2. Een stroomschema dat illustreert hoe semaforen werken

Een overzicht van de i.MX RT500 MCU en de DSP

i.MX RT500 is een familie van dual-core microcontrollers op basis van een krachtige Arm® Cortex®-M33-kern met een kloksnelheid tot 275 MHz en ondersteuning voor maximaal vijf megabyte SRAM.

De i.MX RT500 MCU biedt beveiligingsfuncties zoals Arm TrustZone en een ingebouwde geheugenbeschermingseenheid (MPU) met ondersteuning voor maximaal acht regio's. De CASPER crypto-co-processor maakt hardwareversnelling mogelijk om verschillende functies te versterken die nodig zijn voor asymmetrische cryptografische algoritmen. Dankzij een reeks energiebesparende functies kunnen ontwerpers het stroomverbruik van de i.MX RT500 afstemmen op hun toepassingsvereisten.

Verschillende speciale hardwareversnellers helpen de hoofd-CPU bij het uitvoeren van DSP-berekeningen. Een extra Cadence® Tensilica® Fusion F1 audio DSP, een 2D GPU met vector grafische versnelling en verschillende display-interfaces maken de i.MX RT500 geschikt voor verschillende veilige en energiezuinige embedded applicaties. Typische use-cases zijn onder meer HMI-applicaties, IoT-apparaten, hearables, spraakgestuurde persoonlijke assistenten en andere vergelijkbare consumentenapparaten.

Een blik op de audio-DSP

De i.MX RT500 bevat verschillende speciale co-processors die kunnen helpen de belasting van de CPU-kernen te verlichten door wiskundig complexe berekeningen uit te voeren, terwijl de verwerkingskernen vrij blijven om andere taken uit te voeren. Een van die speciale processors is de fusion DSP, die een Cadence® Tensilica® Fusion F1-audioprocessor en een hardware-floating-point-eenheid bevat.

Deze audioverwerkingsengine werkt op frequenties tot 200 MHz en is ontworpen om altijd-aan spraakgestuurde apparaten zoals virtuele assistenten mogelijk te maken. Bovendien combineert de audio-DSP verschillende modules voor typische voor- en nabewerkingstaken met behulp van talrijke audiocodecs.

De DSP en de belangrijkste CPU-kernen kunnen op verschillende manieren met elkaar communiceren. Ontwikkelaars kunnen het volledige SRAM gebruiken bij het werken met de fusion DSP, tenzij het RAM is beveiligd en bepaalde delen zijn gemarkeerd voor alleen beveiligde toegang.

Programmeren met de DSP in gedachten

Tensilica DSP's ondersteunen verschillende realtime besturingssystemen (RTOS), waaronder FreeRTOS™, Zephyr™, Linux® en XOS. Cadence ontwikkelde de XOS embedded kernel als referentieontwerp met Tensilica-processors in het achterhoofd.

De lichtgewicht XOS-kernelfuncties omvatten een taakplanner, adaptieve contextomschakeling, synchronisatiemechanismen, beheer van onderbrekingen en uitzonderingen en beheer van kritieke bronnen. De broncode van de kernel is voornamelijk geschreven in standaard C en niet specifiek voor Xtensa-processors en DSP's.

Voldoen aan de vereisten voor slimme consumentenapparaten

De i.MX RT500-familie van crossover-MCU's heeft verschillende functies die zijn ontworpen om de slimme consumentenapparaten van morgen te inspireren. De verschillende co-processors helpen de belangrijkste verwerkingskernen van de MCU bij het uitvoeren van wiskundig complexe berekeningen voor beveiligings- en signaalverwerkingstoepassingen. Een van die co-processors is de sterk geoptimaliseerde Cadence® Tensilica® Fusion F1 audio DSP, waardoor altijd-aan spraakgestuurde apparaten zoals virtuele assistenten mogelijk zijn. Programmeurs kunnen XOS en de Xplorer IDE gebruiken om applicaties te ontwerpen voor de speciale Cadence-processor.

De toepassingsnota AN13159 bevat meer details, een lijst met ondersteunde API-functies en voorbeelden voor voorwaarden en gebeurtenissen in XOS, en de website van NXP biedt meer informatie over de i.MX RT500-mogelijkheden en -toepassingen. Het biedt ook verschillende trainingsmaterialen, zoals toepassingsnotities, video's en on-demand webinars.

Industrieartikelen zijn een vorm van inhoud waarmee branchepartners nuttig nieuws, berichten en technologie kunnen delen met lezers van All About Circuits op een manier waarop redactionele inhoud niet goed geschikt is. Alle brancheartikelen zijn onderworpen aan strikte redactionele richtlijnen met de bedoeling de lezers nuttig nieuws, technische expertise of verhalen te bieden. De standpunten en meningen in brancheartikelen zijn die van de partner en niet noodzakelijk die van All About Circuits of zijn schrijvers.

Ingebed

- C# met behulp van

- Hybride apparaat combineert DSP- en MCU-architecturen

- Als een DSP een hardwareversneller verslaat

- Beslissingen, beslissingen:hardwareversneller of DSP?

- Contactloze vloeistofniveaumeting met een reflectometerchip

- RFID-tags gebruiken voor het bewaken van huisbeveiliging

- 4D-beeldradarchipsets verbeteren objectidentificatie

- Determinisme van de opstartfase:multichipsynchronisatie gebruiken

- Bluetooth MCU verbetert IoT-beveiliging

- Draadloze MCU met dual-core architectuur

- Richtlijnen voor het gebruik van DSP-handvat: