Ingesloten ontwerp met FPGA's:hardwarebronnen

Noot van de redactie:naarmate er steeds meer geavanceerde algoritmen verschijnen voor slimme productontwerpen, hebben ontwikkelaars vaak moeite om embedded systemen te implementeren die in staat zijn om aan de bijbehorende verwerkingsvereisten van deze algoritmen te voldoen. FPGA's kunnen de vereiste prestaties leveren, maar ontwerpen met FPGA's werd lang beschouwd als beperkt tot de bevoegdheid van FPGA-programmeerexperts. Tegenwoordig heeft de beschikbaarheid van krachtigere FPGA's en effectievere ontwikkelomgevingen FPGA-ontwikkeling echter breed toegankelijk gemaakt. In dit fragment, hoofdstuk 4 uit het boek Architecting High-Performance Embedded Systems, biedt de auteur een uitgebreid overzicht van FPGA-apparaten, implementatietalen en het FPGA-ontwikkelingsproces, evenals een gedetailleerd overzicht van hoe u aan de slag kunt gaan met het implementeren van FPGA's in uw eigen ontwerp. Het volledige fragment wordt gepresenteerd in de volgende reeks afleveringen:

Noot van de redactie:naarmate er steeds meer geavanceerde algoritmen verschijnen voor slimme productontwerpen, hebben ontwikkelaars vaak moeite om embedded systemen te implementeren die in staat zijn om aan de bijbehorende verwerkingsvereisten van deze algoritmen te voldoen. FPGA's kunnen de vereiste prestaties leveren, maar ontwerpen met FPGA's werd lang beschouwd als beperkt tot de bevoegdheid van FPGA-programmeerexperts. Tegenwoordig heeft de beschikbaarheid van krachtigere FPGA's en effectievere ontwikkelomgevingen FPGA-ontwikkeling echter breed toegankelijk gemaakt. In dit fragment, hoofdstuk 4 uit het boek Architecting High-Performance Embedded Systems, biedt de auteur een uitgebreid overzicht van FPGA-apparaten, implementatietalen en het FPGA-ontwikkelingsproces, evenals een gedetailleerd overzicht van hoe u aan de slag kunt gaan met het implementeren van FPGA's in uw eigen ontwerp. Het volledige fragment wordt gepresenteerd in de volgende reeks afleveringen:

1:Hardwarebronnen (dit artikel)

2:Implementatietalen

3:Ontwikkelingsproces

4:Een project bouwen

5:Implementatie

Aangepast van het ontwerpen van hoogwaardige ingebedde systemen, door Jim Ledin.

Uw eerste FPGA-programma ontwikkelen

Dit hoofdstuk begint met een bespreking van het effectieve gebruik van FPGA-apparaten in realtime embedded systemen en gaat verder met een beschrijving van de functionele elementen in standaard FPGA's. De reeks FPGA-ontwerptalen, waaronder Hardware Beschrijvingstalen (HDL's ), blokdiagrammethoden en populaire programmeertalen voor software, waaronder C en C++, worden geïntroduceerd. Het hoofdstuk gaat verder met een overzicht van het FPGA-ontwikkelingsproces en eindigt met een compleet voorbeeld van een FPGA-ontwikkelingscyclus, beginnend met een overzicht van systeemvereisten en eindigend met een functioneel systeem geïmplementeerd in een goedkoop FPGA-ontwikkelbord.

Na het voltooien van dit hoofdstuk weet u hoe FPGA's kunnen worden toegepast in realtime embedded systeemarchitecturen en begrijpt u de componenten waaruit een FPGA-geïntegreerd circuit bestaat. Je hebt geleerd over de programmeertalen die worden gebruikt bij het ontwerpen van FPGA-algoritmen en je begrijpt de volgorde van stappen om een op FPGA gebaseerde applicatie te ontwikkelen. Je hebt ook een compleet FPGA-ontwikkelingsvoorbeeld doorlopen op een goedkoop ontwikkelbord met behulp van gratis FPGA-softwaretools.

In dit hoofdstuk zullen we de volgende onderwerpen behandelen:

- FPGA's gebruiken in realtime embedded systeemontwerpen

- FPGA-implementatietalen

- Het FPGA-ontwikkelingsproces

- Uw eerste FPGA-project ontwikkelen

Technische vereisten

De bestanden voor dit hoofdstuk zijn beschikbaar op https://github.com/PacktPublishing/Architecting-High-Performance-Embedded-Systems.

FPGA's gebruiken in realtime embedded systeemontwerpen

Zoals we zagen in de Elementen van FPGA's sectie van Hoofdstuk 1 , Hoogwaardige architectuur Ingesloten systemen , bevat een typisch FPGA-apparaat een groot aantal opzoektabellen, flip-flops, blok-RAM-elementen, DSP-segmenten en andere componenten. Hoewel het leerzaam kan zijn om de gedetailleerde mogelijkheden van elk van deze componenten te begrijpen, zijn dergelijke zorgen niet noodzakelijk informatief tijdens het FPGA-ontwikkelingsproces. De belangrijkste beperking om in gedachten te houden is dat een specifiek FPGA-onderdeelnummer een eindig aantal van elk van deze elementen bevat, en een ontwerp kan die limieten niet overschrijden wanneer het op dat specifieke FPGA-model is gericht.

In plaats daarvan is het productiever om het FPGA-ontwikkelingsproces te bekijken vanuit het perspectief van de eisen van het embedded systeem. U kunt beginnen met het ontwikkelen van het FPGA-ontwerp gericht op een enigszins willekeurig gekozen FPGA-model. Naarmate de ontwikkeling vordert, kunt u een resourcelimiet bereiken of een FPGA-functie identificeren die het ontwerp vereist en die niet aanwezig is in de momenteel beoogde FPGA. Op dat moment kunt u een ander, beter doel selecteren en doorgaan met ontwikkelen.

Als de ontwikkeling van het ontwerp zijn voltooiing nadert, kunt u zich ook realiseren dat de doel-FPGA die u oorspronkelijk hebt geselecteerd, overmatige middelen bevat en dat het ontwerp kan worden verbeterd door een kleinere FPGA te selecteren, met mogelijke voordelen in termen van lagere kosten, minder pinnen, kleinere pakketgrootte, en minder stroomverbruik.

In elk van deze situaties is het over het algemeen eenvoudig om de beoogde FPGA over te schakelen naar een ander model binnen dezelfde familie. De ontwikkelingstools en ontwerpartefacten die u tot nu toe hebt gemaakt, moeten volledig herbruikbaar zijn met het nieuw gerichte FPGA-model. Als het nodig is om over te stappen naar een andere familie van FPGA's van dezelfde leverancier, of naar een model van een andere leverancier, zal de omschakeling waarschijnlijk meer werk met zich meebrengen.

Het punt van deze discussie is om te benadrukken dat het niet zo belangrijk is om een specifiek FPGA-model te identificeren aan het begin van een krachtige ontwikkelingsinspanning voor ingebedde systemen. In plaats daarvan moeten vroege overwegingen zich richten op het valideren van de beslissing om een FPGA te gebruiken als onderdeel van het ontwerp. Als de FPGA de beste ontwerpbenadering is, ga dan verder met de selectie van een geschikte FPGA-leverancier en apparaatfamilie.

Voorbeeldprojecten in dit boek zijn gebaseerd op de Xilinx Vivado-familie van FPGA-ontwikkeltools. Hoewel een Vivado-licentie moet worden aangeschaft om voor sommige Xilinx FPGA-families te ontwikkelen, worden de FPGA-apparaten in de Artix-7 waarmee we gaan werken gratis door Vivado ondersteund. De Artix-7 FPGA-familie combineert de kenmerken van hoge prestaties, een laag stroomverbruik en lagere totale systeemkosten. Vergelijkbare FPGA-apparaatfamilies en ontwikkeltoolsuites zijn verkrijgbaar bij andere FPGA-leveranciers.

FPGA-ontwikkeling is een redelijk betrokken proces, waarbij een verscheidenheid aan soorten analyse en invoer van ontwerpgegevens vereist is. Om te voorkomen dat deze onderwerpen op een te abstract niveau worden besproken en om concrete resultaten te presenteren in termen van werkende voorbeeldprojecten, zullen we Vivado door het hele boek heen gebruiken. Als je eenmaal bekend bent met de tools en technieken die hier worden besproken, zou je ze moeten kunnen toepassen met vergelijkbare tools van andere leveranciers.

In de volgende secties worden enkele belangrijke onderscheidende kenmerken van de families van FPGA's en individuele modellen binnen die families besproken, waaronder de hoeveelheid blok-RAM, de hoeveelheid en soorten beschikbare I/O-signalen, gespecialiseerde hardwarebronnen op de chip en de opname van een of meer hardwareprocessorcores in het FPGA-pakket.

RAM blokkeren en gedistribueerd RAM-geheugen

RAM blokkeren wordt gebruikt om geheugengebieden binnen een FPGA te implementeren. Een bepaald geheugengebied wordt gespecificeerd in termen van de breedte in bits (meestal 8 of 16 bits) en de diepte, die het aantal opslaglocaties in het geheugengebied definieert.

De totale hoeveelheid blok-RAM in een FPGA wordt meestal gespecificeerd in termen van kilobits (Kb ). De hoeveelheid beschikbare blok-RAM varieert tussen FPGA-families en tussen de modellen binnen een bepaalde familie. Zoals je zou verwachten, hebben grotere, duurdere onderdelen over het algemeen een grotere hoeveelheid bronnen die als blok-RAM kunnen worden gebruikt.

In Xilinx FPGA's, en in verschillende mate in FPGA's van andere leveranciers, is naast blok-RAM een aparte categorie geheugen, gedistribueerd RAM genaamd, beschikbaar. Gedistribueerd RAM is opgebouwd uit de logische elementen die worden gebruikt in opzoektabellen en hergebruikt de circuits van die apparaten om kleine RAM-segmenten te vormen, die elk 16 bits bevatten. Deze segmenten kunnen indien nodig worden samengevoegd om grotere geheugenblokken te vormen.

Blok-RAM wordt meestal gebruikt voor doeleinden die traditioneel worden geassocieerd met RAM, zoals het implementeren van processorcachegeheugen of als opslagbuffer voor I/O-gegevens. Gedistribueerd RAM kan worden gebruikt voor doeleinden zoals de tijdelijke opslag van tussentijdse berekeningsresultaten. Omdat gedistribueerd RAM-geheugen is gebaseerd op opzoektabelcircuits, vermindert het gebruik van gedistribueerd RAM in een ontwerp de beschikbare middelen voor het implementeren van logische bewerkingen.

Blok-RAM kan een enkele poort of dubbele poorten hebben. Blok-RAM met één poort vertegenwoordigt het algemene gebruikspatroon van een processor die RAM leest en schrijft tijdens bedrijf.

Dual-port block-RAM biedt twee lees-/schrijfpoorten, die beide tegelijkertijd actief kunnen lezen of schrijven in hetzelfde geheugengebied.

Blok-RAM met twee poorten is ideaal voor situaties waarin gegevens worden overgedragen tussen delen van een FPGA die met verschillende kloksnelheden werken. Een I/O-subsysteem kan bijvoorbeeld een kloksnelheid van honderden MHz hebben wanneer het een inkomende gegevensstroom ontvangt. Het I/O-subsysteem schrijft binnenkomende gegevens naar het blok-RAM wanneer deze binnenkomen via een van de snelle I/O-kanalen van de FPGA. Een apart subsysteem binnen de FPGA, dat op een andere kloksnelheid draait, kan gegevens van de tweede poort van het blok-RAM lezen zonder de werking van het I/O-subsysteem te verstoren.

Blok-RAM kan ook werken in first-in-first-out (FIFO ) modus. In het voorbeeld van de inkomende seriële datastroom kan het I/O-subsysteem datawoorden invoegen in de FIFO zodra ze binnenkomen en het verwerkingssubsysteem kan ze in dezelfde volgorde uitlezen. Blok-RAM in FIFO-modus levert signalen die aangeven of de FIFO vol, leeg, bijna vol of bijna leeg is. De definities van bijna vol en bijna leeg zijn aan de systeemontwerper. Als u bijna leeg . toewijst om te betekenen dat er minder dan 16 items in de FIFO over zijn, kunt u er zeker van zijn dat elke keer dat de FIFO niet aangeeft dat deze bijna leeg is, u 16 items kunt lezen zonder verdere controle van de beschikbaarheid van gegevens.

Wanneer blok-RAM in FIFO-modus wordt gebruikt, is het van vitaal belang dat de logica die items in de FIFO invoegt, nooit probeert te schrijven wanneer de FIFO vol is, en dat de logische lezing van de FIFO nooit probeert te lezen wanneer de FIFO leeg is. Als een van deze gebeurtenissen optreedt, verliest het systeem gegevens of probeert het ongedefinieerde gegevens te verwerken.

FPGA I/O-pinnen en bijbehorende functies

Omdat FPGA's bedoeld zijn voor gebruik in krachtige toepassingen, zijn hun I/O-pinnen over het algemeen in staat om een verscheidenheid aan snelle I/O-standaarden te implementeren. Tijdens de implementatie van een ontwerp met een FPGA-ontwikkeltoolsuite, moet de systeemontwikkelaar taken uitvoeren, waaronder het toewijzen van functies aan bepaalde pinnen op het FPGA-pakket en het configureren van elk van die pinnen om te werken met de juiste interfacestandaard. Er moeten aanvullende stappen worden uitgevoerd om ingangs- en uitgangssignalen binnen de FPGA-modelcode te koppelen aan de juiste pakketpinnen.

Op pin-niveau zijn individuele I/O-signalen ofwel single-ended of differentieel.

Een eenzijdig signaal verwijst naar de grond. Traditionele Transistor-Transistor-logica (TTL ) en Complementaire metaaloxide halfgeleider (CMOS ) digitale signalen werken over een bereik van 0-5 VDC ten opzichte van aarde.

Moderne FPGA's ondersteunen doorgaans niet het legacy 5 VDC-signaalbereik, maar ondersteunen in plaats daarvan TTL- en CMOS-signalen die over een kleiner spanningsbereik werken, waardoor het stroomverbruik wordt verminderd en de snelheid wordt verbeterd. Laagspanning TTL (LVTTL ) signalen werken over een bereik van 0-3,3 VDC. Laagspanning CMOS (LVCMOS ) signalen kunnen worden geselecteerd met signaalspanningen van 1,2, 1,5, 1,8, 2,5 en 3,3 V. Deze signaaltypen worden LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25 en LVCMOS33 genoemd. Er zijn andere hoogwaardige single-ended signaaltypes beschikbaar, waaronder High-Speed Transceiver Logic (HSTL ) en Stub-serie beëindigde logica (SSTL ).

Single-ended signalen worden veel gebruikt voor laagfrequente doeleinden, zoals het lezen van drukknopingangen en het verlichten van LED's. Single-ended signalen worden ook gebruikt in veel communicatieprotocollen met een lagere snelheid, zoals I2C en SPI. Een belangrijk nadeel van single-ended signalen is dat ruis die is gekoppeld aan de draden en printplaatsporen die het signaal dragen, de ingang naar de ontvanger kan beschadigen. Dit probleem kan aanzienlijk worden verminderd door het gebruik van differentiële signalering.

Voor de hoogste gegevensoverdrachtsnelheden heeft differentiële signalering de voorkeur.

Differentiële signalen gebruik een paar I/O-pinnen en stuur tegengestelde signalen naar de twee pinnen.

Met andere woorden, één pin wordt naar een hogere spanning gestuurd en de andere pin naar een lagere spanning om een 0-gegevensbit weer te geven en de pinspanningen worden omgekeerd om een 1-bit weer te geven. De differentiële ontvanger trekt de twee signalen af om te bepalen of de databit 0 of 1 is. Omdat de twee draden of sporen die het differentiële signaal dragen zich fysiek zeer dicht bij elkaar bevinden, zal elke ruis die in een van de signalen wordt gekoppeld, worden gekoppeld aan de andere. op een zeer vergelijkbare manier. De aftrekbewerking verwijdert de overgrote meerderheid van de ruis, waardoor een betrouwbare werking mogelijk is met veel hogere gegevensoverdrachtsnelheden dan single-ended signalen.

Een aantal differentiële signaalstandaarden worden ondersteund door standaard FPGA's. Er zijn verschillende differentiële versies van HSTL en SSTL gedefinieerd, met verschillende signaalspanningsniveaus voor elk.

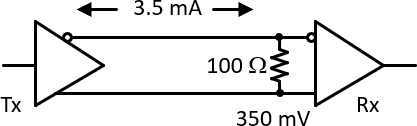

Laagspanning differentiële signalering (LVDS ) werd in 1994 als standaard geïntroduceerd en wordt nog steeds in tal van toepassingen gebruikt. Een LVDS-signaleringszender produceert een constante stroom van 3,5 mA en verandert de richting van de stroom die door de weerstand bij de ontvanger vloeit om toestandsveranderingen te produceren die 0 en 1 gegevenswaarden vertegenwoordigen, zoals weergegeven in Figuur 4.1 :

Figuur 4.1 – LVDS-interface

Bij LVDS-communicatie, net als bij de andere differentiële en single-ended signaleringsstandaarden, is het belangrijk dat de impedantie van het communicatiepad tussen de zender en ontvanger nauw aansluit bij de afsluitimpedantie, die 100 ohm is in het geval van LVDS. Als de impedantie van het communicatiekanaal niet overeenkomt met de afsluitimpedantie, kunnen er reflecties optreden op de lijn, waardoor betrouwbare gegevensontvangst wordt verhinderd.

De impedantie van differentiële signaalspoorparen is een functie van de geometrie van de paarsporen en hun relatie tot het grondvlak. Zoals we zullen zien in Hoofdstuk 6 , Circuits ontwerpen met KiCad , is het eenvoudig om printplaten te ontwerpen die voldoen aan de vereisten van high-speed differentiële signaleringsnormen.

Gespecialiseerde hardwarebronnen

FPGA's bevatten over het algemeen een selectie van speciale hardwarebronnen voor functies die vaak nodig zijn en zijn ofwel efficiënter geïmplementeerd in hardware in plaats van gesynthetiseerde FPGA-functies te gebruiken, of kunnen niet worden geïmplementeerd met FPGA-componenten. Enkele voorbeelden van deze bronnen zijn:

- Interfaces naar extern dynamisch RAM (DRAM ) voor het opslaan van grote hoeveelheden van Deze interfaces ondersteunen over het algemeen een algemene DRAM-standaard zoals DDR3.

- Analoog-naar-digitaal converters.

- Lussen met fasevergrendeling, gebruikt voor het genereren van meerdere klokfrequenties.

- Digitale signaalverwerking multiply-accumulate (MAC ) hardware.

Deze hardwarebronnen maken de ontwikkeling van complexe systemen met uitgebreide mogelijkheden mogelijk. Er wordt speciale hardware geleverd voor functies zoals de MAC-bewerking, omdat de hardwareprestaties aanzienlijk beter zijn dan de gesynthetiseerde equivalente functionaliteit met behulp van FPGA-logische bronnen.

Processorkernen

Sommige FPGA-families bevatten hardwareprocessorkernen om de hoogste software-uitvoeringssnelheid te combineren met de prestatievoordelen van FPGA-geïmplementeerde algoritmen. De Xilinx Zynq-7000-familie integreert bijvoorbeeld een hardware ARM Cortex-A9-processor samen met een traditionele FPGA-stof.

FPGA-ontwerpen waarvoor geen hardwareprocessor nodig is, kunnen een processor implementeren met behulp van de FPGA-bronnen, een zachte processor genoemd. . Zachte processors zijn zeer configureerbaar, hoewel ze over het algemeen niet in staat zijn om de prestaties van een in hardware geïmplementeerde processor te evenaren.

In het volgende gedeelte worden de primaire programmeertalen en gegevensinvoermethoden geïntroduceerd die worden gebruikt om FPGA-algoritmen te ontwikkelen.

Herdrukt met toestemming van Packt Publishing. Copyright © 2021 Packt Publishing

Jim Ledin is de CEO van Ledin Engineering, Inc. Jim is een expert in het ontwerpen, ontwikkelen en testen van embedded software en hardware. Hij is ook bekwaam in het beoordelen van cyberbeveiliging van embedded systemen en het testen van penetratie. Hij heeft een B.S. graad in lucht- en ruimtevaarttechniek van Iowa State University en een M.S. graad in elektrotechniek en computertechniek aan het Georgia Institute of Technology. Jim is een geregistreerde professionele elektrotechnisch ingenieur in Californië, een Certified Information System Security Professional (CISSP), een Certified Ethical Hacker (CEH) en een Certified Penetration Tester (CPT).

Jim Ledin is de CEO van Ledin Engineering, Inc. Jim is een expert in het ontwerpen, ontwikkelen en testen van embedded software en hardware. Hij is ook bekwaam in het beoordelen van cyberbeveiliging van embedded systemen en het testen van penetratie. Hij heeft een B.S. graad in lucht- en ruimtevaarttechniek van Iowa State University en een M.S. graad in elektrotechniek en computertechniek aan het Georgia Institute of Technology. Jim is een geregistreerde professionele elektrotechnisch ingenieur in Californië, een Certified Information System Security Professional (CISSP), een Certified Ethical Hacker (CEH) en een Certified Penetration Tester (CPT). Verwante inhoud:

- Open-source tools helpen FPGA-programmering te vereenvoudigen

- Implementatie van drijvende-kommaalgoritmen in FPGA's of ASIC's

- Gebruik maken van FPGA's voor diepgaand leren

- Softwaretools migreren GPU-code naar FPGA's voor AI-toepassingen

- FPGA's verdringen ASIC's in op Subaru Eyesight gebaseerde ADAS

- Hoe op flash gebaseerde FPGA's functionele veiligheidsvereisten vereenvoudigen

- De voordelen plukken van instant-on FPGA's

- FPGA-configuratie met snelle NOR-flitser

- Hoe FPGA-technologie evolueert om te voldoen aan nieuwe systeemvereisten voor het middensegment

Abonneer u voor meer Embedded op de wekelijkse e-mailnieuwsbrief van Embedded.

Ingebed

- Hoe voorkom je kostbare verrassingen bij het ontwerpen van verbonden hardware

- Wat is ingebed systeemontwerp:stappen in het ontwerpproces

- Vereenvoudiging van IoT-ontwikkeling met Eclipse IoT

- Statusmachines ontwikkelen met testgestuurde ontwikkeling

- Big data omzetten in slimme data met ingebouwde AI

- Community-gestuurde bron spoort zwakke punten in de beveiliging van hardwareontwerp op

- Cypress:ModusToolbox Suite vereenvoudigt IoT-ontwerpcomplexiteit

- Lattice:MachX03D FPGA verbetert de beveiliging met hardware root-of-trust-mogelijkheden

- Ontwerpkit meet bloeddruk met optische sensor

- Java 9 - Probeer met middelenverbetering

- All-in met additief