Hoe maak je een signaalvector in VHDL:std_logic_vector

De std_logic_vector type kan worden gebruikt voor het maken van signaalbussen in VHDL. De std_logic is het meest gebruikte type in VHDL, en de std_logic_vector is de array-versie ervan.

Terwijl de std_logic is geweldig voor het modelleren van de waarde die kan worden gedragen door een enkele draad, het is niet erg praktisch voor het implementeren van verzamelingen draden die van of naar componenten gaan. De std_logic_vector is een samengesteld type, wat betekent dat het een verzameling subelementen is. Signalen of variabelen van de std_logic_vector type kan een willekeurig aantal std_logic . bevatten elementen.

Deze blogpost maakt deel uit van de serie Basic VHDL Tutorials.

De syntaxis voor het declareren van std_logic_vector signalen is:signal <name> : std_logic_vector(<lsb> to <msb>) := <initial_value>;

ofsignal <name> : std_logic_vector(<msb> downto <lsb>) := <initial_value>;

waar <name> is een willekeurige naam voor het signaal en <initial_value> is een optionele beginwaarde. De <lsb> is de index van het minst significante bit, en <msb> is de index van het meest significante bit.

De to of downto specificeert de richting van het bereik van de bus, in feite zijn endianess. Hoewel beide even goed werken, is het gebruikelijk dat VHDL-ontwerpers vectoren declareren met downto . Daarom raad ik u aan altijd downto . te gebruiken wanneer u bitvectoren declareert om verwarring te voorkomen.

De VHDL-code voor het declareren van een vectorsignaal dat een byte kan bevatten:signal MySlv : std_logic_vector(7 downto 0);

De VHDL-code voor het declareren van een vectorsignaal dat één bit kan bevatten:signal MySlv : std_logic_vector(0 downto 0);

De VHDL-code voor het declareren van een vectorsignaal dat nul bits kan bevatten (een leeg bereik ):signal MySlv : std_logic_vector(-1 downto 0);

Oefening

In deze video-tutorial leren we hoe je std_logic_vector . kunt declareren signalen en geef ze beginwaarden. We leren ook hoe we de bits in een vector kunnen herhalen met behulp van een For-Loop om een schuifregister te maken :

De laatste code die we in deze tutorial hebben gemaakt:

library ieee;

use ieee.std_logic_1164.all;

entity T11_StdLogicVectorTb is

end entity;

architecture sim of T11_StdLogicVectorTb is

signal Slv1 : std_logic_vector(7 downto 0);

signal Slv2 : std_logic_vector(7 downto 0) := (others => '0');

signal Slv3 : std_logic_vector(7 downto 0) := (others => '1');

signal Slv4 : std_logic_vector(7 downto 0) := x"AA";

signal Slv5 : std_logic_vector(0 to 7) := "10101010";

signal Slv6 : std_logic_vector(7 downto 0) := "00000001";

begin

-- Shift register

process is

begin

wait for 10 ns;

for i in Slv6'left downto Slv6'right + 1 loop

Slv6(i) <= Slv6(i-1);

end loop;

Slv6(Slv6'right) <= Slv6(Slv6'left);

end process;

end architecture;

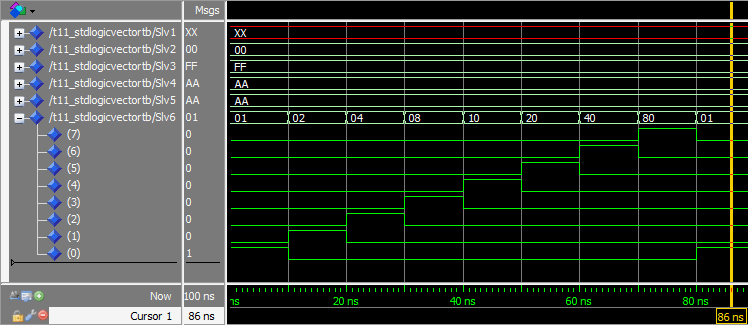

Het golfvormvenster in ModelSim nadat we op run hebben gedrukt en ingezoomd op de tijdlijn:

Analyse

In deze oefening hebben we zes std_logic_vector . gedeclareerd bussen, elk acht bits lang (één byte).

Signaal Slv1 werd gedeclareerd zonder een beginwaarde. De bus is te zien met de waarde XX in de golfvorm-screenshot. Dit komt omdat de waarde die op de bus wordt weergegeven in hexadecimalen is en XX een niet-hexadecimale waarde aangeeft. Maar toen we de bus in de golfvorm uitbreidden, konden we zien dat de afzonderlijke bits inderdaad U's waren.

Signaal Slv2 werd gedeclareerd met een beginwaarde van alle nullen. In plaats van de exacte waarde voor elke bit te specificeren, gebruikten we (other => '0') in plaats van de beginwaarde. Dit staat bekend als een aggregaat opdracht. Het belangrijkste is dat het alle bits in de vector instelt op wat je opgeeft, ongeacht hoe lang het is.

Signaal Slv3 werd gedeclareerd met behulp van een geaggregeerde toewijzing om alle bits de beginwaarde van 1 te geven. We kunnen FF op dit signaal zien in de golfvorm, die hex is voor acht enen.

Signaal Slv4 werd gedeclareerd met een initiële waarde gespecificeerd in hex, AA. Elk hexadecimaal cijfer is 4 bits lang, daarom moeten we twee cijfers (AA) opgeven voor onze vector die 8 bits lang is.

Signaal Slv5 declareert exact dezelfde beginwaarde als Slv4 , maar nu hebben we het gespecificeerd als de binaire waarde 10101010. We kunnen aan de golfvorm zien dat beide signalen de hexadecimale waarde AA hebben.

Signaal Slv6 werd gedeclareerd met een initiële waarde van allemaal nullen, behalve de meest rechtse bit die '1' . was . We hebben een proces gebruikt om een ploegenregister te maken van dit signaal. Het schuifregister, zoals de naam al aangeeft, verschuift de inhoud van de vector elke 10 nanoseconden één plaats naar links.

Ons proces wordt elke 10 ns wakker en de For-Loop verschuift alle bits in de vector één plaats naar links. Het laatste bit wordt teruggeschoven naar de eerste index door de Slv6(Slv6'right) <= Slv6(Slv6'left); uitspraak. In de golfvorm zien we de '1' rimpel door de vector.

Dit is een visualisatie van hoe de '1' plant zich voort via ons ploegenregister:

Door de 'left' . te gebruiken en 'right attributen, hebben we onze code generieker gemaakt. Als we de breedte van Sig6 . wijzigen , zal het proces nog steeds werken. Het is een goede ontwerppraktijk om attributen te gebruiken waar dat kan in plaats van hardcoded waarden.

U vraagt zich misschien af of er meer attributen zijn die u kunt gebruiken, en die zijn er. Ik zal er niet meer over praten in deze tutorialserie, omdat ik ze beschouw als geavanceerde VHDL-functies.

Afhaalmaaltijden

- N-bit vectoren moeten worden gedeclareerd met

std_logic_vector(N-1 downto 0) - Een vector kan als een geheel worden toegewezen of bits erin zijn afzonderlijk toegankelijk

- Alle bits in een vector kunnen op nul worden gezet met behulp van de aggregatietoewijzing

(others => '0') - Code kan algemener worden gemaakt door attributen te gebruiken zoals

'leften'right

Doe de Basic VHDL Quiz – deel 2 »

of

Ga naar de volgende tutorial »

VHDL

- Voorbeelden van VHDL-conversies

- Ondertekend versus niet-ondertekend in VHDL

- Een lijst met strings maken in VHDL

- Hoe maak je een Tcl-gestuurde testbench voor een VHDL-codeslotmodule?

- Simulatie stoppen in een VHDL-testbench

- Een PWM-controller maken in VHDL

- Hoe willekeurige getallen te genereren in VHDL

- Hoe maak je een ringbuffer FIFO in VHDL

- Hoe maak je een zelfcontrolerende testbank aan

- Een gekoppelde lijst maken in VHDL

- Een procedure gebruiken in een proces in VHDL