Ondertekend en niet-ondertekend gebruiken in VHDL

De ondertekende en niet-ondertekende typen in VHDL zijn bitvectoren, net als het type std_logic_vector. Het verschil is dat, hoewel de std_logic_vector geweldig is voor het implementeren van databussen, het nutteloos is voor het uitvoeren van rekenkundige bewerkingen.

Als u een nummer probeert toe te voegen aan een std_logic_vector type, zal ModelSim de compilatiefout produceren:Geen haalbare vermeldingen voor infix-operator "+". Dit komt omdat de compiler niet weet hoe deze verzameling bits die de vector is, moet interpreteren.

Deze blogpost maakt deel uit van de serie Basic VHDL Tutorials.

We moeten onze vector als ondertekend of niet-ondertekend declareren zodat de compiler hem als een getal kan behandelen.

De syntaxis voor het declareren van ondertekende en niet-ondertekende signalen is:signal <name> : signed(<N-bits> downto 0) := <initial_value>;

signal <name> : unsigned(<N-bits> downto 0) := <initial_value>;

Net als bij std_logic_vector kunnen de bereiken to . zijn of downto elk bereik. Maar het declareren van signalen met een ander bereik dan downto 0 is zo ongewoon, dat meer tijd besteden aan het onderwerp ons alleen maar in verwarring zou brengen. De beginwaarde is optioneel, standaard is dit 'U' voor alle bits.

We hebben de integer . al gebruikt type voor rekenkundige bewerkingen in eerdere tutorials. Dus waarom hebben we de ondertekende en niet-ondertekende typen nodig? Voor de meesten hebben digitale ontwerpers graag meer controle over hoeveel bits een signaal daadwerkelijk gebruikt.

Ook lopen ondertekende en niet-ondertekende waarden rond, terwijl de simulator een runtime-fout genereert als een integer wordt buiten de grenzen verhoogd. Ten slotte kunnen ondertekend en niet-ondertekend andere waarden hebben, zoals 'U' en 'X' , terwijl gehele getallen alleen getalwaarden kunnen hebben. Deze meta-waarden kunnen ons helpen fouten in ons ontwerp te ontdekken.

Oefening

In deze video leren we hoe ondertekende en niet-ondertekende signalen zich hetzelfde gedragen en hoe ze zich anders gedragen:

De laatste code die we in deze tutorial hebben gemaakt:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T12_SignedUnsignedTb is

end entity;

architecture sim of T12_SignedUnsignedTb is

signal UnsCnt : unsigned(7 downto 0) := (others => '0');

signal SigCnt : signed(7 downto 0) := (others => '0');

signal Uns4 : unsigned(3 downto 0) := "1000";

signal Sig4 : signed(3 downto 0) := "1000";

signal Uns8 : unsigned(7 downto 0) := (others => '0');

signal Sig8 : signed(7 downto 0) := (others => '0');

begin

process is

begin

wait for 10 ns;

-- Wrapping counter

UnsCnt <= UnsCnt + 1;

SigCnt <= SigCnt + 1;

-- Adding signals

Uns8 <= Uns8 + Uns4;

Sig8 <= Sig8 + Sig4;

end process;

end architecture;

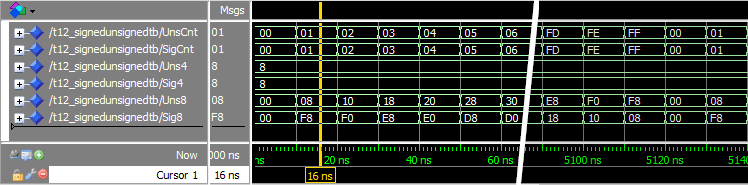

Het golfvormvenster in ModelSim, zoomde in op de interessante onderdelen:

Analyse

De radix van alle signalen in de golfvorm zijn ingesteld op hexadecimaal, zodat we ze gelijk kunnen vergelijken.

In het voorbeeld van de wikkelteller zien we dat de getekende en niet-ondertekende signalen zich precies hetzelfde gedragen. Beide UnsCnt en SigCnt beginnen bij 0 en worden één voor één verhoogd tot FF. Hex FF (decimaal 255) is de grootste waarde die onze 8-bits signalen kunnen bevatten. Daarom wikkelt de volgende stap ze beide terug naar 0.

We hebben de twee 4-bits signalen Uns4 . gemaakt en Sig4 , en gaf ze allebei een beginwaarde van "1000". We kunnen aan de golfvorm zien dat ze allebei slechts hex 8 zijn (binair 1000).

De laatste twee 8-bits signalen die we hebben gemaakt waren Uns8 en Sig8 . We kunnen aan de golfvorm zien dat hun initiële waarden 0 zijn, zoals men zou verwachten. Maar vanaf daar gedragen ze zich anders! Blijkbaar maakten ondertekende en niet-ondertekende typen een verschil bij het toevoegen van twee signalen van verschillende lengte.

Dit komt door iets dat bekend staat als tekenextensie . Het toevoegen van positieve of negatieve getallen die zijn opgeslagen in vectoren van gelijke lengte, is dezelfde bewerking in digitale logica. Dit komt door hoe het complement van twee werkt. Als de vectoren van verschillende lengte zijn, moet de kortste vector worden verlengd.

Het niet-ondertekende 4-bits binaire getal "1000" is decimaal 8, terwijl het ondertekende 4-bits getal "1000" decimaal -8 is. De "1" op de meest linkse plaats van het ondertekende getal geeft aan dat dit een negatief getal is. Daarom worden de twee 4-bits signalen door de compiler verschillend van teken verlengd.

Dit is een visualisatie van hoe tekenextensie de verschillende waarden creëert voor de Uns8 en Sig8 signalen:

Afhaalmaaltijden

- Signalen van het type met en zonder teken zijn vectoren die kunnen worden gebruikt in rekenkundige bewerkingen

- Signalen van het ondertekende en niet-ondertekende type zullen stil overlopen

- Ondertekenextensie kan verschillende resultaten opleveren voor ondertekende en niet-ondertekende typen

Ga naar de volgende tutorial »

VHDL

- Ondertekend versus niet-ondertekend in VHDL

- Een procedure gebruiken in een proces in VHDL

- Een onzuivere functie gebruiken in VHDL

- Een functie gebruiken in VHDL

- Een procedure gebruiken in VHDL

- Constanten en generieke kaart gebruiken in VHDL

- Hoe Port Map-instantiatie te gebruiken in VHDL

- Een Case-When-statement gebruiken in VHDL

- Hoe een VHDL-simulator en -editor gratis te installeren

- PIC18 Microcontroller:wat het is en hoe het te gebruiken?

- Wat is een referentie-aanduiding en hoe gebruiken we deze bij assemblage?