Differentiële isometrische verwerking en simulatieverificatie van high-speed PCB-ontwerp

Invloed van relatieve vertraging op signalen

Signalen die in differentiële signaallijnen worden verzonden, bevatten differentiële moduscomponent en common-modecomponent van signalen.

De hoeveelheid differentiële signalen verwijst naar het verschil tussen twee signalen volgens formule Vdiff =V1 - V2 . De hoeveelheid common mode-signalen verwijst naar de helft van de som van twee signalen volgens formule: . Daarom leidt de spanningsverandering van een enkele lijn zeker tot de gelijktijdige invloed op differentiële modussignalen en common-modussignalen. Vervolgens wordt grafische software toegepast om wiskundige functiediagrammen te tekenen om respectievelijk de invloed op differentiële modussignalen en common-modussignalen te bestuderen. Voor het gemak van onderzoek kunnen signalen worden geanalyseerd door ze te simuleren in een trapeziumvormige golfvorm met dezelfde boven- en uitvaltijd.

. Daarom leidt de spanningsverandering van een enkele lijn zeker tot de gelijktijdige invloed op differentiële modussignalen en common-modussignalen. Vervolgens wordt grafische software toegepast om wiskundige functiediagrammen te tekenen om respectievelijk de invloed op differentiële modussignalen en common-modussignalen te bestuderen. Voor het gemak van onderzoek kunnen signalen worden geanalyseerd door ze te simuleren in een trapeziumvormige golfvorm met dezelfde boven- en uitvaltijd.

• Invloed op differentiële signalen

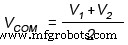

Het positieve fase-aansluitsignaal, het negatieve fase-aansluitsignaal en het differentiële signaal van differentiële lijnparen worden weergegeven in Afbeelding 1 hieronder, waarin de volledige lijn staat voor differentiële signaalgolf.

Als een faseplaatsing plaatsvindt van de positieve fase-aansluiting naar de negatieve fase-aansluiting, zal er een verandering zijn in het verschil tussen het positieve fase-aansluitsignaal en het negatieve fase-aansluitsignaal aan de op- of neerwaartse flank en deze verandering zal veranderen met de verandering van fase. Tr wordt gebruikt om de kortere tijd tussen stijgende en dalende tijd aan te duiden. Het kan worden aangegeven dat wanneer de faseplaatsing minder is dan punt twee van Tr , signaalvervorming is relatief klein en de toename van faseplaatsing leidt tot sterke vervorming van differentiële golfvorm. Wanneer faseplaatsing Tr . overschrijdt , zal niet-monotoon gebied plaatsvinden op golfvorm. Hier is het niet-monotone gebied een rechte lijn. Voor praktische signalen kunnen vanwege reflecties echter grote ups en downs plaatsvinden in een niet-monotoon gebied, waarbij een interferentiepuls wordt gevormd die leidt tot valse triggering, wat moet worden vermeden. Bovendien wordt de bovenrand van de differentiële golfvorm langzaam naarmate de faseplaatsing toeneemt, wat kan leiden tot onvoldoende vestigingstijd voor het gegevenssignaal en kan leiden tot onvoldoende houdtijd voor het kloksignaal.

• Invloed op common-mode signaal

De faseplaatsing van een enkelvoudig terminalsignaal heeft geen invloed op de differentiële golfvorm, maar verandert de golfvorm van common-mode-signalen. Wanneer faseplaatsing plaatsvindt bij het positieve aansluitsignaal, vindt golfverandering plaats naar common-mode-signalen. Er kan worden aangegeven dat het fluctuatiebereik gerelateerd is aan de hoeveelheid faseplaatsing. Wanneer de hoeveelheid faseplaatsing respectievelijk 0,05Tr . is , 0.1Tr , 0.2Tr en 0,5Tr , het fluctuatiebereik van de gewone modus is respectievelijk 5%, 10%, 20% en 50% van het oorspronkelijke fluctuatiebereik. Wanneer fase toeneemt tot Tr of meer, de fluctuatie zal toenemen tot ongeveer 100%, dat is het hoogste fluctuatiebereik. De verandering van het common-mode-signaal kan leiden tot EMI-problemen en aangezien het common-code-signaal onder veel omstandigheden niet wordt ontvangen op de terminal, zal er reflectie ontstaan op de ontvangende terminal, wat leidt tot signaalsignaal. Daarom moet het fluctuatiebereik van het common-mode-signaal zo veel mogelijk worden verkleind.

Concluderend kan een te grote relatieve vertraging tussen differentiële paren valse triggering van signalen, signaalreflectie, EMI en tijdsequencing-problemen veroorzaken. De invloedsgraad van het relatieve vertragingssignaal hangt echter af van de schaalfactor die compatibel is met signaal Tr . Wanneer de schaalfactor 0,05 is, kan vervorming van differentiële signalen bijna worden genegeerd. Voor common-mode-signalen, wanneer de schaalfactor 0,05 is, kan de spanningsfluctuatie van common-mode-signalen echter met ongeveer 5% worden geregeld. Dan, zelfs in de situatie van volledige reflectie, is de reflectiespanning gestapeld op signaallijnen slechts 10% van de oorspronkelijke fluctuatie, wat meestal een acceptabele waarde is. Daarom kan tijdens het ontwerp van hogesnelheidsprintplaten de relatieve vertraging van de differentiële signaallijn in de routeringsregelregels worden ingesteld op 0,05 Tr die in staat is om aan de eis van signaalintegriteit te voldoen.

Bepaling van relatieve vertragingscategorie

Op basis van de bovenstaande analyse ligt de sleutel voor het bepalen van de differentiële isometrische categorie, dat wil zeggen de bepaling van de relatieve vertraging van differentiële paren, in de bepaling van Tr verwijzend naar de kleinste waarde tussen de bovenste en onderste tijd van differentiële signalen. De output van stijgtijd en daaltijd is eigenlijk de output van een combinatie van impedantie en capaciteit. Daarom is de stijg-/daaltijd zonder belasting eigenlijk inherente stijg-/daaltijd.

De volgende drie methoden kunnen worden toegepast om de waarde van Tr . te verkrijgen :

• Stijg-/daaltijd kan direct worden verkregen uit de handleidingen van componenten. In de meeste situaties wordt deze parameter echter niet verstrekt.

• Waarde van Tr kan worden verkregen uit Ramp-sleutelwoorden van het component IBIS-model (Input/Output Buffer Informational Specification). Stijg-/daaltijdparameters onder Ramp-trefwoorden worden over het algemeen gemeten aan de uitgangspoort die is verbonden met een weerstand van 50Ω, die meestal 20% tot 80% van de uiteindelijke spanningstijd is. Aangezien de parameters worden verkregen zonder rekening te houden met de invloed van het pakket, is het strikt voor ons om de stijg-/daaltijd te gebruiken als de waarde van Tr .

• De waarde van Tr kan worden geschat op basis van de minimale klokfrequentie of maximale klokfrequentie van uitgangssignalen. Omdat de distributieve stijgende flank ongeveer 10% van de klokfrequentie is in de meeste snelle digitale systemen, is de waarde van Tr kan worden geschat met de opgegeven minimale klokperiode Tclk op basis van de formule:Tr =Tclk x 10%.

De geschatte waarde die wordt verkregen via de klokperiode is meestal streng omdat parasitaire parameters van het pakket of het laden van componenten de inherente stijg-/daaltijd in transistors aanzienlijk vertragen.

In het praktische werk verstrekken circuitontwerpers in de meeste situaties geen informatie over Tr aan PCB-lay-outingenieurs die slechts enkele dubbelzinnige eisen krijgen op het gebied van differentiële isometrische besturing. De derde methode biedt ongetwijfeld een eenvoudig schema voor PCB-lay-outingenieurs, zolang de hoogste klokfrequentie op de signaallijn wordt verkregen. De hoogste klokfrequentie wordt beschouwd als de meest betrouwbare ontwerpparameter voor circuitontwerpers en wordt meestal aan het begin van het PCB-ontwerp aan PCB-lay-outingenieurs geleverd.

De derde methode leidt meestal tot een lijst met referentiewaarden binnen de categorie van relatieve vertragingsregeling tussen differentiële paren, zoals weergegeven in onderstaande tabel.

| Klokfrequentie/ns | Klokfrequentie/MHz | Relatieve vertragingscategorie/ps | Transmissielijnlengte/mil |

| 3,75 | 266 | 18.8 | 105 |

| 3 | 333 | 15 | 84 |

| 2,5 | 400 | 12,5 | 70 |

| 1.87 | 533 | 9,4 | 52 |

| 1,5 | 667 | 7,5 | 42 |

| 1,25 | 800 | 6.3 | 35 |

Simulatieverificatie

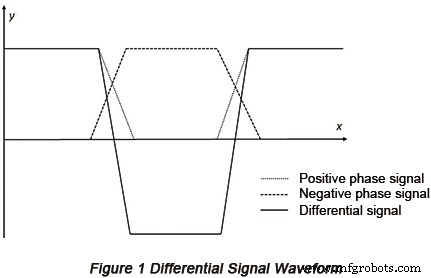

Neem DQS (Data Strobe) differentieel signaal tussen TSM320 en MT41J256M16 als voorbeeld. Cadence simulatiesoftware wordt toegepast om DOS-signaal naar DRR3-geheugen te verzenden om de geheugenbesturingschip te simuleren, de invloed ervan op de vasthoudtijd van het gegevenssignaal te analyseren en de bovenstaande analyse te verifiëren. Simulatiecircuit wordt getoond in Afbeelding 2 hieronder.

Op basis van figuur 2 is de referentiespanning van de uitgangspinnen 1,5 V; geheugenbesturingschip is rechtstreeks verbonden met geheugenchip via ODT (On-Die Termination) -modus met transmissielijn van 800mil; differentiële impedantie is 100Ω en simulatie klokfrequentie van 800MHz. Een transmissielijn van 50Ω is serieel verbonden met de positieve fase-aansluiting van DQS om het discrepantieverschijnsel van differentiële paren te simuleren. In de situatie van isometrische verschillen is de lengte van de enkelvoudige transmissielijn van 50Ω 0mil.

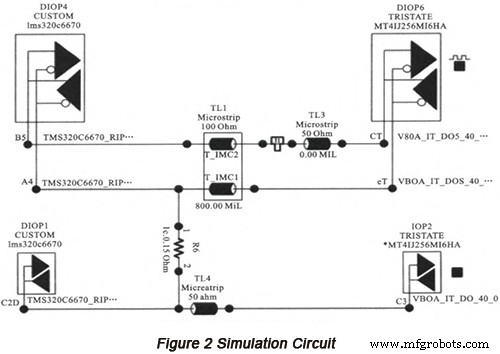

Simulatie wordt uitgevoerd op het differentiële isometrische circuit. Figuur 3 illustreert het uitgangssignaal aan de positieve fase-aansluiting van differentiële signalen. Door meting is de stijgtijd ongeveer 216ps terwijl de valtijd 219ps is, dus de minimale stijg-/daaltijd Tr zou 216ps moeten zijn.

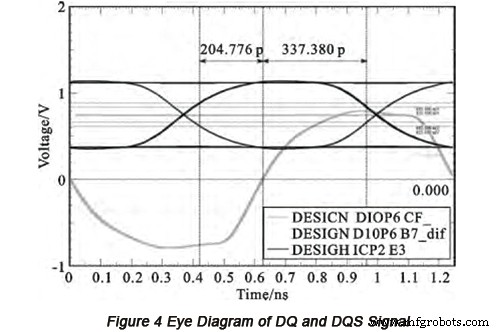

Figuur 4 is een oogdiagram van datasignaal DQ en poortsignaal DQS door simulatie met de vestigingstijd 205ps en houdtijd 337ps. Volgens de omloopsnelheid van DQS- en DQ-signalen door middel van simulatie en gebaseerd op de gegevenshandleiding, moet de minimale totstandbrengingstijd van gegevenssignalen door de ontvangende terminal 85 ps zijn en is de minimale houdtijd 95 ps. Daarom is de overmaat van de minimale vestigingstijd 120ps en de houdtijd 242ps.

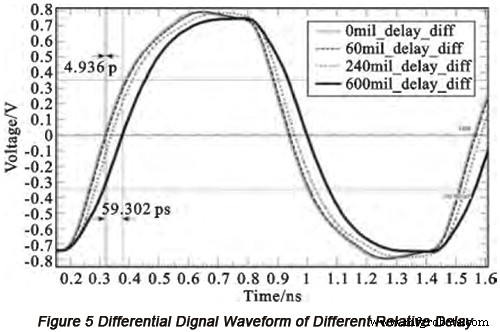

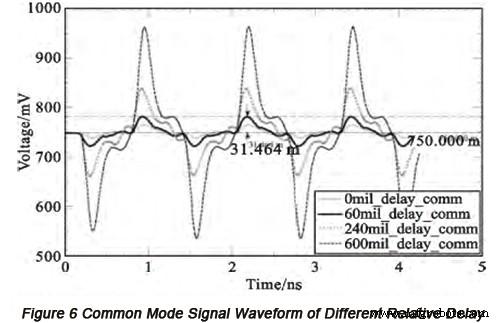

De situatie van het bestaan van 0.05Tr fase plaatsing, 0.2Tr faseplaatsing en 0,5Tr faseplaatsing op de positieve faseterminal moet worden overwogen. Het circuit kan worden gesimuleerd met een enkelvoudige transmissielijnlengte die respectievelijk is ingesteld op 60mil, 240mil en 600mil. Differentiële signaalgolfvorm en common-mode signaalgolfvorm door simulatie gedurende 4 keer worden geïllustreerd in figuur 5 en 6.

Op basis van figuur 5 is vervorming het minimum bij relatieve vertragingen van 0,05Tr en 0.2Tr spelen zich af. Vooral wanneer de relatieve vertraging 0,05Tr . is , alleen plaatsing van ongeveer 5 ps van differentieel signaal naar differentiële signaalgolfvorm zonder relatieve vertraging, zodat de overmaat van het gegevenssignaal wordt verhoogd met ongeveer 5 ps, terwijl de overmaattijd met 5 ps wordt verminderd. Hoewel de overmaattijd voor het vasthouden wordt verminderd, is deze hoeveelheid plaatsing zo klein voor de vasthoudtijd van 242ps. Tijdsvolgorde kan worden vermeden. Voor de situatie waarin de relatieve vertraging 0,5Tr . is , heeft de plaatsing van de DQS-signaalgolfvorm ongeveer 60ps bereikt. Hoewel deze plaatsing nog steeds in de categorie overmaat valt, moet er voldoende aandacht aan worden besteed.

Op basis van figuur 6 leidt de toename van faseplaatsing tot duidelijke periodieke fluctuatie op golven en de geleidelijke toename van het bereik. Wanneer de relatieve vertraging respectievelijk 0,05Tr . is , 0.2Tr en 0,5Tr , de gemeten piekwaarde van het common-mode signaal is respectievelijk 61mV, 176mV en 430mV, waarvan de hoogste waarde zeven keer de laagste is. Het grootste fluctuatiebereik is respectievelijk 4,3%, 12% en 29%.

Concluderend, het simulatieresultaat is compatibel met het resultaat verkregen door analyse van wiskundige functiediagrammen. Wanneer de relatieve vertraging tussen differentiële paren minder is dan 0,05Tr , de invloed op signalen is vrij klein.

De minimale klokperiode van het uitgangssignaal op de uitgangsklem wordt toegepast om de relatieve vertragingsbesturingscategorie te schatten. Op basis van de componentenhandleiding is de minimale klokperiode van componenten 1,25 ns met een klokfrequentie van 800 MHz. Volgens tabel 1 moet de relatieve vertraging binnen 6,3 ps worden geregeld met een transmissielijnlengte van 35 mil. Blijkbaar is deze waarde veel kleiner dan de controlecategorie van de relatieve vertraging van 0,05Tr door middel van simulatie. Daarom is de geschatte relatieve vertragingscontrolecategorie relatief conservatief, wat specifieker is dan het gesimuleerde resultaat.

Nuttige bronnen

• Onderzoek naar high-speed PCB-ontwerp in ingebed applicatiesysteem

• Hoe beeldvlakken te ontwerpen voor high-speed PCB's

• High-speed PCB-ontwerpuitdagingen voor signaalintegriteit en hun oplossingen

• Simulatie PCB met OrCAD PSpice

• Full Feature PCB-productieservice van PCBCart - Meerdere opties met toegevoegde waarde

• Geavanceerde PCB-assemblageservice van PCBCart - Start vanaf 1 stuk

Industriële technologie

- Richtlijnen voor RF- en magnetronontwerp

- PCB-materialen en ontwerp voor hoogspanning

- Flex- en Rigid-Flex Bend-mogelijkheden in PCB-ontwerp

- Stappen en proces Leer om uw PCB-ontwerp te beschermen

- Tegenslagen en oplossingen in RF PCB-ontwerp

- 3 routeringstechnieken op PCB high-speed signaalcircuitontwerp

- Tips voor snelle lay-out

- Onderdrukkingsmethode voor signaalreflectie in high-speed PCB-lay-out

- Discussie over voeding en aarde in elektromagnetische compatibiliteit van PCB

- Signaalintegriteitsanalyse en PCB-ontwerp op high-speed digitaal-analoog gemengd circuit

- Uitdagingen bij het ontwerpen van high-speed PCB's voor signaalintegriteit en hun oplossingen