Ontwerp en implementatie van High Density FDR Interconnection Switch Boards

Tegenwoordig heeft de transmissiesnelheid van een krachtig computerinterconnectienetwerk met de toepassing van snelle seriële transmissie zich ontwikkeld tot FDR (Fourteen Data Rate, 14Gb/s), de 4e generatie van de primaire SDR (Single Data Rate, 2.5Gb/ s), DDR (Double Data Rate, 5Gb/s) en QDR (Quad Data Rate, 10Gb/s). Het ontwerp van PCB (Printed Circuit Board) met interconnectie- en schakelbord en interfacekaarten die essentieel zijn voor de vorming van internet, is het hogesnelheids- en hoogfrequente veld van FDR binnengekomen. Aangezien de stijgtijd van het FDR-signaal drastisch is teruggebracht tot de grootte van 10ps, is een reeks problemen met betrekking tot signaalintegriteit de belangrijkste kenmerken geworden om de mogelijkheid van implementatie van functionaliteit en betrouwbare werking te bepalen, zoals verzwakking, overspraak, reflectie, elektromagnetische interferentie enz. Op basis van de kenmerken van FDR-interconnectiechips, waaronder meerdere poorten, meerdere kanalen, meerdere vermogenscategorieën en een hoog energieverbruik, moeten er altijd meerdere interconnect-chips worden geïntegreerd op een enkele interconnectiekaart om de doorvoersnelheid te verhogen. Op een bord met beperkte ruimte moet aan de ene kant aan een aantal eisen worden voldaan, waaronder componentenlay-out en warmteafvoer, routering met hoge dichtheid, lange afstandstransmissie over de achterkant van het bord en integriteit van allerlei soorten signalen. Aan de andere kant moeten sommige elementen in overweging worden genomen, waaronder de ontwerpperiode van PCB's, beperkingen op de fabricagetechniek van PCB's en kostenbeheersing. Daarom is het uiterst moeilijk voor ontwerpimplementatie en simulatieverificatie. Gebaseerd op een PCB-ontwerpvoorbeeld van FDR-interconnectie en schakelbord, bevat dit artikel enkele optimalisatiemethoden op het gebied van substraatmateriaalselectie, stapelontwerp, routeringsregels en anti-interferentieontwerp om het integriteitsprobleem van allerlei soorten signalen op te lossen in het proces van FDR high-speed PCB-ontwerp.

Verzwakkingskenmerk en selectie van substraatmateriaal

Voor FDR hoogfrequente signalen is transmissielijnverlies het probleem met betrekking tot signaalintegriteit. Wanneer FDR-signalen worden verzonden van de verzendende terminal naar de ontvangende terminal langs verbindingskanalen, omdat de hoogfrequente verzwakking veel groter is dan de laagfrequente verzwakking, heeft er ernstige vervorming plaatsgevonden in de signaalgolfvorm die bij de ontvangende terminal aankomt. De vervorming wordt hoofdzakelijk ingedeeld in twee aspecten:de spanningszwaai van signalen is sterk afgenomen, terwijl er een slechte degradatie heeft plaatsgevonden om de opgaande flank te signaleren. De eerste beperkt de transmissieafstand van signalen, terwijl de laatste leidt tot interferentie tussen codes. Transmissielijnverlies A kan worden beschouwd als de som van geleiderverlies Acond en diëlektrisch verlies Adiel zoals weergegeven in formule (1):A =Adiel + Acond .

Geleiderverlies verwijst naar het verlies veroorzaakt door de seriële weerstand op de koperen geleider tussen het signaalpad en het retourpad. In de situatie van hoge frequentie zorgt het skin-effect ervoor dat de stroom aan het oppervlak van de omringende koperen geleiders vloeit. Met de toename van de equivalente seriële weerstand van koperen geleiders, zal het geleiderverlies toenemen met de toename van de frequentie die positief evenredig is met de vierkantswortel van de frequentie, die wordt geïllustreerd in formule (2): .

.

Diëlektrisch verlies verwijst naar het verlies gegenereerd door het medium van substraatmateriaal, voornamelijk bepaald door het attribuut van materiaal en niet gerelateerd aan geometrische constructie inclusief geleiderbreedte, positief evenredig met de frequentie, die wordt weergegeven in formule (3): .

.

Op basis van formule (2) kan de toename van de lijnbreedte het verlies van geleiders verminderen. In het praktische PCB-ontwerp kan de breedte van geleiders echter nooit oneindig breed zijn als gevolg van de beperking van de afstand tussen de pinnen, het bord, het aantal signaallagen en de impedantie. De algemeen toegepaste geleiderbreedte/afstand/breedte in FDR-ontwerp is gewoonlijk 7mil/7mil/7mil of 8mil/10mil/8mil. Wanneer de geleiderbreedte hetzelfde is, is het geleiderverlies positief evenredig met de geleiderlengte, zonder enige relatie met materiaal. Om het totale transmissieverlies te verminderen, hoeft daarom alleen rekening te worden gehouden met diëlektrisch verlies. Op basis van formule (3) is diëlektrisch verlies evenredig met de dissipatiefactor en de toepassing van kleine dissipatiefactoren kan nuttig zijn voor het verminderen van diëlektrisch verlies, wat leidt tot verlies van algehele transmissie.

Tabel 1 geeft een overzicht van de attribuutparameters van drie gewone high-speed plaatmateriaal en verlieswaarden berekend volgens formule (1), (2) en (3) wanneer de transmissiesnelheid 14 Gb/s is, de geleiderbreedte 8mil en de impedantie 50Ω.

| Parameters plaatmateriaal | FR4 | Nelco4000-13SI | Megtron6 |

| ADMIN@MFGROBOTS.COM | 0,02 | 0,008 | 0,004 |

| ADMIN@MFGROBOTS.COM | 4.10 | 3.200 | 3.600 |

| Avoorwaarde @7GHz/inch | 0,24 | 0,240 | 0,240 |

| Adiel @7GHz/inch | 0,65 | 0,230 | 0.120 |

| ADMIN@MFGROBOTS.COM/in | 0,89 | 0.470 | 0.360 |

| ADMIN@MFGROBOTS.COM/30in | 27.00 | 14.000 | 11.000 |

| Relatieve kosten | 1.00 | 3.500 | 8.000 |

Het kan worden aangegeven dat met een transmissiesnelheid van 14 Gb/s en een transmissielengte van 30 inch, het totale transmissieverlies van de Nelco4000-13SI ongeveer 14 dB is, terwijl de spanningsverzwakking die een typische FDR-chip kan weerstaan, in het bereik van 20 dB tot 25dB. Daarom kan dit type bordmateriaal worden toegepast in FDR-interconnectieschakelbordontwerp met een transmissieafstand van minder dan 30 inch. De algehele transmissieverzwakking van FR4 is echter ongeveer 27 dB en FR4 kan niet worden toegepast voor FDR-ontwerp van langeafstandsontwerp, maar FDR-interconnectie-interfacekaarten met korte transmissieafstand mogen FR4 selecteren om de kosten te verlagen. Wat betreft Megtron6 waarvan de algehele transmissieverzwakking het kleinst is, het heeft de hoogste kosten en de toepassing ervan in FDR leidt tot hogere systeemarchitectuurkosten. Kortom, voor hoogfrequente PCB's is plaatmateriaal de basis en bepaalt de selectie van plaatmateriaal de transmissielengte van signalen.

Lay-out en stapelontwerp

Voor PCB-ontwerp moet eerst rekening worden gehouden met de structuur van de printplaat en de stapel. Gewoonlijk is het patroon en de vorm van de printplaat bepaald en de bepaling van het stapelnummer ligt in de signaalfrequentie, de pindichtheid van de printplaat, de fabricagekosten van de printplaat, de productieperiode en de betrouwbaarheidsvereisten. FDR-interconnectieschakelborden hebben een hoge frequentie en dichtheid en het aanbrengen van meerlaagse borden is de noodzakelijke stap om interferentie te verminderen. Daarnaast is het bepalen van het stapelnummer cruciaal.

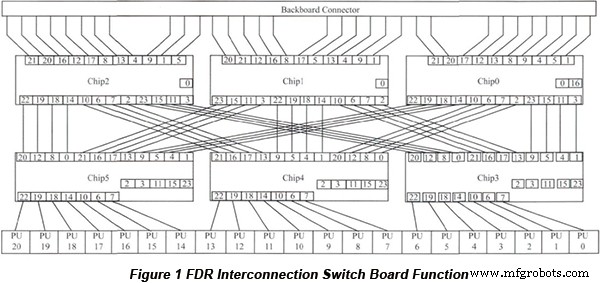

Er zijn 24 poorten op de FDR-interconnectiechip en elke poort heeft 8 Tx-kanalen en 8 Rx-kanalen in de bedieningsmethode van intercoupling. 6 interconnectie-chips en 3 downlink-chips worden toegepast door FDR-interconnectiekaart en 32 poorten zijn toegankelijk via de backboard-connector. 3 uplink-chips hebben toegang tot 21 poorten via QSFP (Quad Small Form-factor Pluggable) optische vezels. Uplink-chip en downlink-chip zijn met elkaar verbonden via 4 poorten, zoals weergegeven in afbeelding 1.

FDR bevat het pakket van BGA (Ball Grid Array) met een oppervlakte van 50 mm x 50 mm, 1157 pinnen en een afstand van 1,0 mm en P/N-pinnen bij de poorten van Tx en Rx zijn verdeeld volgens 3 concentrische cirkels. Theoretisch kunnen 3 signaallagen worden toegepast om alle pinnen op alle poorten uit BGA te leiden. Met de volgende twee elementen in overweging, kunnen twee signaallagen worden gebruikt om toegang te krijgen tot een groep pinnen van concentrische cirkels.

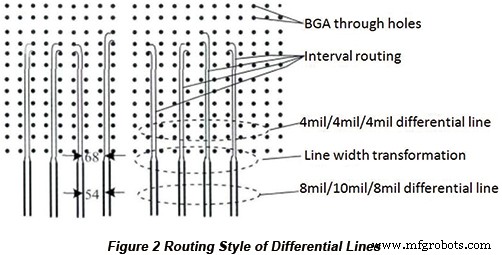

a. Vanwege de beperking van de afstand, is de lijnbreedte/afstand/breedte van differentiële lijnen 4mil/4mil/4mil en het zal worden uitgebreid tot 8mil/10mil/8mil die uit BGA komen en de afstand tussen differentiële lijnparen mag niet minder zijn dan 50 miljoen. Daarom moet een paar differentiële lijnen een breedte van 2 mm innemen en 48 paar signalen bevinden zich langs de rand met de grootste dichtheid. Het is dus moeilijk om deze methode te implementeren.

b. De afstand tussen de BGA-pinnen is 1 mm. Als een signaallaag wordt toegepast om toegang te krijgen tot een groep concentrische cirkelsignalen, is de afstand tussen differentiële lijnparen onder BGA slechts 14 mil, wat verre van de vereiste 50 mil is. Bovendien is de maximale parallelle routeringslengte slechts 20 mm, wat enige overspraak zal veroorzaken.

Om de bovengenoemde negatieve factoren te vermijden, worden twee signaallagen toegepast om toegang te krijgen tot een groep concentrische cirkelsignalen en moet het differentiële signaal bij elke signaallaag uit BGA worden geleid met een tussenruimte van 50 mil. Daarom zijn er ten minste 6 lagen nodig voor FDR-interconnectiekaarten om alle differentiële signalen uit BGA te laten leiden. Met de connectiviteit en routering van het bord en voldoende bordoppervlak voor de uitwisseling van koppelcondensatoren, worden 8 interne signalen en 22-laags stack toegepast.

Overspraakanalyse en reductiemaatregelen

Overspraak is de eerste overweging in termen van circuitontwerp met hoge snelheid en hoge dichtheid. Wanneer spanning en stroom in de aanvalslinie veranderen, zal elektromagnetische koppeling plaatsvinden door onderlinge capaciteit en wederzijdse inductantie tussen offensieve linie en slachtofferlijn. De overspraak die naar de transmissieterminal langs de slachtofferlijn stroomt, wordt near-terminal overspraak genoemd, terwijl de overspraak die naar de ontvangstterminal langs de slachtofferlijn stroomt, verre-terminale overspraak wordt genoemd. Over het algemeen moet de totale ruisspanning op de slachtofferlijn worden geregeld op minder dan 5% van de signaalspanning. Het is het beste om het overspraakbudget van een enkelzijdige offensieve lijn binnen 1% te houden, rekening houdend met een andere geluidsbron en offensieve lijn rond twee zijden van de slachtofferlijn.

De belangrijkste punten voor het verminderen van overspraak zijn:

a. De afstand tussen de aanvalslijn en de slachtofferlijn moet worden vergroot en de lengte van de parallelle routering moet worden verkleind.

b. Geïntegreerde aarde wordt toegepast als het terugkerende pad van signalen. Volgens de empirische wet, voor de striplijn van 50Ω, wanneer de afstand drie keer de lijnbreedte is, is near-end overspraak ongeveer 0,5%. Voor microstriplijnen van 50Ω, wanneer de afstand drie keer de lijnbreedte is, is near-end overspraak ongeveer 1%. De verre overspraak op striplijnen of volledig ingebedde microstriplijnen is bijna nul en de verre overspraakpolariteit van microstrip-transmissielijnen is negatief en is relatief groot omdat de invloed van inductieve koppeling groter is dan capacitieve koppeling.

• Intervalroutering

In dit ontwerp is de differentiële impedantie van de differentiële hogesnelheidslijn 100Ω. Op basis van de Si9000-veldoplosser wordt de lijnbreedte/afstand/lijnbreedte berekend op 8mil/10mil/8mil. Hoe breder de lijn, hoe kleiner de demping en de afstand van 10 mil is om de differentiële impedantie van 100Ω te behouden. Dit type differentiële lijn wordt toegepast buiten het BGA-chipgebied. Om overspraak te verminderen, is de afstand tussen twee paar differentiële lijnen maar liefst 80mil. The spacing between pins of interconnection chip in this article is 1mm and the through hole size limitation of BGA makes the line width/spacing/line width of the differential line in the BGA chip area 4mil/4mil/4mil. Although the differential impedance of this type of differential line is 100Ω as well, the lead loss is big, requiring differential line of 4mil/4mil/4mil to be transformed into 8mil/10mil/8mil as soon as it enters BGA chip area. In order to reduce crosstalk, differential line of 4mil/4mil/4mil in BGA chip area applies the way of interval routing to ensure the spacing between two pairs of differential lines more than 50mil as well, which is shown in Figure 2.

• Differential holes

Specific differential holes are set in this design for the application of exchange coupling capacitance on the connection surface layer. Ground holes have to be placed beside differential holes to provide backflow channel for returning path. Design of four ground holes features the best effect and two ground holes can be also applied when the area of board is limited. Besides, measures such as back drilling and internal pad eliminationhave should be taken to differential holes to reduce the impedance change at differential holes in order to decrease crosstalk and reflection.

• Preventing Tx and Rx from being routed in the same layer

In order to reduce crosstalk, Tx differential line should be routed in the different layer from Rx differential line. Here, Tx refers to the source terminal of differential line while Rx refers to the receiving terminal of differential line. If both of them have to be routed in the same layer, the spacing between them has to be over 5mm to ensure safety.

• 20H rule

In the PCB circuit with high frequency and high speed, RF energy is coupled by PCB power layer and ground layer and edge magnetic flux leakage is generated between power layer and ground layer. The radio RF energy can be radiated to the free space. 20H rule indicates that if there are high-speed currents on the board, there are electromagnetic fields associated with them. In the design of this article, the distance between all the routings and board edge should be at least 20 times of line width and the distance between high-speed differential holes and power plane cut-off lines is at least 5mm.

• Routing on the surface layer

In the design of high-frequency PCBs, with the relatively big far-end crosstalk between microstrip lines and strip lines considered, high-speed differential lines are prohibited on the surface layer. In the design of this article, at most 8 internal routing layers are required owing to the limitation of manufacturing craft. Moreover, the terminal arrangement limitation of interconnection chip makes it impossible for internal layers only to implement the connections of the interconnection differential lines between 6 chips inside connection board.

Helpful Resources

• Something You Must Know about HDI

• History of High-Density Packaging Technology

• 3 Keys to Designing a Successful HDI PCB

• Advantages of HDI Printed Circuit Boards

• Full Feature PCB Manufacturing Service from PCBCart - Multiple Value-added options

• Advanced PCB Assembly Service from PCBCart - Start from 1 piece

Industriële technologie

- Switch contactontwerp

- Hoe kabels en harnassen te documenteren

- Wat is Power Hammers?- Types, ontwerp en bediening

- High-tech op maat gemaakte printplaten

- Richtlijnen voor RF- en magnetronontwerp

- PCB-materialen en ontwerp voor hoogspanning

- Flex- en Rigid-Flex Bend-mogelijkheden in PCB-ontwerp

- Tegenslagen en oplossingen in RF PCB-ontwerp

- Wolfraam

- Het ontwerp- en implementatieproces voor fabrieksautomatisering

- De opkomst van High Density Interconnect PCB's