Logische signaalspanningsniveaus

Ingangsspanningen voor logische poorten

Logische poortcircuits zijn ontworpen om slechts twee soorten signalen in en uit te voeren:"hoog" (1) en "laag" (0), zoals weergegeven door een variabele spanning:volledige voedingsspanning voor een "hoge" toestand en nulspanning voor een "lage" toestand. In een perfecte wereld zouden alle signalen van logische circuits bestaan bij deze extreme spanningslimieten en er nooit van afwijken (d.w.z. minder dan volledige spanning voor een "hoge" of meer dan nulspanning voor een "lage").

In werkelijkheid bereiken logische signaalspanningsniveaus echter zelden deze perfecte limieten als gevolg van verdwaalde spanningsdalingen in de transistorschakelingen, en daarom moeten we de signaalniveaubeperkingen van poortcircuits begrijpen terwijl ze proberen signaalspanningen te interpreteren die ergens tussen

Spanningstolerantie van TTL-poortingangen

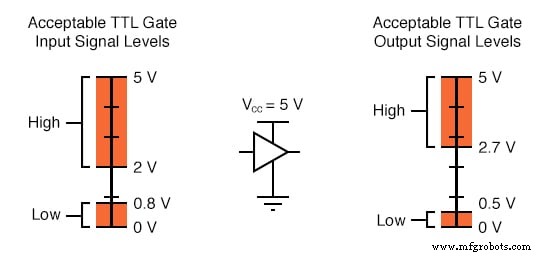

TTL-poorten werken op een nominale voedingsspanning van 5 volt, +/- 0,25 volt. Idealiter zou een TTL "hoog" signaal precies 5,00 volt zijn en een TTL "laag" signaal precies 0,00 volt.

Echte TTL-poortcircuits kunnen echter niet zulke perfecte spanningsniveaus uitvoeren en zijn ontworpen om "hoge" en "lage" signalen te accepteren die aanzienlijk afwijken van deze ideale waarden.

"Aanvaardbare" ingangssignaalspanningen variëren van 0 volt tot 0,8 volt voor een "lage" logische toestand en 2 volt tot 5 volt voor een "hoge" logische toestand.

"Aanvaardbare" uitgangssignaalspanningen (spanningsniveaus gegarandeerd door de poortfabrikant over een gespecificeerd bereik van belastingsomstandigheden) variëren van 0 volt tot 0,5 volt voor een "lage" logische toestand en 2,7 volt tot 5 volt voor een "hoge" logische toestand :

Als een spanningssignaal tussen 0,8 volt en 2 volt naar de ingang van een TTL-poort zou worden gestuurd, zou er geen bepaalde reactie van de poort zijn. Een dergelijk signaal zou als onzeker worden beschouwd , en geen enkele fabrikant van logische poorten zou garanderen hoe hun poortcircuit een dergelijk signaal zou interpreteren.

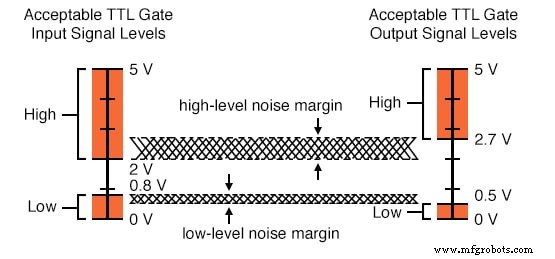

TTL-ruismarge

Zoals u kunt zien, zijn de toelaatbare bereiken voor uitgangssignaalniveaus smaller dan voor ingangssignaalniveaus, om ervoor te zorgen dat elke TTL-poort die een digitaal signaal afgeeft aan de ingang van een andere TTL-poort, spanningen zal verzenden die acceptabel zijn voor de ontvangende poort. Het verschil tussen het toelaatbare uitvoer- en invoerbereik wordt de ruismarge genoemd van de poort.

Voor TTL-poorten is de ruismarge op laag niveau het verschil tussen 0,8 volt en 0,5 volt (0,3 volt), terwijl de ruismarge op hoog niveau het verschil is tussen 2,7 volt en 2 volt (0,7 volt). Simpel gezegd, de ruismarge is de piekhoeveelheid valse of "ruis" -spanning die kan worden gesuperponeerd op een zwak uitgangsspanningssignaal van de poort voordat de ontvangende poort het verkeerd kan interpreteren:

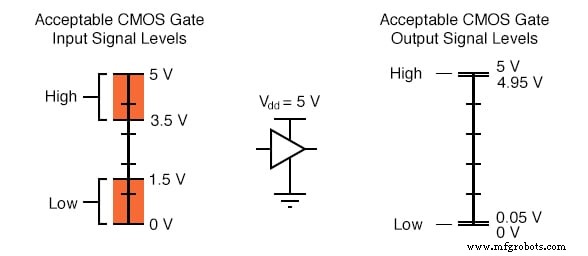

Spanningstolerantie van CMOS-poortingangen

CMOS-poortcircuits hebben invoer- en uitvoersignaalspecificaties die behoorlijk verschillen van TTL. Voor een CMOS-poort die werkt op een voedingsspanning van 5 volt, variëren de acceptabele ingangssignaalspanningen van 0 volt tot 1,5 volt voor een "lage" logische toestand en 3,5 volt tot 5 volt voor een "hoge" logische toestand.

"Aanvaardbare" uitgangssignaalspanningen (spanningsniveaus gegarandeerd door de poortfabrikant over een gespecificeerd bereik van belastingsomstandigheden) variëren van 0 volt tot 0,05 volt voor een "lage" logische toestand en 4,95 volt tot 5 volt voor een "hoge" logische toestand :

CMOS-ruismarge

Uit deze cijfers moet duidelijk zijn dat CMOS-poortcircuits veel grotere ruismarges hebben dan TTL:1,45 volt voor CMOS-marges op laag en hoog niveau, versus maximaal 0,7 volt voor TTL. Met andere woorden, CMOS-circuits kunnen meer dan tweemaal de hoeveelheid gesuperponeerde "ruis"-spanning op hun ingangslijnen verdragen voordat er signaalinterpretatiefouten zullen optreden.

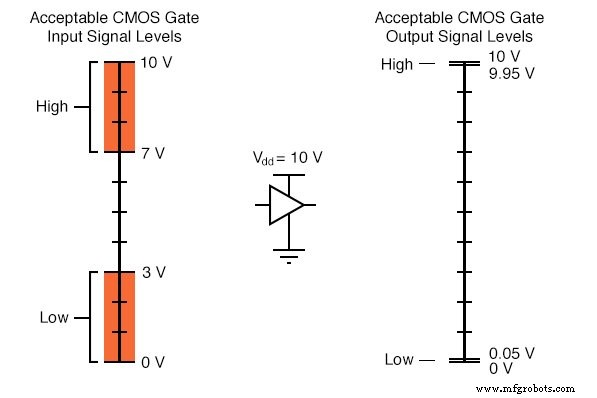

Ruismarges bij hogere bedrijfsspanningen

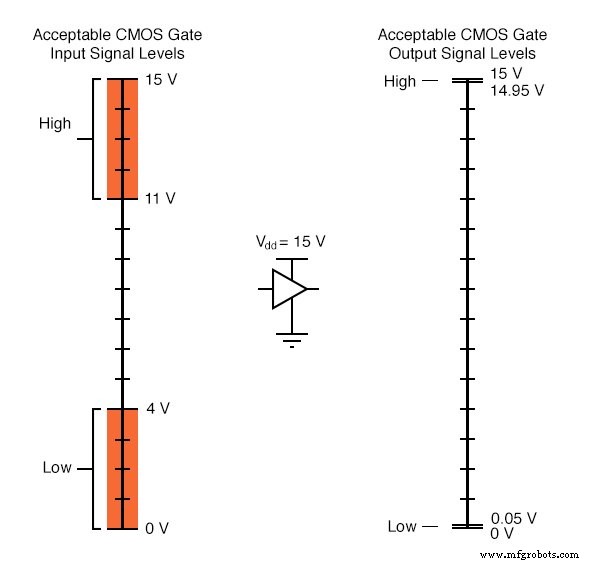

De CMOS-ruismarges worden nog groter bij hogere bedrijfsspanningen. In tegenstelling tot TTL, dat beperkt is tot een voedingsspanning van 5 volt, kan CMOS worden gevoed door spanningen tot 15 volt (sommige CMOS-circuits zo hoog als 18 volt).

Hier worden de acceptabele "hoge" en "lage" toestanden weergegeven, zowel voor invoer als uitvoer, van CMOS-geïntegreerde schakelingen die werken op respectievelijk 10 volt en 15 volt:

De marges voor acceptabele "hoge" en "lage" signalen kunnen groter zijn dan in de vorige afbeeldingen is weergegeven. Wat wordt weergegeven, vertegenwoordigt de prestaties van het "worst-case" ingangssignaal, gebaseerd op de specificaties van de fabrikant. In de praktijk kan blijken dat een poortschakeling "hoge" signalen van aanzienlijk minder spanning en "lage" signalen van aanzienlijk hogere spanning tolereert dan de hier gespecificeerde.

Omgekeerd zijn de extreem kleine uitgangsmarges die worden getoond - die uitgangstoestanden voor "hoge" en "lage" signalen garanderen tot binnen 0,05 volt van de "rails" van de voeding - optimistisch. Dergelijke "vaste" uitgangsspanningsniveaus zijn alleen waar voor omstandigheden van minimale belasting. Als de poort aanzienlijke stroom naar een belasting toevoert of laat dalen, kan de uitgangsspanning deze optimale niveaus niet handhaven vanwege de interne kanaalweerstand van de uiteindelijke uitgangs-MOSFET's van de poort.

Spanningsdrempels

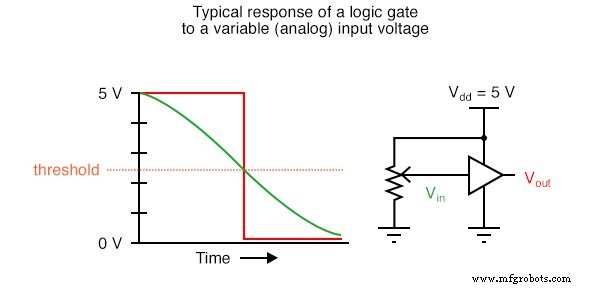

Binnen het "onzekere" bereik voor elke poortinvoer, zal er een scheidspunt zijn dat het werkelijke "lage" ingangssignaalbereik van de poort scheidt van het werkelijke "hoge" ingangssignaalbereik. Dat wil zeggen, ergens tussen het laagste "hoge" signaalspanningsniveau en het hoogste "lage" signaalspanningsniveau gegarandeerd door de poortfabrikant, is er een drempelspanning waarbij de poort eigenlijk verander de interpretatie van een signaal van "laag" of "hoog" of vice versa. Voor de meeste poortcircuits is deze niet-gespecificeerde spanning een enkel punt:

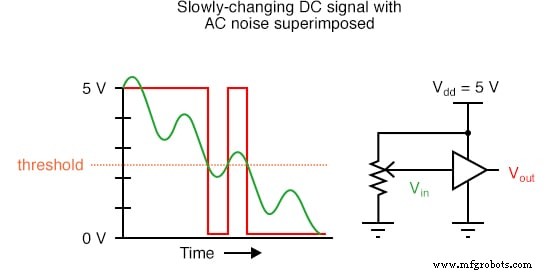

Ingangen met AC-ruis

In de aanwezigheid van AC "ruis" spanning gesuperponeerd op het DC-ingangssignaal, zal een enkel drempelpunt waarop de poort zijn interpretatie van logisch niveau verandert, resulteren in een onregelmatige output:

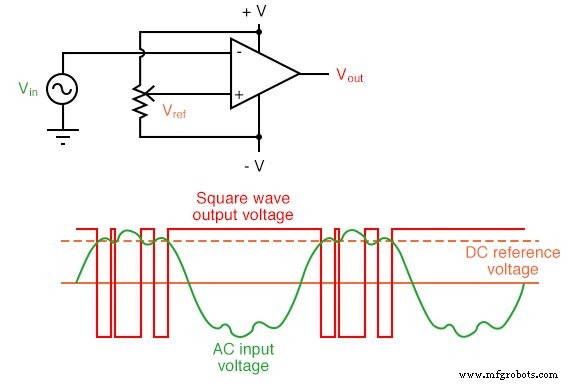

Als dit scenario u bekend voorkomt, komt dat omdat u zich een soortgelijk probleem herinnert met (analoge) spanningsvergelijker op-amp-circuits. Met een enkel drempelpunt waarop een ingang ervoor zorgt dat de uitgang schakelt tussen "hoge" en "lage" toestanden, zal de aanwezigheid van significante ruis onregelmatige veranderingen in de uitgang veroorzaken:

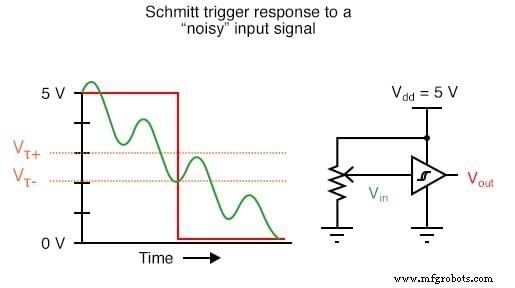

Schmittt-trigger

De oplossing voor dit probleem is een beetje positief feedback geïntroduceerd in het versterkercircuit. Bij een op-amp wordt dit gedaan door de uitgang via een weerstand weer aan te sluiten op de niet-inverterende (+) ingang.

In een poortcircuit houdt dit in dat de interne poortschakelingen opnieuw moeten worden ontworpen, waarbij de feedback binnen het poortpakket tot stand wordt gebracht in plaats van via externe verbindingen. Een zo ontworpen poort wordt een Schmitt-trigger genoemd . Schmitt-triggers interpreteren variërende ingangsspanningen volgens twee drempelspanningen:a positief gaand drempel (VT+), en een negatief-gaand drempel (VT-):

Hysterese in Schmitt-triggerpoorten

Schmitt-triggerpoorten worden in schematische diagrammen onderscheiden door het kleine "hysterese" -symbool dat erin is getekend, dat doet denken aan de B-H-curve voor een ferromagnetisch materiaal. Hysterese veroorzaakt door positieve feedback binnen de poortschakelingen voegt een extra niveau van ruisimmuniteit toe aan de prestaties van de poort.

Schmitt-triggerpoorten worden vaak gebruikt in toepassingen waar ruis wordt verwacht op de ingangssignaallijn(en) en/of waar een onregelmatige uitgang zeer nadelig zou zijn voor de systeemprestaties.

TTL- en CMOS-technologieën gebruiken in hetzelfde systeem

De verschillende spanningsniveau-eisen van TTL- en CMOS-technologie leveren problemen op wanneer de twee typen poorten in hetzelfde systeem worden gebruikt. Hoewel het geen probleem is om CMOS-poorten te gebruiken op dezelfde voedingsspanning van 5,00 volt die de TTL-poorten nodig hebben, zijn de TTL-uitgangsspanningsniveaus niet compatibel met de CMOS-ingangsspanningsvereisten.

Voorbeeld TTL- en CMOS-combinatiecircuit

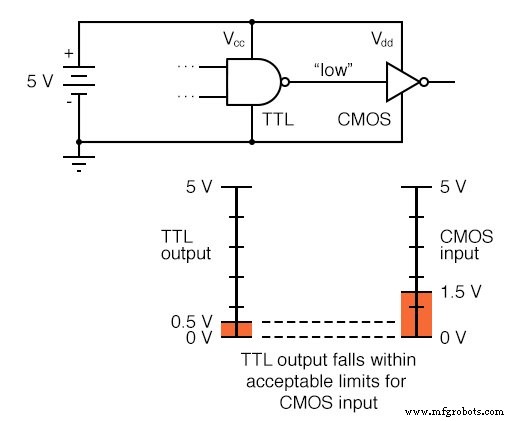

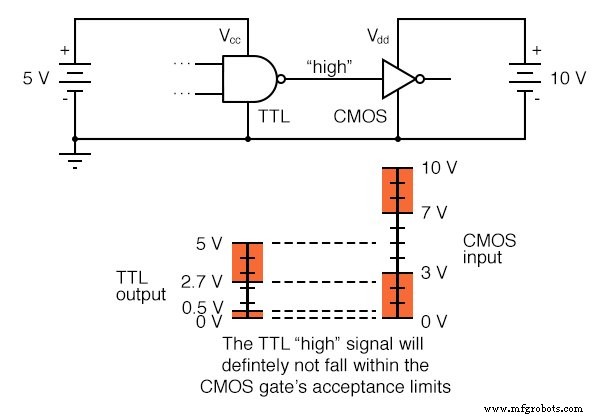

Neem bijvoorbeeld een TTL NAND-poort die een signaal afgeeft aan de ingang van een CMOS-inverterpoort. Beide poorten worden gevoed door dezelfde voeding van 5,00 volt (Vcc ). Als de TTL-poort een "laag" signaal afgeeft (gegarandeerd tussen 0 volt en 0,5 volt), wordt dit correct geïnterpreteerd door de ingang van de CMOS-poort als een "laag" (verwacht een spanning tussen 0 volt en 1,5 volt):

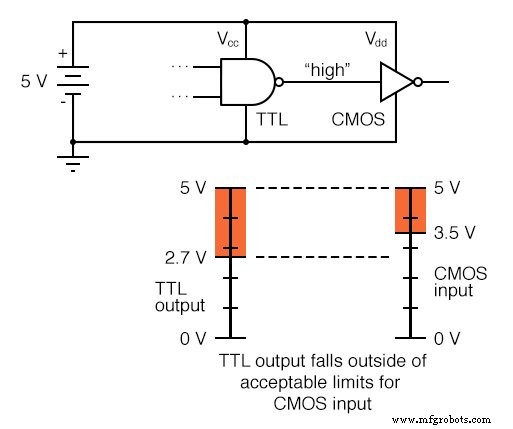

Als de TTL-poort echter een "hoog" signaal afgeeft (gegarandeerd tussen 5 volt en 2,7 volt), mogelijk niet correct worden geïnterpreteerd door de ingang van de CMOS-poort als een "hoog" (verwacht een spanning tussen 5 volt en 3,5 volt):

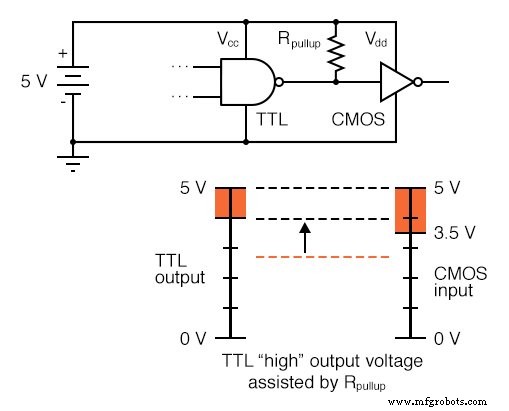

Gezien deze mismatch is het heel goed mogelijk dat de TTL-poort een geldig "hoog" signaal afgeeft (geldig, dat wil zeggen, volgens de normen voor TTL) dat binnen het "onzekere" bereik voor de CMOS-invoer ligt, en mogelijk is ( ten onrechte) geïnterpreteerd als een "laag" door de ontvangende poort. Een gemakkelijke "oplossing" voor dit probleem is om het "hoge" signaalspanningsniveau van de TTL-poort te vergroten door middel van een pullup-weerstand:

Er is echter iets meer nodig om een TTL-uitgang te koppelen aan een CMOS-ingang, als de ontvangende CMOS-poort wordt gevoed door een grotere voedingsspanning:

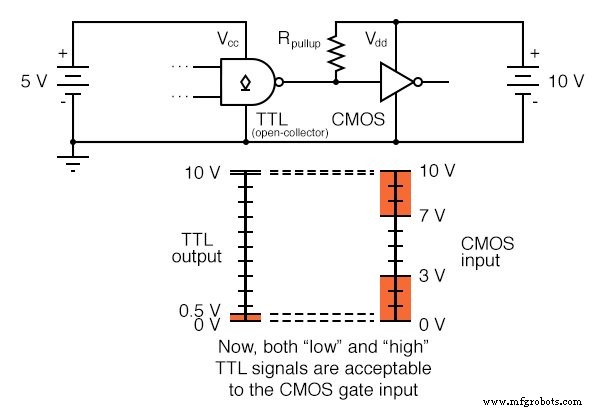

Een Open-Collector TTL-poort gebruiken met een CMOS-poort

Er zal geen probleem zijn met de CMOS-poort die de "lage" uitvoer van de TTL-poort interpreteert, natuurlijk, maar een "hoog" signaal van de TTL-poort is een andere zaak. Het gegarandeerde uitgangsspanningsbereik van 2,7 volt tot 5 volt van de TTL-poortuitgang is lang niet in de buurt van het acceptabele bereik van de CMOS-poort van 7 volt tot 10 volt voor een "hoog" signaal.

Als we een open-collector . gebruiken TTL-poort in plaats van een totempaaluitgangspoort, echter een pullup-weerstand naar de 10 volt Vdd voedingsrail zal de "hoge" uitgangsspanning van de TTL-poort verhogen tot de volledige voedingsspanning die de CMOS-poort voedt. Aangezien een open-collectorpoort alleen stroom kan zinken, geen bronstroom, wordt het "hoge" spanningsniveau volledig bepaald door de voeding waaraan de pullup-weerstand is bevestigd, waardoor het probleem van de mismatch netjes wordt opgelost:

Problemen bij het gebruik van CMOS-uitvoer naar een TTL-invoer

Vanwege de uitstekende uitgangsspanningskarakteristieken van CMOS-poorten, is het meestal geen probleem om een CMOS-uitgang op een TTL-ingang aan te sluiten. Het enige belangrijke probleem is de huidige belasting die wordt gepresenteerd door de TTL-ingangen, aangezien de CMOS-uitgang de stroom moet laten dalen voor elk van de TTL-ingangen in de "lage" toestand.

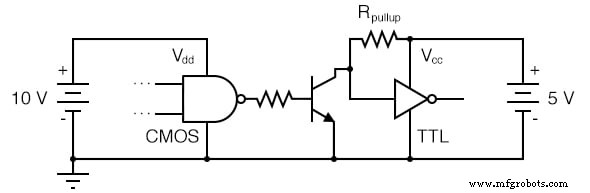

Wanneer de betreffende CMOS-poort wordt gevoed door een spanningsbron van meer dan 5 volt (Vcc ), zal er echter een probleem optreden. De "hoge" uitgangsstatus van de CMOS-poort, die groter is dan 5 volt, zal de aanvaardbare ingangslimieten van de TTL-poort voor een "hoog" signaal overschrijden.

Open-collector-omvormercircuit gebruiken

Een oplossing voor dit probleem is het creëren van een "open-collector" invertercircuit met behulp van een discrete NPN-transistor, en deze gebruiken om de twee poorten aan elkaar te koppelen:

De "Rpullup ”-weerstand is optioneel, aangezien TTL-ingangen automatisch een “hoge” toestand aannemen wanneer ze zwevend worden gelaten, wat zal gebeuren wanneer de CMOS-poortuitgang “laag” is en de transistor afsnijdt. Een zeer belangrijk gevolg van het implementeren van deze oplossing is natuurlijk de logische inversie die door de transistor wordt gecreëerd:wanneer de CMOS-poort een "laag" signaal afgeeft, ziet de TTL-poort een "hoge" ingang; en wanneer de CMOS-poort een "hoog" signaal afgeeft, verzadigt de transistor en ziet de TTL-poort een "lage" ingang. Zolang er rekening wordt gehouden met deze inversie in het logische schema van het systeem, komt alles goed.

GERELATEERD WERKBLAD:

-

Werkblad digitale logische signalen

Industriële technologie