De optimalisatie van spacer-engineering voor condensatorloze DRAM op basis van de Dual-Gate Tunneling Transistor

Abstract

De DRAM op basis van de dual-gate tunneling FET (DGTFET) heeft de voordelen van een condensatorloze structuur en een hoge retentietijd. In dit artikel wordt de optimalisatie van spacer-engineering voor DGTFET DRAM systematisch onderzocht door de Silvaco-Atlas-tool om de prestaties verder te verbeteren, inclusief de vermindering van de leesstroom "0" en verlenging van de retentietijd. De simulatieresultaten laten zien dat afstandhouders aan de bron- en afvoerzijde respectievelijk de lage-k- en hoge-k-diëlektrica moeten toepassen, wat de leesstroom "1" kan verbeteren en de leesstroom "0" kan verminderen. Door deze geoptimaliseerde spacer-techniek toe te passen, verkrijgt de DGTFET DRAM de optimale prestatie - extreem lage leesstroom "0" (10 −14 A/μm) en een grote retentietijd (10s), waardoor het statische stroomverbruik en de dynamische verversingssnelheid afnemen. En de lage waarde "0" stroom verbetert ook de stroomverhouding (10 7 ) van het lezen van "1" tot het lezen van "0". Bovendien onthult de analyse over schaalbaarheid de inherente tekortkoming, die de verdere onderzoeksrichting voor DGTFET DRAM biedt.

Achtergrond

Met de inkrimping van de apparaatgeometrie heeft de 1 transistor (1T)-1 condensator (1C) dynamisch willekeurig toegankelijk geheugen (DRAM) moeilijkheden ondervonden bij het verkleinen, omdat het moeilijk is voor de condensator om zijn grootte te verkleinen [1,2,3] . De geheugenindustrie heeft enkele effectieve methoden voorgesteld voor het verpakken van geheugen met een hogere dichtheid, zoals nieuwe materialen en nieuwe apparaatstructuren [4, 5]. De 1T DRAM met de condensatorloze structuur werd voor het eerst gerapporteerd in de vroege jaren 90 [6, 7], en het trekt steeds meer aandacht. In 1T DRAM wordt de toestand 1 (carrier-opslag) op vier manieren bereikt:impactionisatie [8], bipolaire junctietransistor [9], band-to-band tunneling (BTBT) [10] en gate-tunneling [11].

De tunneling-veldeffecttransistor (TFET) op basis van de BTBT wordt beschouwd als een potentieel alternatief voor MOSFET vanwege de hogere schakelverhouding en extreem lage stroomuitval [12,13,14]. De voordelen van TFET - lage stroom buiten de staat en zwakke temperatuurafhankelijkheid - zijn buitengewoon gunstig voor DRAM. Vooral de lage stroom in de off-state kan de leesstroom "0" en het statische stroomverbruik verminderen. Op dit moment zijn er enkele groepen die werken aan het onderzoek naar TFET DRAM [15,16,17,18,19,20]. Het is gemeld dat TFET DRAM de lage leesstroom "0" en een hoge retentietijd (RT) heeft. Van deze TFET DRAM's is de dual-gate TFET (DGTFET) DRAM het meest prominent [19, 20]. In DGTFET DRAM zijn zowel de schrijf- als leesbewerkingen gebaseerd op de BTBT. Onderzoek toont aan dat de leesstroom "0" van DGTFET DRAM kan oplopen tot 1 nA/μm, wat veel minder is dan die van traditionele 1T1C DRAM. En de RT van 2 s is veel beter dan de doelwaarde van 64 ms, die gewoonlijk is ingesteld op dynamische verversingstijd in het computersysteem [21]. De RT van DGTFET DRAM is nog steeds groter dan 300 ms wanneer de temperatuur wordt verhoogd tot 85 ° C, wat de uitvoerbaarheid in de zware omstandigheden toelaat. Bovendien vertoont de eliminatie van condensatoren met grotere afmetingen in DGTFET DRAM ook zijn concurrentievermogen in verpakkingen met een hoge dichtheid. Deze voordelen geven volledig aan dat het noodzakelijk is om DGTFET DRAM te bestuderen. Hoewel deze onderzoeken hebben aangetoond dat DGTFET superieure prestaties heeft dan conventionele 1T1C DRAM, zijn de resultaten (RT en aflezing "0" stroom) niet optimaal vanwege het feit dat de apparaatconfiguratie van DGTFET niet is geoptimaliseerd.

In dit artikel wordt de spacer-engineering van DGTFET geoptimaliseerd om DGTFET optimale prestaties te laten leveren. In TFET's hebben de spacer-diëlektrica de sterke invloed op BTBT [22, 23]. In DGTFET zijn de afstandhouders aan de bron- en afvoerzijde gesloten voor tunnelovergangen, dus ze hebben een grote invloed op de prestaties van DGTFET DRAM. Dit artikel analyseert systematisch de invloeden van spacer-diëlektricum (low-k of high-k diëlektrica) in elke spacer op DGTFET DRAM en stelt een geoptimaliseerde spacer-engineering voor. Door de optimalisatie van spacer-engineering wordt de leesstroom "0" verlaagd tot 10 −14 A/μm en RT kunnen oplopen tot 10 s. Ten slotte wordt in dit werk ook de schaalbaarheid van DGTFET DRAM met de geoptimaliseerde spacer-engineering besproken.

Apparaatstructuur en simulatiemethode

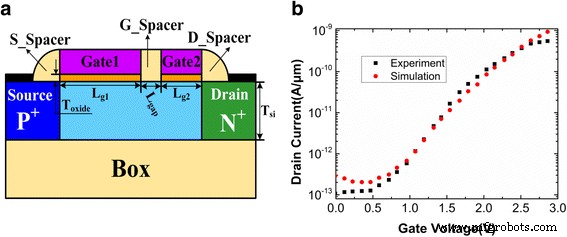

De DGTFET met een P-I-N-configuratie wordt geïllustreerd in figuur 1a. De source- en drainregio's zijn P + doping (10 20 /cm 3 ) en N + doping (10 20 /cm 3 ), respectievelijk. Het intrinsieke kanaalgebied is verdeeld in twee delen:Gate1-gebied met de N + polysilicium en Gate2-regio met de P + polysilicium. Er is een korte opening tussen de Gate1 en Gate2. De P + polysilicium Gate2 kan de fysieke bron voor ladingopslag creëren en onderhouden en de conventionele op TFET gebaseerde DRAM vervangen die gebruikmaakt van een P + zakgebied als opslagruimte. Terwijl voor een N + polysilicium Gate1, de gatenconcentratie in het onderlappingsgebied tussen Gate1 en Gate2 is laag, wat handig is voor de leesbewerking. Dus een P + polysilicium Gate2 is gekozen om een dieper opslaggebied te creëren dat een langere bewaartijd zou kunnen vergemakkelijken, terwijl een N + polysilicium Gate1 is geselecteerd om het tunnelmechanisme te besturen tijdens het lezen [20]. In figuur la verwijzen de S_Spacer en D_Spacer naar de afstandhouders aan respectievelijk de bron- en afvoerzijde. De G_spacer verwijst naar de spacer tussen de Gate1 en Gate2. Het standaardmateriaal van de afstandhouders is SiO2 . De standaard apparaatparameters zijn als volgt:dikte van de siliciumfilm (Tsi ) is 20 nm, lengte van de Gate1 (Lg1 ) is 400 nm, lengte van de Gate2 (Lg2 ) is 200 nm, lengte van de poortopening (Lopening ) is 50 nm, en de dikte van het Gate-oxide HfO2 (Toxide ) is 3 nm.

een Schema van dual-gate TFET (DGTFET) DRAM-cel. b Vergelijking tussen gesimuleerde overdrachtskarakteristiek met experimentele resultaten voor SOI TFET [25]

De simulaties van de DGTFET DRAM worden uitgevoerd in Silvaco Atlas met behulp van een niet-lokaal BTBT-model. Het niet-lokale BTBT-tunnelmodel houdt rekening met de ruimtelijke variatie van de energiebanden en de opwekking/recombinatie van het tegenovergestelde dragertype [24]. De parameters van het tunnelmodel zijn gekalibreerd volgens de experimentele resultaten van SOI TFET [25]. De massa van de elektronen- en gatentunnel is aangepast tot 0,22 m0 en 0,52m0 , respectievelijk, waarbij m0 is de rustmassa van het elektron. De gesimuleerde overdrachtskarakteristiek van SOI TFET is consistent met experimentele resultaten, zoals weergegeven in figuur 1b, die de in dit artikel toegepaste modellen autoriseert. Vanwege de zware doping in source- en drainregio's wordt ook rekening gehouden met het bandgap-verkleiningsmodel en Fermi-Dirac-statistieken. Verder worden ook de Shockley-Read-Hall-recombinatie en doping- en elektrisch-veldafhankelijke mobiliteitsmodellen toegepast. Alle modelparameters komen overeen met die in [19, 20]. Omdat de levensduur van de drager de generatie/recombinatie van de drager tijdens het vasthouden bepaalt, beïnvloedt het de RT van DGTFTET DRAM. Volgens de verschillende levensduur van de drager, variërend tussen 1 s en 10 ns in [26,27,28], zijn de elektron- en gatlevensduur ingesteld op 100 ns. Scharfetter-relatie- en Schenk-modellen worden gebruikt om respectievelijk doping en temperatuurafhankelijkheid van de levensduur op te nemen.

Resultaten en discussie

Bedieningsmechanisme

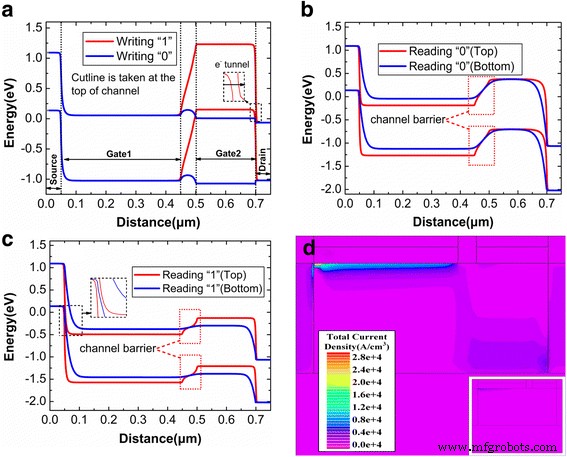

In DGTFET DRAM worden de schrijf- en leesbewerkingen bestuurd door BTBT op respectievelijk de afvoer- en brontunneling-juncties. Afbeelding 2 toont de energiebanden tijdens de verschillende bewerkingen. Zoals getoond in Fig. 2a, plaatst de Gate2 met een negatieve bias tijdens het schrijven van "1" de energieband van het kanaal onder Gate2 aanzienlijk, zodat een extreem kleine tunnelbarrière wordt gecreëerd aan de afvoerzijde. De elektronen tunnelen dus naar de afvoerzijde en de gaten worden verzameld in de diepe potentiaalput (1,2 V), zoals weergegeven in figuur 3a. Tijdens het schrijven van "0" zorgt de Gate2 met een positieve bias ervoor dat de gaten uit deze potentiaalput verdrijven en opnieuw worden gecombineerd aan de afvoerzijde [29]. Figuur 2b, c toont de energiebanden na respectievelijk het lezen van "1" en "0". Figuur 2b illustreert dat er een kanaalbarrière is tussen de Gate1 en Gate2, maar deze bestaat niet aan de onderkant van het kanaal. Bovendien is de tunnelafstand aan de bronzijde kleiner aan de bovenkant van het kanaal. Dit toont aan dat een hellend geleidingspad (van frontinterface voor Gate1 naar achterinterface voor Gate2) wordt gevormd tijdens het lezen "1", wat ook kan worden aangetoond door de stroomdichtheid van figuur 2d. Tijdens de uitlezing "0" is de voor de hand liggende kanaalbarrière te vinden in Fig. 2c, die de leesstroom "0" beperkt. De inzet van figuur 2d laat zien dat elektronen die vanuit het brongebied tunnelen, deze kanaalbarrière niet kunnen passeren om de stroom met hogere aflezing "0" te vormen.

Energiebanden van bron tot afvoer. een Energiebanden na het schrijven van "1" met negatieve Gate2-bias en na het schrijven van "0" met positieve Gate2-bias. b Energiebanden aan de boven- en onderkant van het kanaal na het lezen van "1". c Energiebanden aan de boven- en onderkant van het kanaal na het lezen van "0". d Totale stroomdichtheid na het lezen van "1"

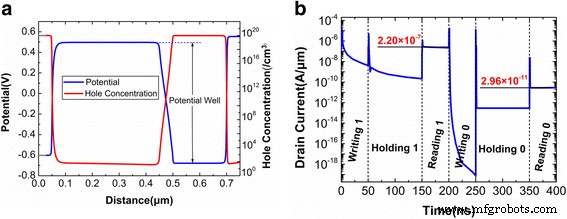

een Potentiële en gatenconcentratie op het oppervlak van het kanaal na het schrijven van "1". b Tijdelijke respons van afvoerstroom voor DGTFET DRAM gebruikt in tabel 1

Een goede programmeerconditie is belangrijk voor DGTFET DRAM. Bij Gate2 moet een grotere negatieve bias worden toegepast, zodat de verzadigde BTBT wordt geïnduceerd tijdens het schrijven van "1". Tijdens het vasthouden van "1" wordt een kleine negatieve bias toegepast bij Gate2 om gaten in de potentiaalbron lange tijd vast te houden. Voor leesbewerkingen versterkt de hogere Gate1-bias de BTBT tijdens het lezen van "1", maar wat nadelig is voor het lezen van "0" -stroom. De Gate2 met de juiste bias kan niet alleen de leesstroom "1" verbeteren, maar kan ook de leesstroom "0" verzwakken. Door de geoptimaliseerde programmeerconditie in tabel 1 toe te passen, wordt de tijdelijke respons van DGTFET DRAM met de standaardparameters getoond in figuur 3b. De schrijf- en lees- en houdtijden zijn respectievelijk ingesteld op 50 ns en 100 ns. De verkregen stroomverhouding van het lezen van "1" tot het lezen van "0" is ongeveer 10 4 , wat hetzelfde is als die in [17, 19, 20].

Impact van spacer-diëlektrica

In DGTFET DRAM zal het gebruik van low-k of high-k diëlektrica in drie spacers (S_Spacer, G_Spacer en D_Spacer) de prestaties beïnvloeden. In dit ontwerp kiezen de low-k en high-k diëlektrica voor de SiO2 en HfO2 , respectievelijk. Als elke spacer SiO2 . gebruikt of HfO2 , zullen er in totaal acht combinaties van spacer-engineering zijn. Voor een uitgebreidere analyse, de prestatie-eigenschappen van DGTFET DRAM met elke combinatie, inclusief het lezen van "1" (I 1 ) en “0” (I 0 ) stromen en stroomverhouding (I 1 / Ik 0 ), worden geëxtraheerd uit de tijdelijke reacties, zoals weergegeven in tabel 2. Om de RT te beoordelen, worden deze parameters ook geëxtraheerd wanneer de houdtijd wordt verhoogd tot 2 s, wat in de volgende secties zal worden besproken. In tabel 2 vertegenwoordigen de letters "S" en "H" SiO2 en HfO2 , en drie letters van elke afkorting vertegenwoordigen respectievelijk S_Spacer, G_Spacer en D_Spacer.

Uit tabel 2 kan de optimale spacer-engineering worden gekozen. De ik 1 zijn ongeveer 10 −7 A/μm en 10 −9 A/μm wanneer de SiO2 en HfO2 worden respectievelijk gebruikt in S_Spacer. Wanneer de D_Spacer de HfO2 . toepast , de ik 0 is laag tot ongeveer 10 −14 A/μm. Daarom is de optimale spacerconfiguratie van DGTFET DRAM dat diëlektrica met lage k en hoge k moeten worden gebruikt aan de bron- en afvoerzijde. De specifieke redenen zullen in de volgende paragrafen systematisch worden geanalyseerd.

Invloeden van S_Spacer-diëlektricum

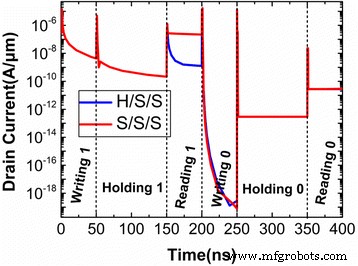

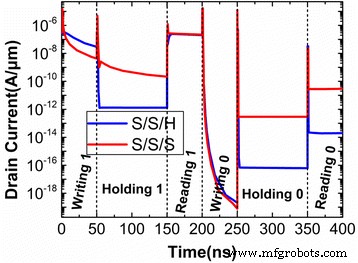

Om de invloeden van S_Spacer te analyseren, worden de tijdelijke reacties van afvoerstromen voor H/S/S en S/S/S vergeleken in Fig. 4. Het kan worden waargenomen dat de aflezing "1" stroom met ongeveer twee is verbeterd ordes van grootte wanneer de SiO2 wordt gekozen als het S_Spacer-diëlektricum.

Tijdelijke reacties van afvoerstromen voor H/S/S en S/S/S uitgevoerd in tabel 1

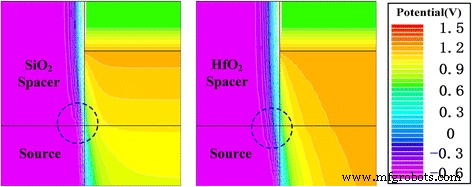

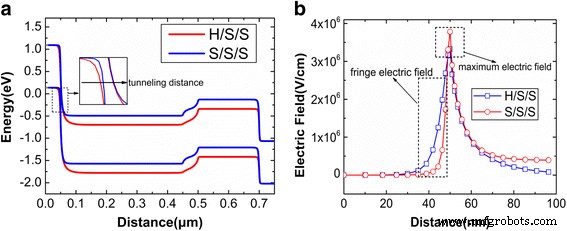

Figuur 5 toont de potentiële contouren van S/S/S en H/S/S. Bij de brontunnelovergang is het oppervlaktedepletiegebied van H/S/S duidelijk verlengd in vergelijking met dat van S/S/S, zoals getoond in de cirkel in Fig. 5. Het uitgebreide oppervlaktedepletiegebied vergroot de tunnelingbarrièrebreedte. Afbeelding 6a toont de energiebanden na het lezen van "1". Zoals te zien is in het lokale vergrote gebied van deze figuur, is de tunnelafstand (zie de pijlen) van H/S/S duidelijk groter dan die van de S/S/S, wat wordt veroorzaakt door het uitgebreide oppervlaktedepletiegebied. Bovendien, na het lezen van "1", wordt het elektrische veld bovenaan de brontunnelverbinding weergegeven in Fig. 6b. Er kan worden vastgesteld dat het elektrische randveld van H/S/S groter is dan dat van S/S/S, wat de belangrijkste reden is voor de uitbreiding van het oppervlaktedepletiegebied. Kortom, S_Spacer met hoge k (HfO2 ) diëlektricum genereert het grotere elektrische randveld zodat het oppervlaktedepletiegebied bij de brontunnelingovergang wordt verlengd, wat de tunnelafstand van elektronen vergroot en de leesstroom "1" verlaagt. Verder blijkt uit figuur 6b dat het maximale elektrische veld van S/S/S groter is dan dat van H/S/S. De exponentiële relatie tussen BTBT-snelheid en elektrisch veld maakt de tunnelstroom van S/S/S veel groter dan die van H/S/S [30]. Daarom is de S_Spacer met het low-k diëlektricum (SiO2 ) is gunstig voor de aflezing "1" stroom.

Potentiële contouren van de S/S/S (links) en H/S/S (rechts) na het lezen van "1"

een Energieband van bron tot afvoer en b elektrisch veld aan de bovenkant van de brontunneling junction

In figuur 6a brengt het S_Spacer-diëlektricum ook de impact op de energieband van het kanaalgebied. In figuur 6b is het elektrische veld van S/S/S groter in het kanaalgebied, dus het kanaalpotentiaal is kleiner dan dat van H/S/S. Als gevolg hiervan is het hogere energieniveau te vinden in S/S/S. Maar dit kan geen effecten hebben op de tunnelbarrière en het lezen van "1" stroom.

Invloeden van D_Spacer-diëlektricum

Vervolgens wordt in dit artikel ook de D_Spacer onderzocht. De constante S_Spacer en G_Spacer behouden (SiO2 wordt gebruikt in deze twee Spacers), worden de verschillende transiënte afvoerstromen veroorzaakt door de verschillende D_Spacer-diëlektrica geïllustreerd in Fig. 7. Afgezien van het lezen van "1" en schrijven van "0", zijn de andere bewerkingen duidelijk afhankelijk van D_Spacer-diëlektricum. Dit komt omdat die D_Spacer ver verwijderd is van het geleidingspad "1" (onderkant van het kanaal onder de Gate2). Uit het vorige bedieningsmechanisme kan worden geleerd dat schrijf- en vasthoudbewerkingen worden geregeld door Gate2, dus het D_Spacer-diëlektricum kan deze twee bewerkingen beïnvloeden.

Tijdelijke reacties van afvoerstromen voor S/S/H en S/S/S uitgevoerd in tabel 1

Tijdens het vasthouden worden de gaten die zijn verzameld tijdens het schrijven van "1" uit de potentiaalput verwijderd en opnieuw gecombineerd aan de afvoerzijde. Dus de houdstroom "1" komt voornamelijk van de SRH-recombinatiestroom. Vanwege de sterkere beheersbaarheid van Gate2 over het kanaal in S/S/S, heeft S/S/S de grotere recombinatiesnelheid en houdt "1" stroom vast. Maar het is veel minder dan de BTBT-stroom tijdens het lezen van "1", dus de hogere houdstroom "1" kan niet worden weerspiegeld in het lezen van "1" stroom.

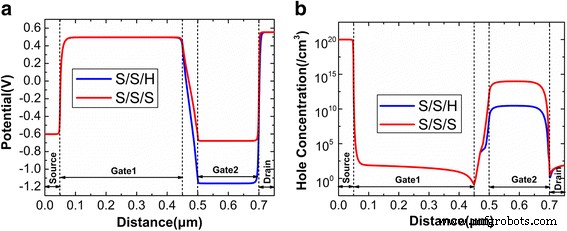

Tijdens het schrijven van "1" beïnvloedt het D_Spacer-diëlektricum de potentiaalputdiepte aanzienlijk. De potentiaalcontour in Fig. 8a laat zien dat D_Spacer met HfO2 diëlektricum creëert een diepere potentiaalbron. Het houdt in dat de effectieve BTBT tussen de afvoer en het kanaal wordt uitgebreid tot in het diepere kanaalgebied. Daarom is de schrijfstroom "1" van S/S/H hoger dan die van S/S/S. Tijdens het vasthouden van "0", hoewel een kleine negatieve bias (-0,2 V) wordt toegepast bij Gate2, kan het ook de energieband van het kanaal onder Gate2 opzetten, wat de BTBT aan de afvoerzijde induceert. Door de vorige analyse kan worden geleerd dat D_Spacer met SiO2 diëlektricum verbetert de BTBT bij de afvoertunnelverbinding tijdens het vasthouden van "0", wat kan worden aangetoond door de hogere gatenconcentratie voor S / S / S, zoals weergegeven in Fig. 8b. Daarom is de D_Spacer met SiO2 diëlektrische resultaten in de hogere houdstroom "0".

een Potentiële contour na het schrijven van "1". b Gatenconcentratie na vasthouden van “0”

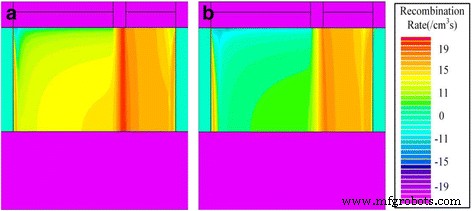

Tijdens het lezen van "0", omdat de kanaalbarrière tussen de Gate1 en Gate2 voorkomt dat de elektronen naar de afvoerzijde stromen, wordt het verschil bij het lezen van "0"-stroom voor S/S/H en S/S/S voornamelijk veroorzaakt door de recombinatiestroom . Hoe meer gaten er worden verzameld tijdens het vasthouden van "0" voor S/S/S, dus de dalende energieband maakt de recombinatiesnelheid van S/S/S groter dan die van S/H/S tijdens het lezen van "0", zoals weergegeven in Fig. 9. Als gevolg hiervan, wanneer de D_Spacer met SiO2 , moet de hogere leesstroom "0" worden toegeschreven aan de hogere recombinatiestroom, die wordt veroorzaakt door de meer geaccumuleerde gaten tijdens het vasthouden van "0".

Recombinatiesnelheid van a S/S/S en b S/S/H na het lezen van "0"

Samenvattend, de optimale spacer-engineering voor DGTFET DRAM is dat de spacers aan de bron- en afvoerzijde respectievelijk de low-k en high-k diëlektrica moeten toepassen. Uit Tabel 2 blijkt dat G_Spacer geen invloed heeft op DGTFET DRAM wanneer de andere afstandhouders ongewijzigd blijven. Dit komt omdat BTBT's die de schrijf- en leesbewerkingen domineren, vrij zijn van de invloed van G_Spacer.

Bewaartijd

Zoals eerder is uitgelegd, verslechteren de recombinatie en generatie van het gat tijdens het vasthouden van "1" en "0" respectievelijk de toestand "1" en "0". Dientengevolge is het noodzakelijk om de prestatievermindering van DGTFET DRAM bij een langere bewaartijd te bestuderen. In Tabel 2, de I 1 en ik 0 sterk achteruitgaan met het toenemen van de houdtijd. Op alle apparaten, I 1 /Ik 0 is nog steeds groter dan 10 4 voor apparaat met optimale spacer-engineering (S/S/H en S/H/H) wanneer de houdtijd stijgt tot 2 s.

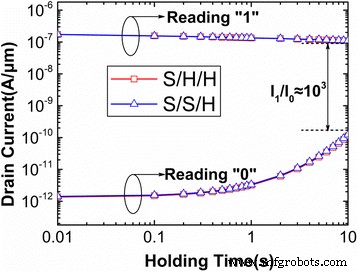

Over het algemeen is de houdtijd die nodig is om de maximale waarnemingsmarge te verkleinen (verschil tussen I 1 en ik 0 ) met 50% wordt beoordeeld als RT. In dit ontwerp wordt een striktere RT gedefinieerd als de maximale houdtijd wanneer de I 1 /Ik 0 is hoger dan 10 3 . Afbeelding 10 toont de variatie van de leesstroom met de houdtijd voor S/S/H en S/H/H. Er kan worden vastgesteld dat de stroomverhouding van S/H/S en S/H/H zo hoog is als 10 3 wanneer de houdtijd oploopt tot 10 s. Als gevolg hiervan kan de RT van DGTFET DRAM met optimale spacer-engineering oplopen tot 10 s. Dit is veel hoger dan de doelwaarde van 64 ms. Tabel 3 vergelijkt de prestatie-eigenschappen in dit werk met die in [17,18,19,20]. In [19, 20] is de huidige verhouding slechts 10 2 , en de RT is veel kleiner dan 10 s. Bovendien is de aflezing "0" stroom in dit werk twee ordes van grootte lager dan die in [19, 20]. De experimentresultaten over FD-SOI TFET DRAM laten ook zien dat hun aflezing "0" stroom en RT inferieur zijn dan die in dit werk. Deze superieure prestatie toont aan dat DGTFET een vervanging is voor DRAM met laag vermogen. De optimalisatie van spacer-engineering zorgt ervoor dat de DGTFET DRAM een lage "0"-stroom en een hoge RT verkrijgt, wat nuttig is voor de vermindering van het statische en dynamische stroomverbruik.

Variatie van de leesstroom met de houdtijd voor S/S/H en S/H/H

Schaalbaarheid van DGTFET DRAM

Hoewel de DGTFET DRAM het probleem van geheugenceldichtheid oplost vanwege de eliminatie van condensator met de grote omvang, is het noodzakelijk om de schaalbaarheid ervan te bestuderen. Het doel van schaalbaarheid is om de RT hoger te houden dan 2 s. Tabel 4 extraheert de prestatie-eigenschappen van S/S/H met de afname van L g1 , L g2 , en L kloof . In Tabel 4 vertegenwoordigen de drie cijfers van elke afkorting L g1 , L kloof , en L g2 .

Uit Tabel 4 kan worden afgeleid dat I 1 neemt extreem af wanneer de Lg1 reduceert tot 100 nm van 200 nm. De schaal van Lg1 voorbij 100 nm vernauwt de n-type-geïnduceerde barrière, wat resulteert in een verminderde beheersbaarheid van de poort en een verslechterd I 1 . De ik 0 neemt aanzienlijk toe met het afnemen van L g1 en L g2 . De reductie van L g2 verkleint de kanaalbarrièrebreedte tussen Gate1 en Gate2, waardoor een deel van de elektronen de barrière passeert om het hogere I te vormen 0 . Bovendien is het continu verkleinen van L g1 verzwakt het vermogen van Gate1 om de tunneling-elektronen op het oppervlak van het kanaal te beperken tijdens het lezen van "0". In Tabel 4 is de L kloof heeft geen duidelijke invloed op de I 1 , maar de ik 0 neemt licht toe met het afnemen van de L kloof . L . verkleinen kloof onder de 20 nm maakt een hogere tunneling naar Gate2 mogelijk, waardoor toestand "0" wordt verslechterd, waardoor de retentietijd wordt verkort.

Om ervoor te zorgen dat de I 1 /Ik 0 en bewaartijd zijn groter dan 10 2 en 2 s, respectievelijk de minimale L g1 , L g2 , en L kloof worden respectievelijk beschouwd als 200, 150 en 20 nm. Deze minimale apparaatgrootte is iets kleiner dan die in [17,18,19,20], zoals weergegeven in Tabel 3. De minimale grootte van DGTFET DRAM is echter nog steeds groter dan die van 20 nm/18 nm node 1T1C DRAM [31 ], wat de inherente tekortkoming is van DGTFET DRAM. Maar de voordelen van condensatorloos, laag vermogen en hoge RT kunnen niet worden genegeerd met behulp van optimalisatie van spacer-engineering. In de toekomst zal het verminderen van de omvang van DGTFET DRAM tot meer dan 100 nm de focus van ons werk zijn.

Conclusies

In dit artikel wordt de optimalisatie van spacer-engineering voor DGTFET DRAM bestudeerd door de Silvaco-Atlas-tool. De afstandhouders aan de bron- en afvoerzijde hebben de belangrijkste invloed op de prestaties van DGTFET DRAM. Het vergrote elektrische randveld door de source spacer met HfO2 zorgt ervoor dat het oppervlakte-uitputtingsgebied zich uitstrekt bij de brontunneling, waardoor de afleesstroom "1" afneemt. Wanneer de SiO2 diëlektricum wordt gebruikt in de afvoerafstandhouder, hoe sterker BTBT meer gaten induceert tijdens het vasthouden van "0", wat de recombinatiestroom verbetert tijdens het lezen van "0". Daarom is de optimale spacer-engineering dat lage-k- en high-k-diëlektrica moeten worden gebruikt in respectievelijk drain- en source-afstandhouders. Door de optimalisatie van spacer-engineering verkrijgt de DGTFET DRAM prominente voordelen:extreem lage leesstroom "0" en hogere retentietijd (10s) in vergelijking met andere gerelateerde werken. Bovendien blijkt uit de analyse over schaalbaarheid dat de minimale apparaatgrootte nog steeds groter is dan die in de laatste 20 nm/18 nm node 1T1C DRAM. Deze inherente tekortkoming geeft aan dat het in de toekomst verminderen van de omvang van DGTFET DRAM tot meer dan 100 nm de focus zal zijn van ons werk voor DGTFET DRAM.

Afkortingen

- DGTFET:

-

Dual-gate tunneling veldeffecttransistor

- DRAM:

-

Dynamisch willekeurig toegankelijk geheugen

Nanomaterialen

- De Unijunction Transistor (UJT)

- Op sensoren gebaseerde projectideeën voor laatstejaars ingenieursstudenten

- Reliability Engineering Principles for the Plant Engineer

- IBM-wetenschappers vinden een thermometer uit voor de nanoschaal

- De waarde van cloudgebaseerd slicen en bestandsbeheer voor 3D-printen

- Hoogreflecterende dunnefilmoptimalisatie voor micro-LED's met volledige hoek

- Het ontwerp van de emissielaag voor elektronenvermenigvuldigers

- Het beste niveau voor optimalisatie en organisatie in de Smart Factory

- Hoe u de op maat gemaakte technische oplossingen vindt die u zoekt

- Een gebrek aan diversiteit kan de oorzaak zijn van de groeiende vaardigheidskloof in de sector

- Bedankt voor de herinneringen!