Open source GPU bouwt voort op RISC-V

Een groep enthousiastelingen stelt een nieuwe set grafische instructies voor die zijn ontworpen voor 3D-graphics en mediaverwerking. Deze nieuwe instructies zijn gebaseerd op de RISC-V-basisvectorinstructieset. Ze zullen ondersteuning toevoegen voor nieuwe gegevenstypen die specifiek zijn voor grafische afbeeldingen als gelaagde extensies in de geest van de kern-RISC-V-instructieset-architectuur (ISA). Vectoren, transcendentale wiskunde, pixel en texturen en Z/Frame-bufferbewerkingen worden ondersteund. Het kan een gefuseerde CPU-GPU ISA zijn. De groep noemt het de RV64X omdat de instructies 64-bits lang zullen zijn (32-bits is niet genoeg om een robuuste ISA te ondersteunen).

Waarom nu?

De wereld heeft genoeg GPU's om uit te kiezen, waarom dit? Omdat, zegt de groep, commerciële GPU's minder effectief zijn in het voldoen aan ongebruikelijke behoeften, zoals dual-phase 3D frustum clipping, aanpasbare HPC (arbitrary bit depth FFT's), hardware SLAM. Ze zijn van mening dat samenwerking flexibele standaarden biedt, de inspanning van 10 tot 20 manjaar vermindert die anders nodig zou zijn, en zal helpen bij kruisverificatie om fouten te voorkomen.

Het team zegt dat hun motivatie en doelen worden gedreven door de wens om een klein, ruimtebesparend ontwerp te maken met aangepaste programmeerbaarheid en uitbreidbaarheid. Het moet low-cost IP-eigendom en ontwikkeling bieden, en niet concurreren met commerciële aanbiedingen. Het kan worden geïmplementeerd in FPGA- en ASIC-doelen en zal gratis en open source zijn. Het eerste ontwerp zal gericht zijn op microcontrollers met een laag vermogen. Het zal Khronos Vulkan-compatibel zijn en na verloop van tijd andere API's ondersteunen (OpenGL, DirectX en andere).

De laatste hardware zal een RISC-V-kern zijn met een GPU-functionele eenheid. Voor de programmeur zal het eruitzien als een enkel stuk hardware met 64-bit lange instructies gecodeerd als scalaire instructies. Het programmeermodel is een schijnbare SIMD, dat wil zeggen, de compiler genereert SIMD uit vooraf ingestelde scalaire opcodes. Het bevat variabele-issue, predicated SIMD-backend, vector front-end, precieze uitzonderingen, branch shadowing en veel meer. Er is geen behoefte aan een RPC/IPC-aanroepmechanisme om 3D API-aanroepen van/naar ongebruikte CPU-geheugenruimte naar GPU-geheugenruimte en vice versa te verzenden, aldus het team. En het zal beschikbaar zijn als 16-bits vast punt (ideaal voor FPGA's), evenals 32-bits drijvende komma (ASIC's of FPGA's).

Het ontwerp zal het Vblock-formaat gebruiken (van de Libre GPU-inspanning):

- Het is een beetje zoals VLIW (alleen niet echt)

- Een blok instructies wordt voorafgegaan door registertags die extra context geven aan scalaire instructies binnen het blok

- Subblokken omvatten:vectorlengte, swizzling, vector/breedte-overschrijvingen en voorspelling.

- Dit alles wordt toegevoegd aan scalaire opcodes

- Er zijn geen vector-opcodes (en ook niet nodig)

- In de vectorcontext gaat het als volgt:als een register wordt gebruikt door een scalaire opcode, en het register wordt vermeld in de vectorcontext, wordt de vectormodus geactiveerd

- Activering resulteert in een for-loop op hardwareniveau die meerdere aaneengesloten scalaire bewerkingen uitvoert (in plaats van slechts één).

- Implementers zijn vrij om de lus op elke gewenste manier te implementeren:SIMD, multi-issue, single-execution.

Het ontwerp maakt gebruik van scalairen (8-, 16-, 24- en 32-bits vast en floats), evenals transcendentalen (sincos, atan, pow, exp, log, rcp, rsq, sqrt, enz.). De vectoren (RV32-V) ondersteunen vectorbewerkingen met 2-4 elementen (8-, 16- of 32-bits/element), samen met gespecialiseerde instructies voor een algemene 3D-weergavepijplijn voor punten, pixels, texels (in wezen speciale vectoren). )

- XYZW-punten (64- en 128-bits vast en zwevend)

- RGBA-pixels (8-, 16-, 24- en 32-bits pixels)

- UVW texels (8-, 16-bits per component)

- Licht en materialen (Ia, ka, Id, kd, Is, ks...)

Matrices zijn 2 × 2, 3 × 3 en 4 × 4 matrices worden ondersteund als een native datatype samen met geheugenstructuren om ze te ondersteunen voor attribuutvectoren en zullen in wezen worden weergegeven in een 4 × 4 matrix.

Een van de voordelen van fused CPU-GPU ISA is de mogelijkheid om een standaard grafische pijplijn in microcode te implementeren, ondersteuning te bieden voor aangepaste shaders en ray-tracing-extensies te implementeren. Het ondersteunt ook vectoren voor numerieke simulaties met 8-bits integer-gegevenstypen voor AI en machine learning.

Aangepaste rasters kunnen worden geïmplementeerd, zoals splines, SubDiv-oppervlakken en patches.

Het ontwerp zal flexibel genoeg zijn om aangepaste pijplijnfasen, aangepaste geometrie-/pixel-/framebufferfasen, aangepaste tessellators en aangepaste instancieringsbewerkingen te implementeren.

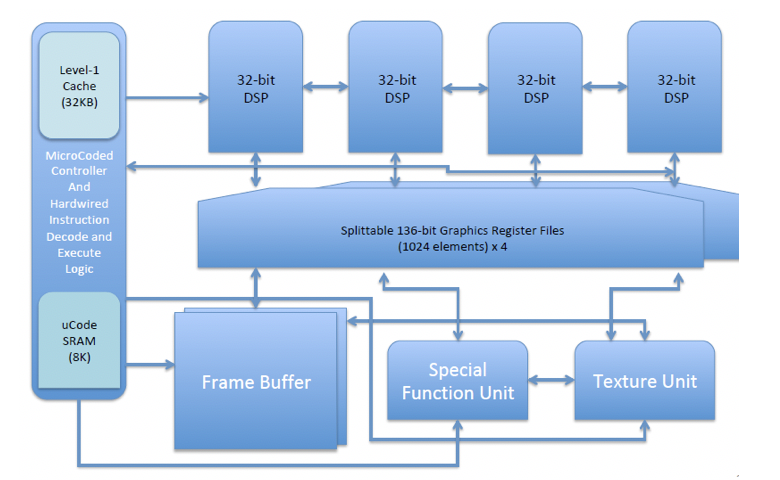

RV64X-blokdiagram

De RV64X referentie-implementatie omvat:

- Instructie/Data SRAM Cache (32KB)

- Microcode SRAM (8KB)

- Instructiedecoder met dubbele functie

- Bedraad met implementatie van RV32V en X

- Micro-gecodeerde instructiedecoder voor aangepaste ISA

- Quad Vector ALU (32 bits/ALU—vast/zwevend)

- 136-bits registerbestanden (1K elementen)

- Speciale functie-eenheid

- Textuureenheid

- Configureerbare lokale framebuffer

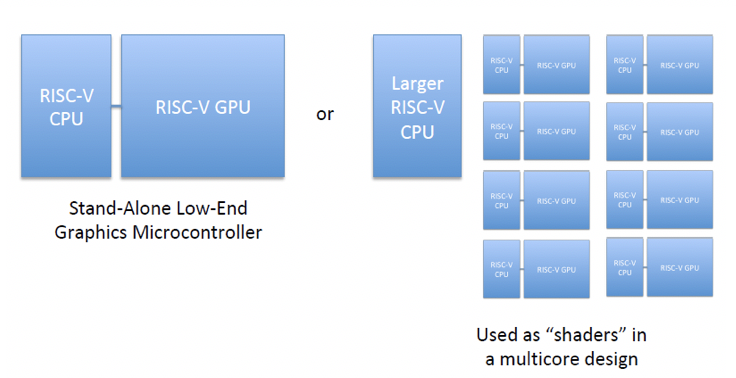

Het ontwerp is bedoeld om schaalbaar te zijn zoals hieronder aangegeven.

Het schaalbare ontwerp van de RV64X

Het RV64X-ontwerp heeft verschillende nieuwe ideeën, waaronder gefuseerde, verenigde CPU-GPU ISA, configureerbare registers voor aangepaste gegevenstypen en door de gebruiker gedefinieerde SRAM-gebaseerde microcode voor toepassingsgedefinieerde aangepaste hardware-uitbreidingen voor:

- Aangepaste rasterfasen

- Raytracing

- Machineleren

- Computervisie

Hetzelfde ontwerp dient zowel als een stand-alone grafische microcontroller of schaalbare shader-eenheid, en gegevensformaten ondersteunen FPGA-native of ASIC-implementaties.

Waarom is er behoefte aan open afbeeldingen?

De ontwikkelaars denken dat de meeste grafische processors het high-end dekken, zoals gaming, high-frequency trading, computer vision en machine learning. Ze geloven dat het ecosysteem geen schaalbare grafische kern heeft voor meer reguliere toepassingen voor zaken als kiosken, billboards, casinospellen, speelgoed, robotica, apparaten, wearables, industriële mens-machine-interfaces, infotainment en auto-meterclusters. Ondertussen moeten speciale programmeertalen worden gebruikt om GPU-kernen te programmeren voor OpenGL, OpenCL, CUDA, DirectCompute en DirectX.

Een grafische extensie voor RISC-V zou de schaalbaarheid en meertalige lasten wegnemen en een hoger niveau van use case-innovatie mogelijk maken.

Volgende stappen

Dit is een zeer vroege specificatie, nog in ontwikkeling en onderhevig aan verandering op basis van input van belanghebbenden en de industrie. Het team zal een discussieforum oprichten. Een onmiddellijk doel is het bouwen van een voorbeeldimplementatie met een instructiesetsimulator, een FPGA-implementatie die gebruikmaakt van open-source IP en aangepaste IP die is ontworpen als open-sourceproject. Demo's en benchmarks worden ontworpen. Ontwikkelaars die geïnteresseerd zijn om deel te nemen, moeten Atif Zafar contracteren.

Wat betreft de Libre-RISC 3D GPU, het doel van de organisatie is om een hybride CPU, VPU en GPU te ontwerpen. Het is niet, zoals algemeen gemeld, een "toegewijde exclusieve GPU". De mogelijkheid bestaat om een stand-alone GPU-product te maken. Hun primaire doel is om een complete alles-in-één processor-SoC te ontwerpen die toevallig een door Libre gelicentieerde VPU en GPU bevat.

Wat denken we?

Het aantal GPU-leveranciers neemt toe. We hebben er nu meer dan een dozijn.

AppleLibre-RISC-V 3D GPUQualcommAMDNvidiaRISC-V GraphicsArmIntelThink-SiliconDMPJingjia MicroVeriSilcionImagination TechnologiesEen applicatie die niet wordt vermeld als potentiële gebruiker van een gratis, flexibele, kleine GPU, omvat cryptovaluta en mining.

Als het het doel van de RISC-V-gemeenschap is om de IP-leveranciers zoals Arm en Imagination te evenaren, dan kunnen we DSP-, ISP- en DP-ontwerpen verwachten. Er is minimaal één Open DSP-voorstel; misschien kan het in de RISC-V-gemeenschap worden gebracht.

Het zal minstens twee jaar duren voordat er hardware-implementaties verschijnen. Een van de meest logische kandidaten om dit ontwerp te adopteren is Xilinx, dat nu Arm's Mali gebruikt in zijn Zynq-ontwerp. We verwachten ook dat er verschillende implementaties uit China komen.

>> Dit artikel is oorspronkelijk gepubliceerd op onze zustersite, EE Times.

Jon Peddie , een pionier in de grafische industrie, is president van Jon Peddie Research.

Jon Peddie , een pionier in de grafische industrie, is president van Jon Peddie Research. Abonneer u voor meer Embedded op de wekelijkse e-mailnieuwsbrief van Embedded.

Ingebed

- Inleiding tot open source-terminologie

- Open source en het internet der dingen:innovatie door samenwerking

- RISC-V Summit:hoogtepunten op de agenda

- Industriële IoT-beveiliging bouwt voort op hardware

- Een projectlogboek voor FirePick Delta, de Open Source MicroFactory

- AT&T, Tech Mahindra werken samen aan nieuw open source AI-platform

- Softwarerisico's:Open source beveiligen in IoT

- Open source IoT-ontwikkeltools versus door leveranciers ondersteunde tools

- MassRobotics publiceert 's werelds eerste' open source autonome mobiele robot interoperabiliteitsnormen

- De noodzaak van open source aan de rand (eBook)

- Open source stimuleert de acceptatie van IoT en Edge Computing