Inzicht in ADC-codefoutenpercentage

Omdat snelle analoog-naar-digitaal-omzetters (ADC's) in bemonsteringsfrequentie zijn toegenomen, is ook het probleem van codefouten - ook bekend als fonkelcodes - in de uitvoergegevens van de ADC toegenomen. Een codefout wordt gedefinieerd als een fout in de uitvoercode van een ADC die een gedefinieerde drempel overschrijdt. De drempel wordt meestal gedefinieerd als het niveau waarop een fout de verwachte amplitude van de ruis van de ADC overschrijdt, zodat de fout gemakkelijk kan worden geïdentificeerd in aanwezigheid van ruis.

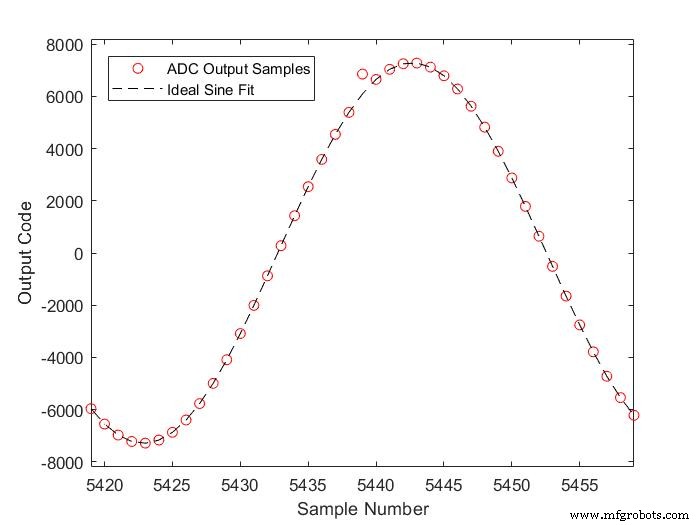

Een andere manier om deze definitie van de foutdrempel uit te leggen, is dat de foutamplitude optreedt met een waarschijnlijkheid die groter is dan de verwachte waarschijnlijkheid van die amplitude, gegeven de veronderstelde Gauss-gedistribueerde ruis van de ADC. Afb. 1 toont een voorbeeldcodefout gevonden in de uitvoervoorbeelden van een ADC. Het foutieve monster is duidelijk zichtbaar in vergelijking met de ideale sinusgolffit en overtreft ver de ruis van de andere monsters in de plot.

Afb. 1:Voorbeeld van een ADC-uitgang met een codefout.

Het codefoutpercentage (CER) van een ADC, ook wel woordfoutpercentage (WER) of metastabiliteitsfoutpercentage genoemd, wordt gedefinieerd als het gemiddelde aantal fouten per monster en wordt gemeten door het gemiddelde aantal monsters tussen opeenvolgende fouten te tellen. Het wordt meestal gedefinieerd als een orde van grootte, zoals 10 –12 fouten/monster. De gemiddelde tijd tussen fouten is daarom afhankelijk van de bemonsteringsfrequentie van de converter. De gemeten CER is alleen nauwkeurig wanneer de ADC werkt met de bemonsteringsfrequentie waarmee de CER werd gemeten. Over het algemeen kan het verlagen van de bemonsteringsfrequentie de CER met ordes van grootte verbeteren.

Laten we eens kijken waar codefouten vandaan komen om te zien waarom de bemonsteringsfrequentie een belangrijke factor is.

Wat laat een ADC schitteren?

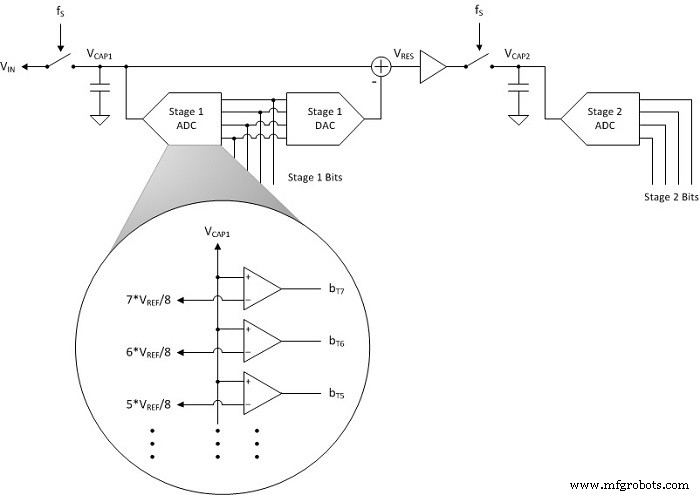

Een meerstaps ADC-architectuur, zoals een gepijplijnde flash-ADC of een SAR-ADC (opeenvolgend benaderingsregister), zet de bemonsterde spanning stapsgewijs om in digitale bits, en elke opeenvolgende fase vertrouwt op het resultaat van de vorige fase. Overweeg een eenvoudige, snelle ADC met pijplijnflits, zoals weergegeven in Afb. 2 . Deze vereenvoudigde ADC toont twee conversiefasen waarbij elke volgende fase een digitale code produceert die het ingangssignaal fijner schat.

De werking van de getoonde ADC is als volgt:

De eerste trap bemonstert de ingangsspanning en converteert het analoge ingangssignaal grof naar een digitale code met behulp van de eerste trap ADC. De flash-ADC in deze fase werkt door de bemonsterde spanning te vergelijken met statische spanningsreferenties, gegenereerd uit de hoofdreferentiespanning van de ADC (V REF ), met behulp van snelle vergelijkers. De uitvoer van de flitscomparators is een met een thermometer gecodeerd digitaal monster dat de ingangsspanning weergeeft.

De geconverteerde thermometercode wordt dan rechtstreeks naar de eerste-traps DAC gestuurd. Deze DAC voert de analoge spanning uit, die overeenkomt met het grof geconverteerde monster.

Aftrekken van de uitvoer van de eerste-traps DAC van de oorspronkelijke ingangsspanning resulteert in de kwantisatiefoutspanning of restspanning (V RES ). Het residu wordt vervolgens geamplificeerd en opnieuw bemonsterd (gepipelined) voor de tweede fase.

De tweede trap ADC kwantiseert V RES om een nauwkeurigere (hogere resolutie) schatting van de oorspronkelijke analoge ingangsspanning te verkrijgen.

Afb. 2:Voorbeeld van een gepijplijnd Flash ADC-architectuurblokdiagram.

De V RES creatieproces introduceert een snelle beslissingslus. Binnen één bemonsteringsklokperiode moet de bemonsterde spanning door de ADC van de eerste trap worden omgezet in een digitale code. De digitale code moet worden uitgevoerd vanaf de DAC van de eerste trap, afgetrokken van de oorspronkelijke ingangsspanning en opnieuw worden bemonsterd door de tweede trap. De snelle beslissingslus introduceert codefouten omdat de comparator in de flash-ADC een insteltijd heeft die een functie is van het verschil tussen de bemonsterde spanning en V REF .

Eenvoudiger, een comparator duurt langer om te regelen wanneer de ingangsspanning (V CAP1 ) dicht bij de referentiespanning ligt (zoals 7 * V REF /8) van de vergelijker. Theoretisch, als V CAP1 oneindig dicht bij de referentiespanning van de comparator ligt, zal de comparator nooit tot rust komen omdat hij in zijn lineaire gebied zal werken.

Ruis zal voorkomen dat dit daadwerkelijk gebeurt, maar als de comparator er te lang over doet om tot rust te komen, kan de DAC van de eerste trap de onjuiste digitale code gebruiken om de gekwantiseerde analoge spanning uit te voeren. Het resultaat is een V RES die niet overeenkomt met de daadwerkelijke digitale uitgangscode van de ADC van de eerste trap. De ADC van de tweede trap converteert vervolgens de verkeerde V RES , wat resulteert in een codefout.

Wat beïnvloedt CER?

U zou nu voldoende details moeten hebben om enkele conclusies te kunnen trekken over wat de CER beïnvloedt. De CER is duidelijk afhankelijk van de bemonsteringsfrequentie. Een snellere bemonsteringsfrequentie verkort de tijd waarin de beslissingslus een beslissing moet nemen. Minder tijd om een beslissing te nemen resulteert in een exponentiële toename van de kans dat de comparator niet op tijd tot rust is gekomen.

–Matt Guibord is een systeemingenieur in hogesnelheidsconverters bij Texas Instruments.

Ingebed